小伙伴們了解了 ESD的基本概念以及系統高效ESD設計(SEED)的必要性(告警!您的RF設備需要系統級ESD保護),這次Qorvo將為您介紹SEED工具箱中所有必要的部分,Let's go!

板載ESD保護器件

作為一個總體戰略,您可以在PC電路板上使用許多保護元件,以保護終端產品免受ESD事件的影響。這些保護元件包括:

無源和有源元件,如:

串聯電阻

去耦電容

鐵氧體磁珠

抑制裝置,如電磁干擾(EMI)/ESD濾波器

瞬態電壓抑制器(TVS)

TVS元件:

聚合物變阻器

陶瓷變阻器

火花隙s

硅二極管

然而,使用這些元件時應謹記以下幾點:

電阻、電容、電感-電容(LC)濾波器和鐵氧體磁珠在系統中衰減間接或二級ESD應力方面表現良好。一個有效的方法就是,需要將這些元件盡可能置于ESD應力對象(模塊引腳)附近。

您可以將串聯電阻與去耦電容(電阻-電容[RC]濾波器)或電壓箝位一起使用。

電容提供去耦性。選擇的電容最好具有高額定電壓、高共振頻率、低電阻和低電感。確保在連接電容時實現軌跡長度的最短化。

LC濾波器可阻隔瞬變電壓和EMI。

串聯鐵氧體磁珠可衰減電源線上的EMI和ESD。

變阻器可從高待機值變為極低導電值,從而吸收ESD能量,并限制ESD誘發性電壓。它們通常具有較高的觸發電壓(幾百伏)和高達100 V的箝位電壓,同時具有非常低的電容,但能夠在長時間的ESD應力之后顯示明顯的漏電流。

根據待保護的接口類型,硅基TVS二極管也可以具有較低的電容和比其他TVS元件更低的動態電阻值。它們具有較高的ESD吸附能力(即一旦ESD觸電被吸附,保護裝置就會非常快速地返回到高阻抗狀態)。適合高速/RF應用的TVS二極管可提供非常低的觸發電壓(低于100 V)和箝位電壓(低于20 V),同時具有出色的響應時間。

但請注意:片外保護器件的電容將導致RF通道中的不匹配性。為彌補這些不匹配性,設計人員需要調整其RF和天線路徑中的匹配網絡。

更多關于瞬態電壓抑制器(TVS)的信息

TVS二極管是實現ESD保護的首選元件之一。當誘發性電壓超過雪崩擊穿電壓時,它們通過分流過電流的方式運行。它們是一種箝位裝置,抑制所有高于擊穿電壓的過電壓。當不存在過電壓時,它們會自動重置至關閉狀態,但會吸收更多內部的瞬態能量。

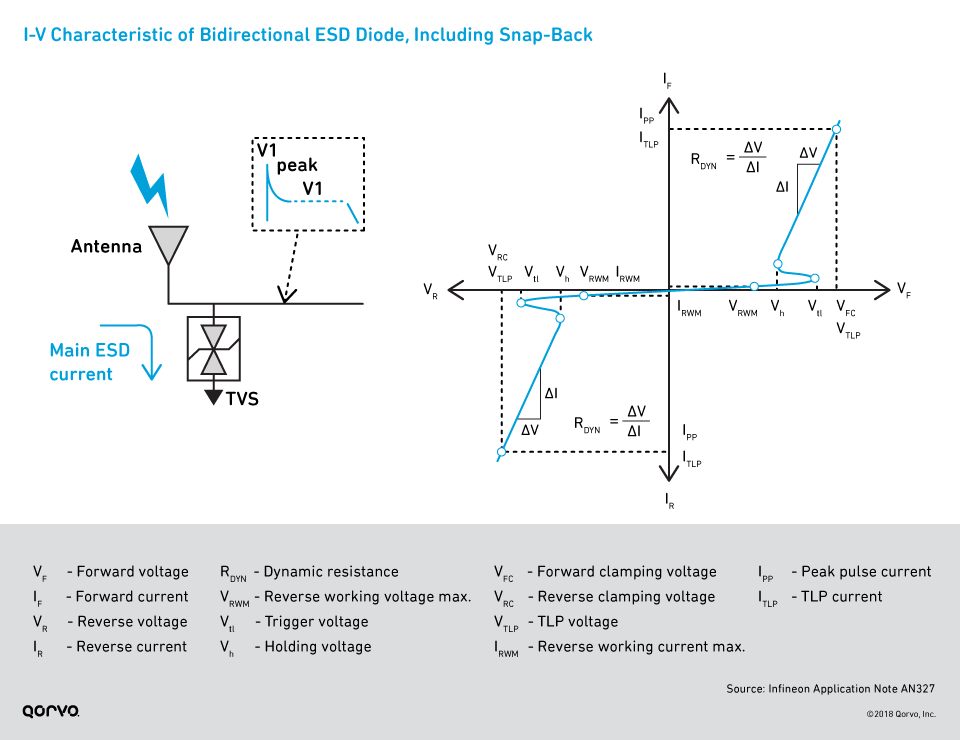

TVS二極管可以是單向二極管,也可以是雙向二極管。雙向二極管可使用兩個相互對立的雪崩二極管以串聯的方式表示,如下所示,并連接至相對于被保護引腳的并聯配置。這些設備均制造為單個封裝元件。

對于RF應用中的ESD保護,必須保持盡可能小的TVS二極管電容。這可避免輸入匹配的失諧,從而使保護設備產生較少的諧波失真。

下圖顯示了雙向TVS二極管的電流-電壓(I-V)曲線。您可以看到,TVS相對于原點呈對稱狀,且可針對正極和負極ESD觸電進行ESD保護。

下圖比較了變阻器、聚合物和TVS二極管響應ESD觸電的殘留電壓。大家可以看到,當今的硅基TVS二極管是針對ESD觸電最有效的方法。

板載TVS二極管位置的重要性

然而,TVS的位置具有重要影響。如果電路設計不當,則ESD保護就不會那么有效。請記住,這些一般原則:

在開發PC電路板時,請注意軌跡不要太長,因為這會產生不必要的電感。

記住:與TVS設備串聯的電容會使一級ESD電流路徑斷開,而添加至一級ESD電流路徑的任何RF電感都會提高殘留路徑中的總阻抗。

如果將TVS置于合適的位置,就不需要其他ESD元件。

那么什么是合適的位置?如下圖所示,您應該:

只使用TVS。

切勿將TVS置于電容或電感器的前面或后面。

確保沒有軌跡。應將TVS置于RF路徑和接地之間。

接地:機械因素

為緩解ESD事件,必須對成品的每一方面進行正確的接地——PC電路板、所有IC芯片和元件、外殼、蓋子等。確保在終端產品接地時考慮了以下所有方面:

所有金屬件必須通過低阻抗路徑連接至系統接地。

浮動金屬部件都有ESD危險。

所有金屬部件都必須接地,或如果適用,更換為塑料件。

多個互聯的PC電路板設計可能會導致高電阻電感系統接地。當一級TVS和RF模塊置于不同的PC電路板上時,應特別注意保護天線。

一級和二級ESD保護

了解一級和二級ESD保護是SEED方法的基本組成部分。通常:

一級保護是在板上進行,稱為主要箝位。

二級保護是在片上進行,稱為輔助箝位。

一級和二級ESD保護階段的協同設計是SEED方法的基本概念。下圖顯示了RF前端(RFFE)中針對ESD保護的主要和輔助箝位的高級基本視圖。

注意:一些系統設計需要在IC前放置一個額外的板載輔助箝位,以減少元件引腳可能存在的任何殘留ESD電荷。

我們來進一步了解一級和二級保護:

一級保護(板載):一級保護可能包含箝位元件,如并聯電感器或TVS元件(二極管、變阻器和火花隙)。這些主要箝位可分流較大的ESD電流。主要箝位主要為與直接ESD能量入口接觸的外部連接和其他接口。此外,它們在減少IC元件引腳處出現的殘留ESD應力方面發揮著重要作用。

二級保護(片上):二級保護用于箝住設備引腳處積累的任何殘留ESD應力。ESD瞬態的形狀在很大程度上取決于板載主要箝位特性和PC電路板設計。

一級和二級ESD保護階段的協同設計(即板載和片上保護)是SEED方法的基本概念。這兩個階段可在兩個分支的載流能力通過串聯阻抗實現平衡的位置提供必要的保護。

模擬和分析這兩個保護階段可幫助電路板設計人員選擇適當的板載保護箝位電平,以確保能夠有效地處理抵達IC的峰值殘留脈沖。利用模擬實現的SEED保護設計要求將國際電工委員會(IEC)應力模型、基于SEED參數的TVS和IC接口引腳模型以及隔離阻抗電路(即PC電路板上的電路)整合在一起。我們將在第3部分詳細介紹如何模擬和分析SEED設計。

RF前端(RFFE)的保護戰略

不同的應用需要不同的ESD保護。一種方法或許能夠滿足您的應用需求,但可能不適用于其他應用。最終,您使用的設計必須通過FCC和IEC測試,這樣您的產品才能獲得認證并出售。我們來看看可用于RFFE中ESD保護的幾種戰略。

1基本保護——并聯電感器

最基本的方法是采用一個并聯電感器。如下圖所示,電感器(L)是ESD電流脈沖的主要分流元件。該電感器的nH范圍應比較低(<20?nH),這樣才能構成有效的?ESD?保護解決方案。但它會增加插入損耗,帶來一些?RF?性能挑戰。并聯電容通常用于實現?RF?匹配,而非?ESD?保護。

2單級高通濾波器

第二種方法采用單級高通濾波器(HPF),如下圖所示。然而,這可能并不是最有效的方法。

優點:

提供良好的全帶寬ESD覆蓋。

可合理地減少ESD脈沖幅度,同時允許蜂窩頻率范圍通過。

缺點:

會產生較高的殘留電壓(Vpeak>100 V)。

需要較低的電感,以確保最優性能(這意味著實現RF與ESD性能權衡)。

3兩級ESD保護

第三種方法使用兩級ESD保護,如下圖所示。該方法將TVS作為一級保護,并將HPF作為二級ESD保護,以捕獲殘留應力。

如下圖中看到的那樣:

第一級保護(TVS)箝住低于20V的電壓,從而將峰值電壓降至50V以下。

第二級保護中的HPF進一步降低殘留電壓脈沖,箝住低于10V的電壓,從而將峰值電壓降至20V以下。

ESD保護的最佳方法

最終,您是在試圖降低IC在ESD觸電中遇到的電壓;目的是在其擊中IC之前降低所有峰值電壓。我們認為理想的ESD戰略就是兩級方法,第一級使用TVS元件(TVS二極管),第二級使用HPF網絡。

優勢:

它可以提高您的電路板級ESD保護,并為您提供通過IEC測試的最佳機會。

此外,它還可以減少ESD脈沖幅度和RF路徑上的殘留電壓。

雙向TVS二極管有助于防止正極和負極脈沖影響。

高通濾波器可箝住任何殘留電壓脈沖。

從而為元件引腳提供最佳保護。

-

ESD

+關注

關注

49文章

2255瀏覽量

174894 -

移動設備

+關注

關注

0文章

511瀏覽量

55072 -

SEED

+關注

關注

0文章

11瀏覽量

9292

原文標題:移動設備的 ESD 設計戰略:您的 SEED 工具是否擁有這些部分?

文章出處:【微信號:Qorvo_Inc,微信公眾號:Qorvo半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

matlab的其他工具箱及SIMULINK

如何在matlab中添加新的工具箱

MATLAB語言工具箱-ToolBox實用指南

***工具箱下載5.8最新版

調試工具箱中所包含的工具介紹

matlab的其他工具箱及SIMULINK

怎樣改善塑料工具箱的鉸鏈

普查工具箱有哪些以及植保儀器工具箱系列的匯總

MATLAB自動駕駛工具箱使用

評論