引 言

USB(通用串行總線)是英特爾、微軟、IBM、康柏等公司1994年聯合制定的一種通用串行總線規范,它解決了與網絡通信問題,而且端口擴展性能好、容易使用。最新的USB2.0支持3種速率:低速1.5 Mbit/s,全速12 Mbit/s,高速480 Mbit/s。這3種速率可以滿足目前大部分外設接口的需要。

本文介紹了目前使用較多的USB2.0控制器CY7C68013芯片與FPGA(現場可編程門陣列)芯片接口的Verilog HDL(硬件描述語言)實現。本系統可擴展,完全可用于其他高速數據采集系統中。

1 系統構成

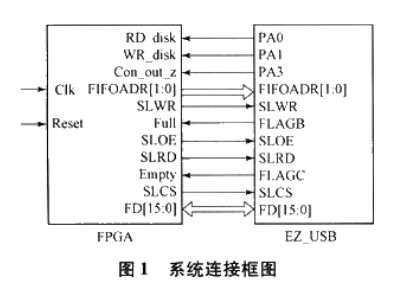

本系統主要是由FPGA和USB2.0控制器CY7C268013組成,系統框圖及其信號連接關系如圖1所示。可以根據實際系統的需要,用FPGA實現預定功能,如數據采集卡、控制硬盤讀寫等。

1.1 控制器CY7C68013

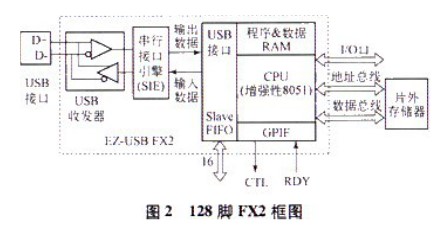

Cypress公司的EZ-USB FX 2是第一個包含USB2.0的集成微控制器,它內部集成了1個增強型的8051、1個智能USB串行接口引擎、1個USB數據收發器、3個8位I/O口、16位地址線、8.5 kB RAM和4 kBFIFO等。增強性8051內核完全與標準8051兼容,而性能可達到標準8051的3倍以上。其框圖如圖2所示。

1.1.1 CY7C68013結構特點

EZ-USB FX2提供了一種獨持架構,使USB接口和應用環境直接共享FIFO,而微控制器可不參與數據傳輸,但允許以FIFO或RAM的方式訪問這些共享FIFO,這種被稱之為“量子FIFO”的處理架構,較好地解決了USB高速模式的帶寬問題。

FX2芯片在數據傳輸時主要利用了4 kB的FIFO,分為7個端點:EPOIN&OUT、EP1IN、EP1OUT、EP2、EP4、EP6和EP8。其中EPO、EPlIN和EP1OUT是3個64 B的緩存,只能被固件訪問,EP0是一個默認的數據輸入輸出端口緩存;EP1IN和EP1OUT是單獨的64 B緩存,呵以配置這些端點為塊傳輸、中斷傳輸或同步傳輸;端點2、4、6、8是大容量高帶寬的數據傳輸端點,可以配置為各種帶寬以滿足實際需要,端點2、4是輸出端點,端點6、8是輸入端點。值得注意的是,端點4、8能配置為每幀512 B,而端點2、6卻能配置為每幀512 B或1 024 B,并可配置為2、3、4級,這樣EP2或EP6最大能配置為4 kB的緩存。

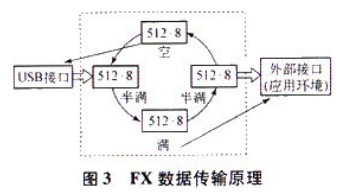

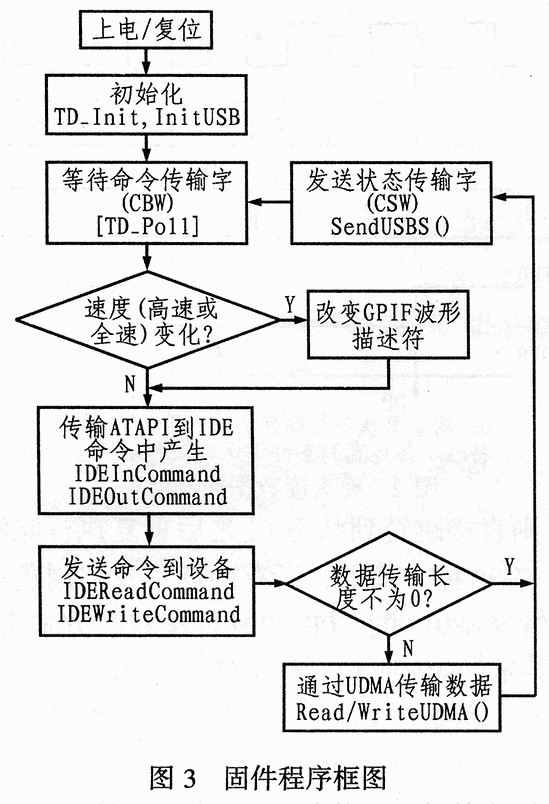

其在內部的傳輸控制是通過full(滿)和empty(空)兩個控制信號來完成的,當full為真時不能再寫數據,當empty為真時不能再對FIFO進行讀,其內部數據傳輸示意圖如圖3所示。

如圖3所示,USB執行OUT傳輸,將EP2端點設成512 B四重FIFO。在USB端和外部接門端都并不知道有四重FIFO。USB端只要有1個FIFO為“半滿”,就可以繼續發送數據。當操作的FIFO寫“滿”時,FX2自動將其轉換到外部接口端,排隊等候讀取;并將USB接口隊列中下一個為“空”的FIFO轉移到USB接口上,供其繼續寫數據。外部接門端與此類似,只要有1個FIFO為“半滿”,就可以繼續讀取數據。當前操作的FIFO讀“空”時,FX2自動將其轉換到USB接口端,排隊等候寫入;并將外部接口隊列中下一個為“滿”的FIFO轉移到外部接口上,供其繼續讀取。

1.1.2 Fx2接口方式

FX2有Slave FIFO和GPIF兩種接口方式。

Slave FIFO是從機方式,即FX的CPU不直接參與USB數據處理,而是簡單地把FX作為USB和外部數據處理邏輯(如ASIC、DSP和IDE(串行接口引擎)控制器)之間的通道,數據流并不經過CPU,而是通過FX的FIFO直接傳輸。FIFO通過外部主機控制,同時,FIFO提供所需的時序信號、握手信號(滿、空等)和輸出使能等。

可編程接口GPIF是主機方式,GPIF作為內部主機控制端點FIFO,其core是一個可編程狀態機,可以生成多達6個控制輸出信號和9個地址輸出信號,能外接6個外部Ready輸入信號和2個內部Ready輸入信號。通過用戶自定義的波形描述符來控制狀態機,使用軟件編程讀寫控制波形,幾乎可以對任何8/16 hit接口的控制器、存儲器和總線進行數據的主動讀寫,非常靈活。

2 接口的Verilog HDL編程實現

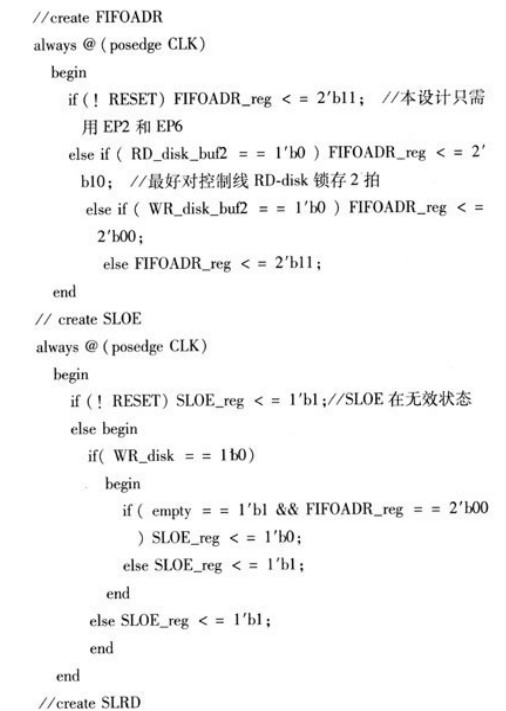

在本設計巾采用Slave FIFO從機方式實現FPGA對FX的控制,通過Verilog HDL編程實現。FPGA可以根據實際情況選定。我們在設計時選用Xilinx公司的Virtex-Ⅱ設備(XC2V10004FG456C)。

2.1 異步FIFO讀數據

FX讀數據也就是數據從FX傳到FPGA的過程,其過程如下:

a)反復檢測控制線狀態,當讀事件發生時,即控制線con_out_z=0和RD_disk=10時,轉到 b;

b)分配FIFOADR[1:0]=00,這時FIFO指針會指向輸出端點,表明使用端點EP2;

c)檢查FIFO是否空,當empy=1時表示FIFO不空,轉到狀態d,否則保持在狀態C;

d)賦值SLOE=0,使雙向數據線FD在輸出狀態,采樣FD數據線上的數據,并在SLRD的上升沿使FIFO指針門動加1,跳轉到e;

e)假如有更多的數據需要讀,轉到狀態b,否則轉到狀態a。

對讀數據編程如下:

用Mentor軟件Modelsim進行仿真驗證,其仿真波形如圖4所示。在此過程中,SLRD信號特別重要,在SLRD的下降沿把FlFO中的數據放到FD數據線上;在SLRD的上升沿把FIFO指針加1,并指向下一個單元。

2.2 異步FIFO寫數據

向FIFO寫數據是讀數據的逆過程,也就是把FP-GA數據寫入FX的FIFO,其編程過程如下:

a)查詢控制信號線con_out_z和WR_disk,看是否有讀事件發生,如果有,就轉移到狀態b,否則保持在狀態a;

b)分配FIFOAFR[1:0]=10,FIFO指針指向輸入端點,轉向狀態c;

c)檢查FIFO的滿標志是否為1,假如fuIl=1,表示FIFO不滿,轉到狀態d,否則保持在狀態c;

d)把外部數據indata放在FD上,同時把SLWR拉高,以使得FIFO指針自動加1,然后轉到狀態e;

e)假如有更多的數據要傳輸,轉到狀態b,否則轉到狀態a。

其程序與寫FIFO數據時一樣,只是在生成SLWR信號時,需要注意控制信號之間的保持延時時間約束,這可以通過仿真結果進行適當修改。

讀數據信號仿真波形如圖5所示。但必須注意的是,在SLWR的下降沿把indata數據線上的數據放到FD數據線上;在SLWR的上降沿把FD數據線上的數據放人FIFO,并同時使FIFO指針加1,指向下一個緩存單元。

3 結束語

現在USB2.O控制器CY7C68013已經應用到許多數據傳輸領域,由于此芯片靈活的接口和可編程特性簡化了外部硬件的設計,提高了系統可靠性,也利于PCB(印制電路板)的制作與調試。本設計可擴展性好,因此可用于需要處理大容量的數據采集系統中。本設計已經用于對IDE硬盤的讀寫控制中,實現了對IDE硬盤的快速讀寫。

-

FPGA

+關注

關注

1630文章

21767瀏覽量

604616 -

控制器

+關注

關注

112文章

16412瀏覽量

178736 -

usb

+關注

關注

60文章

7963瀏覽量

265243

發布評論請先 登錄

相關推薦

基于CY7C68013與FPGA接口的Verilog HDL編程

USB2.0控制器CY7C68013芯片與FPGA芯片接口的Verilog HDL實現

怎么實現USB2.0微控制器CY7C68013的GPIF接口設計?

cy7c68013開發包及驅動

USB2.0控制器CY7C68013特點與應用

基于CY7C68013的USB數據采集系統

USB2.0控制器CY7C68013特點與應用

USB2.0控制器CY7C68013的接口設計實現

基于CY7C68013的高速數據通信接口設計

基于USB2.0芯片CY7C68013的高速數據通信接口設計

CY7C68013和FPGA的數據通信

USB2.0微控制器CY7C68013的GPIF接口設計資料下載

通過CY7C68013控制器與FPGA芯片實現Verilog HDL接口設計

通過CY7C68013控制器與FPGA芯片實現Verilog HDL接口設計

評論