SSPC(固態功率控制器)是由半導體器件構成的智能開關裝置,用于接通/斷開電路,實現電路保護和接收上級計算機的控制信號并向上位機實時反饋其狀態信息。由于控制邏輯完全由CPLD內部的硬件電路完成,因此與功率器件一起工作時,具有很好的電磁兼容性和抗干擾能力。研制多開關的SSPC組共享大規模控制芯片,具有相當大的工程實用價值,尤其適用于空間有限的場合,如飛機上。

本文充分利用CPLD的特點,設計了具有集成度高、速度快、抗干擾能力強和可靠性高等優點的28V直流SSPC。在一塊電路板上集成多個SSPC,各個功率開關問相互獨立工作,進一步提高了功率密度。

1 功能定義

28V直流SSPC應該具有以下功能:

(1) 接收上位機的控制信號。該控制信號能夠兼容TTL/CMOS電平,且高電平表示導通,低電平表示關斷;

(2) 根據流過的SSPC的電流邏輯分析出自身的狀態,并根據表1中的代碼表示上傳給上位機;

(3) SSPC能夠實時診斷自身故障,并根據故障的嚴重程度不同,采取不同的保護措施。

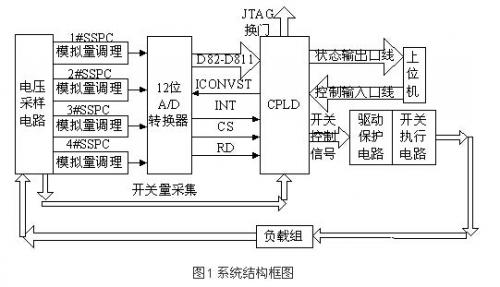

2 總體方案設計

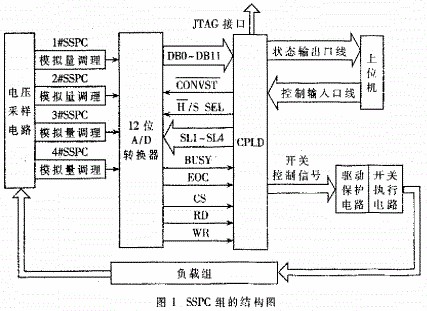

28V直流SSPC組的結構如圖1所示。

每路SSPC的取樣電阻上的電壓經過調理電路和低通濾波以后,送到4通道的A/D轉換器的模擬輸入端,A/D轉換器的數據輸出端、狀態信號和控制信號分別接到CPLD的I/O引腳,便于程序控制A/D轉換器的動作。CPLD另外的I/O口可以配置為MOSFET的動作命令輸出口線、SSPC的狀態輸出口線和與上位機相連的控制命令輸入口線;CPLD自身提供的JTAG BST電路,可以方便地測試系統內部測試器件之間的連接和檢驗器件的操作。

由CPLD組成的邏輯判斷電路的主要功能有:

(1) 將A/D轉換得到的數據通過邏輯判斷,綜合出SSPC的工作狀態并向上位機輸出;

(2) 接收上位機的控制命令,結合自身的工作狀態,綜合得出SSPC的通斷信號,控制MOSFET的開通和關斷。

3 硬件設計

(1) 關鍵器件選型

電力MOSFET選用IR公司的IRF540N,它的漏-源最大耐壓為IOOV,導通阻抗44mΩ,允許通過的最大電流33A。其最大優點為納秒級的開通和關斷時間,能夠完全滿足設計需要。

邏輯控制芯片采用ALTERA公司的flex6000系列。該系列采用的OptiFLEX結構增加了器件的有效面積,可用門的數目達8 000~24 000門,觸發器豐富且基于LUT(查找表)結構,能夠滿足系統處理數據的需要。其待機狀態的電流小于1mA的低功耗模式,具有強功能的I/O引腳和靈活的內部連接等優點,從而使其成為設計首選。

(2) 硬件電路的組成

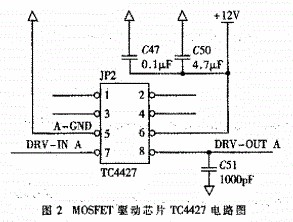

①電力MOSFET驅動和保護電路:采用專門的驅動芯片TC4427,12V供電,如圖2所示。為了抑制電壓和電流的瞬變,MOSFET保護電路采用RCD吸收電路,用以減小器件的開關損耗。

②取樣電路:利用取樣電阻(一般選用康銅絲),將流過負載的電流信號轉化成可測的電壓信號,經過隔離放大器、整流電路、濾波電路、采樣保持器和A/D轉換電路,將數字信號傳送到CPLD進行邏輯分析。

③信號采集和調理電路:通過隔離放大器,將取樣電阻的電壓調節到A/D轉換器的允許范圍內,經過R-C低通濾波器濾除噪聲信號后,送到A/D轉換器的輸入端。

④A/D轉換電路:采用12位的四通道A/D轉換器AD7864,與CPLD的接口主要有:a.數據輸出線:與CPLD的I/O口相連;b.控制線:轉換啟動信號(CONVST)、片選信號(CS)、通道選擇信號(H/S SEL和SL1~SL4)以及讀寫控制信號(RD/WR)等;c.狀態線:BUSY信號和轉換結束標志(EOC)等。

⑤隔離電路:CPLD為3V I/O供電和2.5V內核供電,因此采集的SSPC狀態信號和接收的電力MOSFET控制信號都需要經過電平轉換及電氣隔離,但實際上要采用光耦隔離的方式進行。因為MOSFET的控制信號需要較大的驅動電流,如果直接從CPLD輸出來驅動,會因CPLD電流太小而無法驅動,所以實際中采用六通道反相器74LF04來做光耦前一級的驅動;接收上位機輸出的控制信號是從光耦輸出來的,其電流一般不大(Ie<5mA),所以可以直接接在CPLD的I/O口上。

4 軟件功能設計

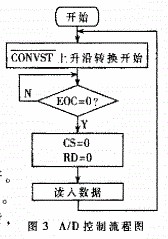

(1) 控制AD7864的動作,從數據口讀出轉換的結果。

運用狀態機的設計方法,AD7864的動作可大致分為3個步驟區間,每個步驟對應一個狀態,每個狀態賦予CPLD特定的功能。

①在步驟S0(CS=1、WR=1、RD=1)時,A/D轉換之中;

②在步驟S1(CS=0、WR=1、RD=1)時,監控EOC信號是否由高電平變為低電平,即

A/D轉換是否結束;

③在步驟S2(CS=0、WR=1、RD=0)時,從DB0~DB11讀取轉換的結果。

軟件流程如圖3所示。

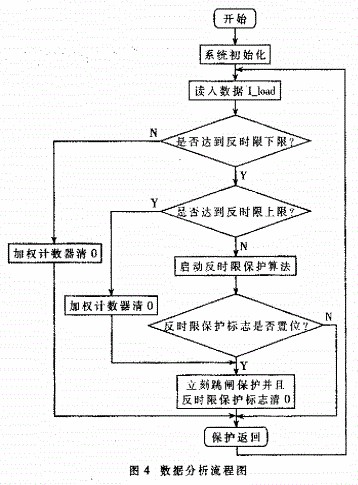

(2) 對采集的數據進行分析。

數據分析流程如圖4所示。

①當電流在額定范圍內時,SSPC正常工作;

②當電流大于額定電流,而小于額定電流的800%時,SSPC進入反時限保護;

③當電流大于額定電流的800%時,SSPC立刻跳閘。

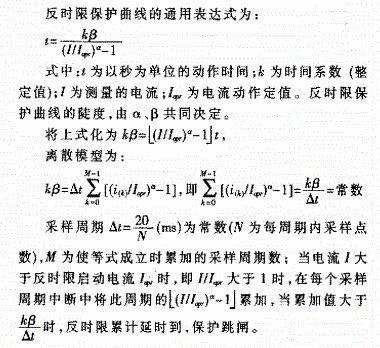

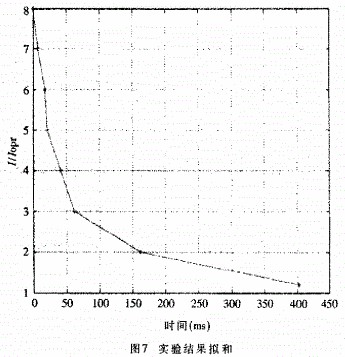

下面介紹SSPC的反時限保護階段的算法推導。

用VHDL語言實現的反時限保護算法流程如圖5所示。

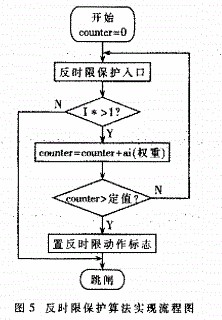

(3) SSPC將內部采集到的電流信號、接收到的控制命令和內部狀態(包括系統啟動的狀態、電流在不同的范圍內變化、跳閘的條件和從跳閘恢復到正常的條件以及故障切除和未切除時的系統啟動等)經過邏輯判斷后,綜合出MOSFET的導通/關斷指令,作為驅動電路的輸入信號。

軟件流程如圖6所示。

5 試驗結果

該仿真是在ALTERA系列CPLD的開發環境MAX+PLUS II上進行的。當在不同的電流值下采集到的四路SSPC負載電流為不同值時,SSPC的工作情況也不一樣。

(1) 當I/Iopr8時,SSPC立即跳閘。

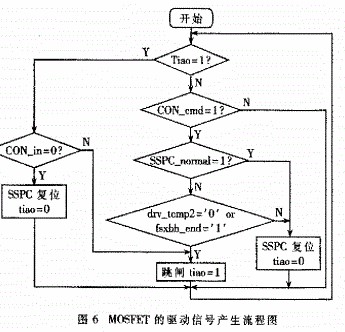

(2) 當I/Iopr為1.2(SSPC_1)、2(SSPC_2)、由1.2增加到2(SSPC_3)和5(SSPC_4)時,SSPC的跳閘時間分別為402ms、161ms、223ms和26ms。

各個臨界點的實驗所得數據經過曲線擬和,得到如圖7所示結果。

試驗結果表明,利用CPLD進行SSPC的開發設計,其延遲時間完全可以通過編程控制,且各路SSPC之間干擾較少。

CPLD內部的硬件結構決定了系統良好的抗干擾性和高可靠性,非常適合于電力系統方面的控制。因此,采用CPLD應是一個研究方向。

-

半導體

+關注

關注

334文章

27538瀏覽量

220159 -

cpld

+關注

關注

32文章

1248瀏覽量

169461 -

控制器

+關注

關注

112文章

16406瀏覽量

178671

發布評論請先 登錄

相關推薦

基于PLD器件EPM3256ATC144-10芯片實現固態功控系統的設計

利用可編程器件CPLD/FPGA實現VGA圖像控制器的設計方案

汽車類多開關檢測接口 (MSDI) 設計包括BOM及組裝圖

多開關檢測接口實現尺寸更小空間利用率更高

淺析多開關檢測接口

如何利用CPLD實現直流固態功率控制器的設計

怎么實現基于DSP芯片和CPLD的剎車控制系統設計?

如何利用CPLD進行數字邏輯器件設計?

CPLD 器件在電機調速中的應用

CPLD器件應用

基于CPLD的電器定時開關控制系統設計

基于CPLD的開關電容組式跟蹤濾波器設計與實現

如何使用CPLD進行電器定時開關控制系統的設計

利用CPLD器件實現多開關的SSPC組共享控制芯片的設計

利用CPLD器件實現多開關的SSPC組共享控制芯片的設計

評論