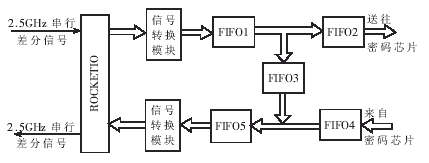

參加國家“863”重大專題項(xiàng)目“高速密碼芯片及驗(yàn)證平臺(tái)系統(tǒng)”的過程中,遇到了將IPV6數(shù)據(jù)包的包頭和數(shù)據(jù)部分拆開,然后在數(shù)據(jù)部分送密碼芯片進(jìn)行加/解密處理,最后再將處理后的數(shù)據(jù)部分與包頭重新封裝為數(shù)據(jù)包的課題。以往對(duì)IP包進(jìn)行拆裝多利用軟件實(shí)現(xiàn),但本項(xiàng)目涉及到配合高速密碼芯片(處理速度在2Gbit/s以上)工作的問題,顯然利用軟件實(shí)現(xiàn)IP包的拆裝在速度上達(dá)不到要求。為此,運(yùn)用FPGA(型號(hào)為Xilinx公司的XC2VP20-FF86CGB0345)來實(shí)現(xiàn)IPV6數(shù)據(jù)包的拆裝。該FPGA內(nèi)部邏輯框圖如圖1所示。

其工作流程為:2.5GHz的標(biāo)準(zhǔn)IPV6數(shù)據(jù)包串行差分信號(hào)通過ROCKETIO高速通道后轉(zhuǎn)換為16位125MHz并行信號(hào),再經(jīng)信號(hào)轉(zhuǎn)換模塊進(jìn)一步轉(zhuǎn)換為66位62.5MHz并行信號(hào)后進(jìn)入FIFO1緩存,然后對(duì)其輸出數(shù)據(jù)進(jìn)行判斷,若是報(bào)頭則送入FIFO3緩存,若是數(shù)據(jù)部分則送入FIFO2緩存,最后將FIFO2數(shù)據(jù)送往密碼芯片進(jìn)行處理;經(jīng)密碼芯片處理的數(shù)據(jù)首先放入FIFO4進(jìn)行緩存,然后控制FIFO3和FIFO4將一個(gè)數(shù)據(jù)包的頭和數(shù)據(jù)寫入FIFO5中,重新封裝成一個(gè)完整的數(shù)據(jù)包;重新封裝的IPV6數(shù)據(jù)包經(jīng)過信號(hào)轉(zhuǎn)換模塊變?yōu)?6位125MHz的并行信號(hào),并通過ROCKETIO高速通道轉(zhuǎn)換為2.5GHz高速串行差分信號(hào)送出。

可以看出,經(jīng)過以上流程,實(shí)現(xiàn)了一個(gè)數(shù)據(jù)包的拆分和重新封裝。

1 IPV6數(shù)據(jù)包的拆分

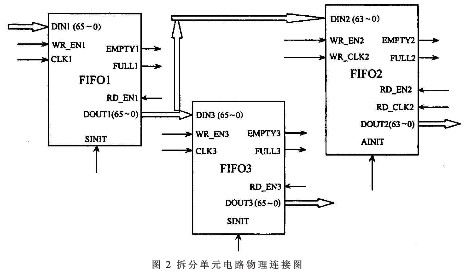

用FPGAP實(shí)現(xiàn)IPV6數(shù)據(jù)包的拆分,主要是通過控制幾個(gè)FIFO的數(shù)據(jù)輸入輸出來實(shí)現(xiàn)的。FPGA內(nèi)部的拆分單元電路的物理連接如圖2所示,其中FIFO的作用是緩存IPV6數(shù)據(jù)包,F(xiàn)IFO2的作用是緩存IPV6數(shù)據(jù)包的數(shù)據(jù)部分,F(xiàn)IFO3的作用是緩存IPV6數(shù)據(jù)包的包頭。

圖中的三個(gè)FIFO都是由Xilinx公司的開發(fā)工具ISE6.1自帶的Core IP生成的。其中FIFO1和FIFO3是同步FIFO,工作時(shí)鐘為頻率62.5MHz,輸入輸出數(shù)據(jù)寬度都是66bit;FIFO2是異步FIFO,輸入時(shí)鐘頻率為62.5MHz,輸出時(shí)鐘頻率為50MHz(密碼芯片的工作時(shí)鐘頻率為50MHz),輸入輸出數(shù)據(jù)寬度都是64bit。

FIFO1的輸入數(shù)據(jù)為IPV6數(shù)據(jù)包。可以看出,該數(shù)據(jù)是以并行的66bit信號(hào)傳輸?shù)模疵恳粫r(shí)鐘周期并行傳送66bit數(shù)據(jù),其中每個(gè)周期的高兩位(即65位和64位)為數(shù)據(jù)包的頭尾標(biāo)志,這是IPV6路由器內(nèi)部根據(jù)實(shí)際處理需要加上的,“10”表示一個(gè)完整數(shù)據(jù)包的第一周期,“11”表示數(shù)據(jù)包的中間內(nèi)容,“01”表示一個(gè)完整數(shù)據(jù)包的最后一個(gè)周期。因?yàn)镮PV6數(shù)據(jù)包的包頭是固定長度的,為40字節(jié)(等于5×64bit),故數(shù)據(jù)的前五個(gè)周期為IPV6數(shù)據(jù)包的包頭,包頭后面跟的就是數(shù)據(jù)包的數(shù)據(jù)部分。

下面討論IPV6數(shù)據(jù)包的包頭和數(shù)據(jù)部分的拆分過程。

首先判斷FIFO1輸入端數(shù)據(jù)的頭尾標(biāo)志DATA(65“64)與FIFO1的滿標(biāo)志FULL1,如果DATA(65”64)=“10”且FULL1=“0”,即判斷到一個(gè)完整數(shù)據(jù)包的開始且FIFO1未滿,則使FIFO1的寫使能WR_EN1有效,寫入數(shù)據(jù);如果DATA(65“64)=“01”,好判斷到一個(gè)完整數(shù)據(jù)包結(jié)束時(shí),則使WR_EN1無效,這樣一個(gè)完整的數(shù)據(jù)包就緩存到了FIFO1時(shí)。

當(dāng)判斷到FIFO1的空標(biāo)示EMPTY1=“0”,即FIFO1非空間,令FIFO1的讀使能信號(hào)RD_EN1有效,將FIFO1中的數(shù)據(jù)讀出,直到EMPTY1=“1”,即FIFO1空為止。對(duì)讀出的數(shù)據(jù)設(shè)定一計(jì)數(shù)器COUNTER1進(jìn)行計(jì)數(shù),當(dāng)DONT1不為0即FIFO1輸出端有信號(hào)時(shí)開始計(jì)數(shù)。當(dāng)0<COUNTER1<=5時(shí),令FIFO3的寫使能信號(hào)WR_EN3有效,將數(shù)據(jù)包的包頭寫FIFO3緩存;當(dāng)COUNTER1>5時(shí),令WR_EN3無效,WR_EN2有效,將IPV6數(shù)據(jù)包的數(shù)據(jù)部分送FIFO2緩存,準(zhǔn)備送密碼芯片處理,直到頭尾標(biāo)志DOUT1(65”64)=“01”時(shí),將COUNTER1清零,在判斷到COUNTER1為0后,將WR_EN2置為無效。注意:FIFO1的輸出端口是66位,F(xiàn)IFO2的輸入端口是64位的,故在FIFO1向FIFO2寫數(shù)據(jù)的過程中,應(yīng)將FIFO1的輸出端口信號(hào)DOUT(63“0)傳送給FIFO2的輸入端口DIN2(63”-)。當(dāng)判斷到FIFO2非空間,將其讀使能信號(hào)RD_EN2置為有效,即可向密碼芯片送出數(shù)據(jù)。

2 IPV6數(shù)據(jù)包的重新封裝

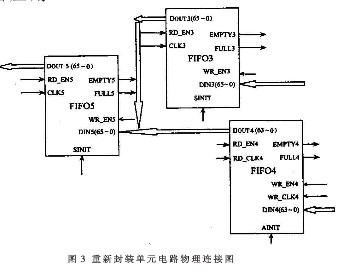

用FPGA實(shí)現(xiàn)IPV6數(shù)據(jù)包的重新封裝,同時(shí)是通過控制幾個(gè)FIFO的數(shù)據(jù)輸入輸出來實(shí)現(xiàn)的,F(xiàn)PGA同部的重新封裝單元電路的物理連接如圖3所示,其FIFO4的作用是緩存密碼芯片送出的加解密處理后的數(shù)據(jù);FIFO5的作用是緩存重新封裝后的IPV6數(shù)據(jù);FIFO3與拆分單元共用,作用是緩用IPV6數(shù)據(jù)包頭。

圖中的FIFO4和FIFO5也都是由Xilinx公司的開發(fā)工具ISE6.1自帶的Core IP生成的,其中FIFO4是異步FIFO,輸入時(shí)鐘為50MHz,輸出時(shí)鐘為62.5MHz,輸入輸出數(shù)據(jù)寬度都是66bit;FIFO5是同步FIFO,工作時(shí)鐘為62.5MHz,輸入輸出數(shù)據(jù)寬度都是66bit。

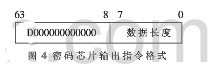

密碼芯片對(duì)數(shù)據(jù)進(jìn)行加/解密處理完畢之后,在送出處理數(shù)據(jù)前,首先向外部系統(tǒng)發(fā)送一64bit長的連接指令,指明處理數(shù)據(jù)所用的加解密算法和數(shù)據(jù)長度。例如,在對(duì)數(shù)據(jù)進(jìn)行2DES加密處理的情況下,接收指令格式(16位制)如圖4所示,其中高56位為指令編碼,低8位為將要輸出的處理數(shù)據(jù)的長度。

因此,在接收處理數(shù)據(jù)時(shí),首先判斷是否有接收指令,如果有接收搦令,則其接收指令中的數(shù)據(jù)長度放寄存器中進(jìn)行寄存,并設(shè)定計(jì)數(shù)器COUNTER2開始計(jì)數(shù)。當(dāng)0<COUNTER2<=數(shù)據(jù)長度時(shí),則令FIFO4的寫使能WR_EN4有效;當(dāng)COUNTER2為其它值時(shí),WR_EN4無效。當(dāng)0<COUNTER2<數(shù)據(jù)長度時(shí),將“11”寫入DIN4(65“64),將64bit處理數(shù)據(jù)寫入DIN4(63”0);當(dāng)COUNTER2=數(shù)據(jù)長度時(shí),即接收到最后一周期的處理數(shù)據(jù)時(shí),將“01”寫入DIN4(65“64),將64bit處理數(shù)據(jù)寫入DIN4(63”0),并將COUNTER2清零。這樣,密碼芯片處理后的數(shù)據(jù)就按格式要求緩存到FIFO4中了。

這時(shí),包頭已經(jīng)緩存到FIFO3中了,處理后的數(shù)據(jù)已經(jīng)按格式要求緩存到FIFO4中了,最后要做的就是控制FIFO3和FIFO4,把一個(gè)完整的IPV6數(shù)據(jù)包寫入FIFO5中。具體做法是:設(shè)定計(jì)數(shù)器COUNTER3,當(dāng)FIFO3和FIFO4都非空時(shí),COUNTER3開始計(jì)數(shù)。當(dāng)COUNTER3>0時(shí),將FIFO5的寫使能信號(hào)WR_EN5置為有效;當(dāng)COUNTER3=0時(shí),WR_EN5置為無效。當(dāng)0<COUNTER3<6時(shí),令FIFO3的讀使能RD_EN3有效,F(xiàn)IFO3將輸出數(shù)據(jù)DOUT3(65“0)寫入FIFO5的輸入端DIN5(65”0);當(dāng)COUNTER3>l=6時(shí),令RD_EN3無效,RD_EN4有效,將FIFO4的輸出數(shù)據(jù)DOUT4(65“0)寫入FIFO5的輸入端DIN5(65”0),直到DOUT4(65“64)=“01”時(shí),將COUNTER3清零,RD_EN4置為無效。這樣,一個(gè)完整的IPV6數(shù)據(jù)包就重封裝在FIFO5中了,當(dāng)判斷到FIFO5非空間,就可以令RD_EN5有效,向外輸出處理后的完整的IPV6數(shù)據(jù)包了。

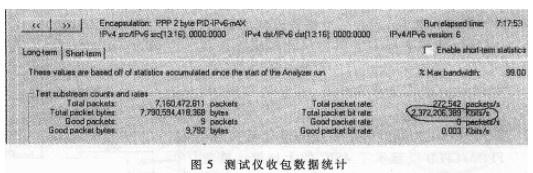

從上述討論可以看出,本課題在FPGA中采用了五個(gè)FIFO,并設(shè)定了三個(gè)計(jì)數(shù)器控制這五個(gè)FIFO的輸入輸出來實(shí)現(xiàn)對(duì)IPV6數(shù)據(jù)包的拆分和重新封裝。總的來看,整個(gè)FPGA設(shè)計(jì)思路巧妙,電路結(jié)構(gòu)簡單,達(dá)到了預(yù)期的處理速度。圖5是整個(gè)測試系統(tǒng)在對(duì)1024字節(jié)的IPV6數(shù)據(jù)包進(jìn)行拆包、送密碼芯片加密。重裝封裝處理后測試儀控制軟件界面上顯示的收包數(shù)據(jù)統(tǒng)計(jì)。從該圖可以看出,整個(gè)系統(tǒng)對(duì)IPV6數(shù)據(jù)包的處理速度達(dá)到了2.372Gbit/s,而這樣的處理速度用軟件是不可能達(dá)到的。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603012 -

芯片

+關(guān)注

關(guān)注

455文章

50714瀏覽量

423158 -

計(jì)數(shù)器

+關(guān)注

關(guān)注

32文章

2256瀏覽量

94478

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

IPv6地址是什么,IPv6的意思

基于IPv6的無線傳感器網(wǎng)絡(luò)邊界路由器有什么優(yōu)點(diǎn)?

怎樣利用FPGA來實(shí)現(xiàn)IPV6數(shù)據(jù)包的拆裝?

基于FPGA的IPV6數(shù)據(jù)包的拆裝是如何實(shí)現(xiàn)的?

IPv6不能外發(fā)數(shù)據(jù)包如何解決呢

一種IPv6數(shù)據(jù)包安全傳輸?shù)?b class='flag-5'>實(shí)現(xiàn)

基于IPv6的防火墻的關(guān)鍵技術(shù)與實(shí)現(xiàn)

基于FPGA的IPV6數(shù)據(jù)包的拆裝

移動(dòng)IPV6在改進(jìn)數(shù)據(jù)包發(fā)送路徑模型下性能分析

IPv6中的網(wǎng)絡(luò)隱蔽通道技術(shù)研究

BGP/MPLS IPv6 VPN技術(shù)白皮書

基于FPGA的IPV6數(shù)字包的分離與封裝的實(shí)現(xiàn)

如何用隧道搭建ipv6

基于XC2VP20—FF896CGB0345 FPGA實(shí)現(xiàn)IPV6數(shù)據(jù)包的拆裝

通過運(yùn)用FPGA器件實(shí)現(xiàn)IPV6數(shù)據(jù)包的拆分和重新封裝

通過運(yùn)用FPGA器件實(shí)現(xiàn)IPV6數(shù)據(jù)包的拆分和重新封裝

評(píng)論