x1電壓放大器或“緩沖器”是模擬設計的標準構建模塊。本文介紹了一種元器件數量少的高性能分立式匹配晶體管緩沖器的設計,并涵蓋優化其設計的一些細節。

在用一個運算放大器就可以輕松實現緩沖器的時代,為什么要使用分立電路?當高精度和最小空間不是特別重要的指標時,零件成本為50美分的雙JFET放大器足以滿足性能要求,它可提供數百兆赫的帶寬,偏移誤差僅10mV或更低,漂移為10μV/oC或更少。通過應用創新,分立元件電路也可以獲得良好的性能,即使運算放大器過時仍然可以使用。緩沖器也可以成為設計庫的一個重要部分。

緩沖放大器電路

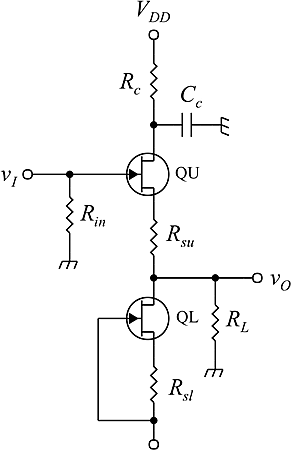

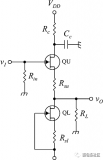

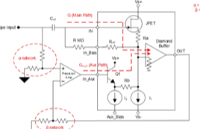

x1電壓放大器的設計目標是實現這樣的理想電壓放大器:無限大的輸入阻抗、零輸出阻抗和線性度。為了實現高輸入阻抗,使用JFET而不是BJT,如圖1的緩沖電路所示。

圖1:為了實現高輸入阻抗,使用JFET而不是BJT。

離散JFET器件可從多家供應商獲得,包括:

·Linear Systems

·飛利浦(現恩智浦)

·東芝

·Vishay Siliconix

盡管單封裝雙器件(如2N3958、2N5196~2N5199,以及2N5564~2N5566等)在熱跟蹤方面具有優勢,為降低成本,我們還是選擇離散JFET器件。低端的雙器件價格每個大約4.50美元,最好的則超過40美元。如果您可以承擔額外的成本,可以選擇價格貴的雙器件,因為它們的熱跟蹤性能優于離散JFET。

設計緩沖器所需要的一些離散N溝道JFET的替代器件包括2N5484~2N5486。2N5485的成本約為每個0.20美元(批量采購數百個時)。其漏極電流的標稱設計值在4~10mA規定范圍內,中值為IDSS = 7mA(IDSS為ID@VGS = 0V)。此外,選擇了兩個JFET以便使用曲線跟蹤器進行匹配。可以通過人工將它們分類為匹配的IDSS箱,每對花費不到一分鐘的時間,產生的額外成本為0.10美元(按照美國勞動力成本計算)。

接下來,選擇一些標準電源電壓:VDD = +12V,VSS = -5V。這些電源電壓在桌面電腦和儀器中都很常見。

失調電壓

匹配JFET的第一個設計特征是匹配晶體管的靜態(dc)跟蹤。如果底部晶體管QL的柵極連接到其源極,則VGS = 0V,漏極電流為IDSS。如果相同的電流通過QU(帶有開路負載),那么由于它是匹配的,其VGS也是零,并且輸入到輸出之間沒有電壓失調。

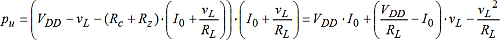

這一絕妙的設計技巧還可以通過將JFET工作點設置為零TC點來改善,其中具有給定ID的VGS的熱漂移在整個溫度范圍內是最小的。對于JFET,零漂移VGS比夾斷電壓高約0.8V。VGSZ的值是各種溫度的ID線相交的地方。對于2N5485,這大約為-1.2V,比-2V左右的夾斷電壓高約0.8V。2N5485(Siliconix)的曲線如圖2所示。

圖2:2N5485(Siliconix)的曲線圖。

使用這些值,Rsl = Rsu = Rs = 1.2V/5mA = 240Ω,容差為5%。Rsl上的壓降在波形路徑中通過匹配電阻器Rsu上的類似壓降進行補償。為了更好地匹配,這些電阻的容差可以是1%。

熱失真

隨著輸入電壓的變化,兩個JFET的功耗也會發生變化。功率的變化引起硅溫度的變化,這會導致放大器響應中產生熱感應電噪聲或“熱”。這種“噪聲”與波形有關,最好視為熱失真。通過設置JFET最大功耗的工作點(op-pt或偏置)可以使JFET的功耗最小,而無需改變輸入(即在op-pt點)。功率的變化(我們希望最小化)在峰值功率附近最小,其中拋物線的導數值或斜率最小。

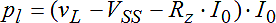

讓JFET的工作點 - 靜態偏置電流為I0。那么上、下晶體管消耗的功率為:

而且:

其中vL是RL上的負載電壓。功耗的差為:

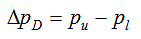

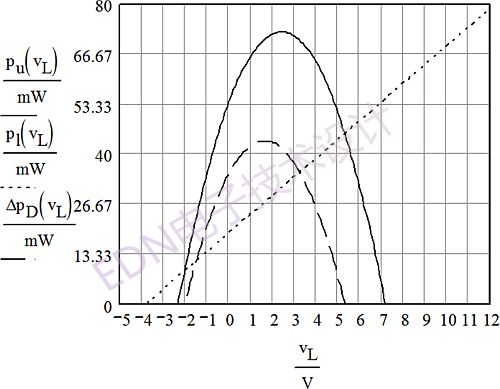

圖3是利用MathCAD匯制的功耗圖。

圖3:利用MathCAD匯制的功耗圖。

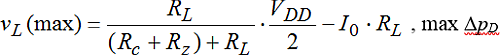

ΔpD最大時,功率隨vL的變化最小,這是使熱失真最小所需要的。最大差分功率時的vL值為:

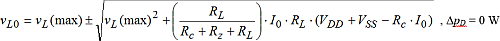

另一個感興趣的電壓是pu與pl相等時。在ΔpD = 0W時求解vL:

在圖3中,vL0 = 5.3V。雖然功耗在此輸出電壓下匹配,但圍繞此值的任何變化都會導致ΔpD的變化大于vL(max)附近vL的相同變化。因此,優選的偏置點是vL(max)。

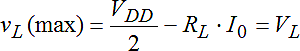

在圖3中,vL(max) = 1.62V。但是,給定的電路參數導致靜態vL為0V。為了調整JFET上的靜態電壓,增加了一個額外的串聯電阻Rc。一般情況下,讓靜態輸出電壓為VL。然后在VL處設置差分功率拋物線的頂點:

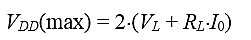

求解滿足所需條件的VDD的值:

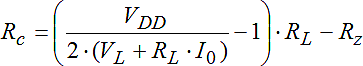

然后將VL和供電電壓VDD代入下式:

在這個設計中,Rc = 490Ω。Cc繞過Rc,使得漏極處不會出現明顯的電壓變化。

匹配BJT緩沖放大器

JFET優于BJT,因為它具有高輸入電阻和低輸入偏置電流。然而,對于相同的溫度系數(TC),JFET的電流匹配必須比BJT好十倍。這就是為什么JFET輸入運算放大器的輸入失調規范通常比BJT的要差。簡而言之,BJT比JFET匹配得更好。

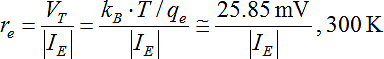

如果您的緩沖設計不需要高輸入電阻,請改用BJT。使用QL的固定基極電壓,必須以稍微不同的方式實現偏置。這使得QL成為由于VBE(T)而隨溫度漂移的電流源。發生類似漂移的匹配QU具有相同的偏置電流和動態發射極電阻:

當ICL(=IEU)隨溫度變化時,電阻保持恒定。隨著溫度升高,VBEL降低,ICL升高。同時,reU隨熱電壓VT增加,但增加的發射極電流通過降低reU來補償。來自QL的電流TC補償re的變化,這會影響緩沖器電壓增益。

這里介紹的基本緩沖級可以通過跟從互補BJT CC級來改進,其中消除了NPN和PNP的b-e結。如果匹配的NPN與QL源串聯,它將補償隨后的NPN CC級。

-

放大器

+關注

關注

145文章

14150瀏覽量

217499 -

元器件

+關注

關注

113文章

4838瀏覽量

95293 -

晶體管

+關注

關注

77文章

10022瀏覽量

141899

原文標題:緩沖放大器設計

文章出處:【微信號:eet-china,微信公眾號:電子工程專輯】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

評論