引言

數據采集設備是測試系統中不可缺少的一部分,數據采集需要針對不同類型的需求,需要有高速A/D、低速A/D、數字多用表等功能,傳統數據采集設備是用一種儀器進行一類測試,通過多種儀器組合實現一組完整測試,這種由多種儀器堆疊起來的數據采集系統具有體積和重量較大、成本較高、維護困難等諸多問題。針對這些問題,為完成某系列型號裝備自動測試任務,設計實現了一種高集成度數據采集設備。該設備需實現100 M高速A/D、雙通道隔離A/D、6通道低速A/D和數字多用表功能,采集數據通過LAN傳輸給上位機。輸入前端調理電路支持寬范圍多種信號輸入,并采用超寬輸入范圍的保護電路,實現設備通用性的同時保證其安全可靠。本設計采用DSP+FPGA架構,利用DSP/BIOS實時操作系統,結合TI提供的NDK 網絡開發工具包,選用高集成度芯片,在10 cm×18 cm面積上設計實現該數據采集系統。

1 總體設計

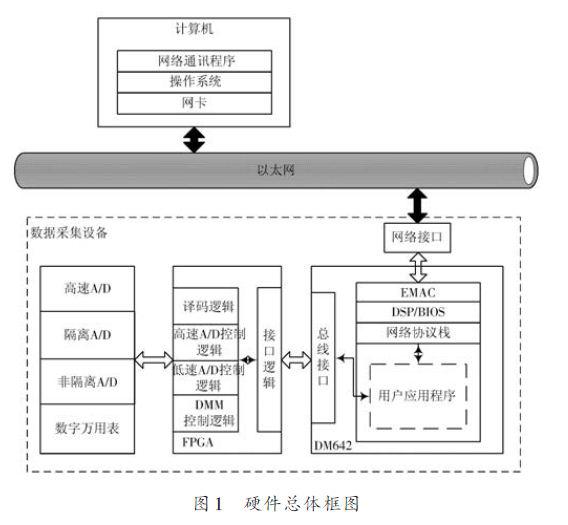

設備的總體結構如圖1所示。設備能夠接入到以太網中,并能夠被計算機遠程訪問。

計算機中網絡通訊程序控制設備進行數據采集并讀取數據。整個設備以DSP+FPGA核心,包含高速A/D、低速隔離A/D、低速非隔離A/D和數字多用表。DSP選用TI公司主頻720 MHz、32 b定點高性能的TMS320DM642,DM642完成了網絡、主控功能。利用DM642的自帶的網絡功能接口,結合TI提供的網絡功能開發包(NDK)實現網絡通訊功能。采用DSP/BIOS實現分配調度線程、數據采集任務和網絡控制傳輸任務,實現對數據采集、存儲和網絡通訊的控制。FPGA選用Altera公司的CycloneⅢ系列低成本工業級的EP3C55F484I8,編寫接口邏輯實現與DM642的數據交互,編寫譯碼邏輯、高速A/D控制邏輯、低速A/D控制邏輯、數字多用表控制邏輯實現數據采集功能。

2 硬件設計

2.1 網絡接口設計

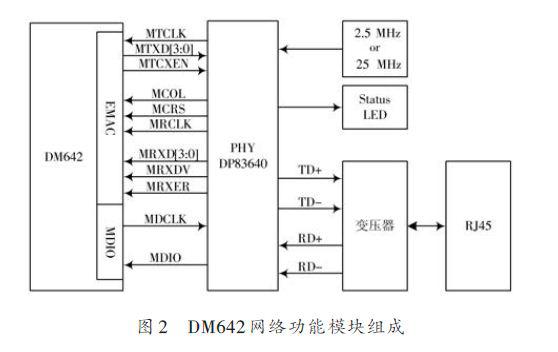

TMS320DM642 自帶一個網絡功能接口,由EMAC控制模塊、EMAC 模塊和MDIO 模塊組成[4],符合IEEE802.3協議,在設計網絡通訊接口時只需要外接一片網絡收發芯片即可,DM642的網絡功能模塊如圖2所示。

網絡收發芯片選用美國國家半導體公司推出的DP83640,其MII接口與DM642 的EMAC 接口直連,MII接口包括接收總線和發送總線,接收部分包括接收數據線RXD[30],接收錯誤標志RX_ER,接收數據有效標志RX_DV 和數據同步接收時鐘信號RX_CLK,當工作在10 Mb/s 時,RX_CLK 為2.5 MHz,工作在100 Mb/s 時,RX_CLK 為25 MHz.發送部分包含發送數據線TXD[30],發送使能位TX_EN,和發送時鐘TX_CLK,同樣,時鐘可以為2.5 MHz或者25 MHz.另外,MII接口帶有沖突檢測信號COL,用于檢測在半雙工模式下發送和接收同時發生的情況。該芯片具有的IEEE1588功能方便日后設備升級時鐘同步功能。

2.2 A/D采集模塊設計

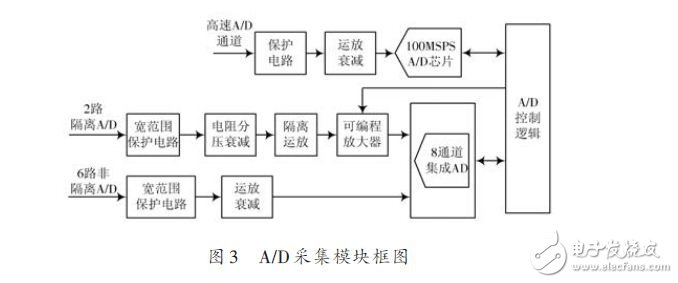

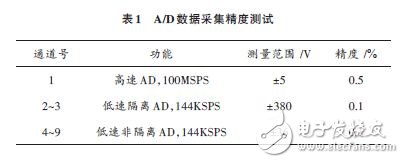

A/D 采集單元分為1 路高速采集和8 路低速采集兩部分,其中低速采集部分,分為2路隔離通道和6路非隔離通道,總圖框圖如圖3 所示。高速采集通道選用14 位的A/D6645,最高采樣率105 MSPS,并行輸出。低速采集通道選用24位的A/DS1278,單片并行8通道,最高采樣率144 KSPS,采用8 路串行輸出,同時采集8 路輸入信號。兩路隔離通道選用A/D215隔離運放。

兩路隔離通道輸入電壓范圍±380 V,輸入阻抗為10 MΩ,1 路高速通道和6 路非隔離通道前端均采用運放衰減,分別實現±5 V 和±40 V 電壓輸入范圍,高輸入阻抗和寬范圍電壓輸入范圍使該設備能夠適應大部分被測系統,實現了設備的通用化。每通道前端采用壓敏電阻和自恢復保險絲設計寬范圍高可靠保護電路,保證設備的穩定性和安全性。

2.3 數字多用表模塊設計

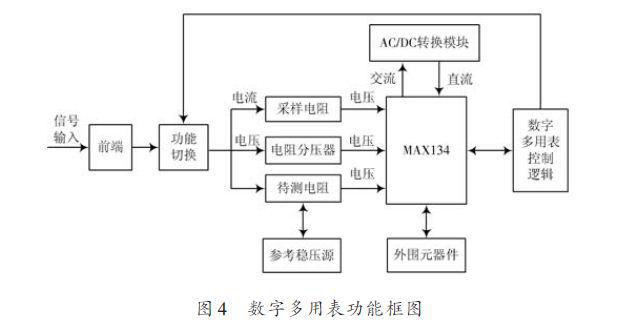

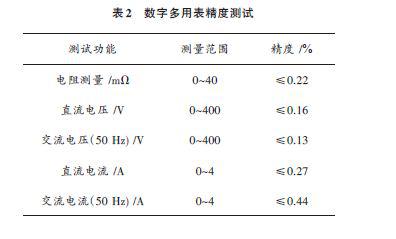

該設備對數字多用表測量速度、精度要求不是很高,但要求電路板的體積盡可能的小,因此在數字多用表電路設計上,選用了MAXIM 公司生產的MAX134 作為測量的核心芯片。MAX134 是單片智能數字多用表專用芯片,在其外圍配置少量元器件,設計簡單的電路即可實現精度達到3位半的數字多用表。該設備的數字多用表功能框圖如圖4所示。采用繼電器實現功能切換;電阻分壓器實現0~400 V交、直流電壓輸入;0.1 Ω和1 Ω采樣電阻實現0~4 A交、直流電流轉換為電壓信號輸入;AC/DC轉換模塊采用有效值轉換芯片A/D637,實現交流信號轉直流;參考穩壓源提供電阻測試的參考電壓,實現0~40 MΩ 電阻測量;外圍元器件實現MAX134 正常工作所需的晶振、電源、濾波等功能。

FPGA 內部邏輯控制功能切換、實現MAX134內部寄存器的讀寫,進而實現數字多用表功能。

3 軟件設計

3.1 網絡通訊功能實現方法

本設計利用DSP/BIOS 結合NDK 實現網絡通訊功能。DSP/BIOS 是TI 公司為C28x,C5000 和C6000 系列DSP開發的可剪裁實時多任務操作系統,同時也是CCS提供的一套多任務開發、硬件抽象、實時分析和系統配置的專用工具。DSP/BIOS以其功能豐富的APIs綜合管理系統內存,實現任務分配和調度,實時監測分析系統運行,并提供方便的數據通信接口和外設驅動開發工具。NDK是TI專門為網絡應用開發提供的網絡開發工具包,利用其TCP/IP協議棧開發網絡應用具有成本低、開發周期短的特點。網絡性能由套接字類型、套接字緩沖區、CPU速度和CPU緩沖等幾方面決定。要使用NDK 必須在DSP/BIOS 中配置TCP/IP 協議棧,主要在DSP/BIOS的。cdb文件中做以下配置:

(1)全局設置GBL

設置系統初始化函數dm642_init,用于設置L2 模式,分配MAC地址;

(2)設置MEM對象

配置程序、數據存儲區域及堆棧大小;

(3)設置HOOK對象

設置NDK的TCP/IP協議棧保存空間;

(4)設置PRD對象

設置NDK HAL庫中的定時驅動事件;

(5)設置線程TSK

靜態創建2個線程:TSK_idle線程,優先級最低,當系統沒有其他任務執行時運行;TSK_main主線程,優先級最高,用于配置服務器信息及啟動HTTP服務。

配置文件生成之后,在DSP/BIOS 中編寫網絡主線程TSK_main,用于啟動運行TCP/IP 協議棧,啟動HTTP服務,同時不斷監測和響應網絡底層事件。在主線程中可以動態創建任務,用于實現與其他網絡設備的網絡通訊功能。

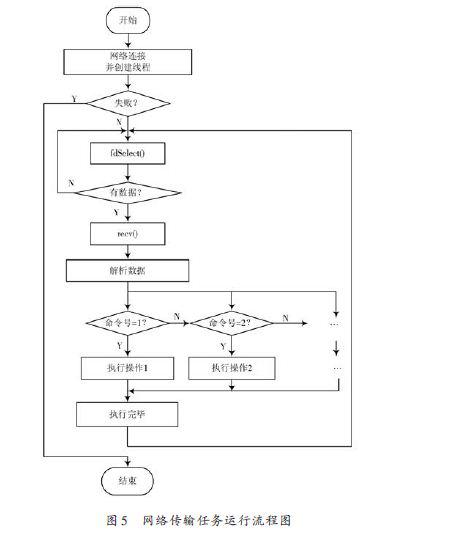

3.2 多任務線程管理機制

為了優化CPU資源,實現各功能的協調運作,需要合理劃分功能、規劃任務。本設計構建了按優先級從高到低創建了高速A/D 線程、低速A/D 線程、數字多用表線程、網絡傳輸線程和網絡配置線程。其中,網絡傳輸任務是最核心的任務線程,主要完成創建線程、網絡命令解析、通道查詢和數據上傳的功能,流程圖如5所示。

網絡傳輸任務使用套接字編程,工作在服務器模式,通訊方式采用TCP.首先調用fdOpenSession()函數建立文件描述表,調用socket()創建套接字,然后綁定IP信息、監聽,然后等待客戶端連接請求,一旦客戶端連接上,便調用fdSelect()函數檢測客戶端是否發送數據,如果有數據則接收,否則繼續檢測,除非客戶端斷開連接。在這種設計模式下,允許客戶端重復的執行斷開、連接操作,保證了系統工作的穩定性。

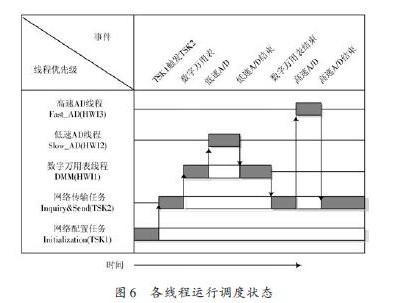

DSP/BIOS 支持硬件中斷(HWI)、軟件中斷(SWI)、任務(TSK)和空閑線程(IDL)4種類型的線程,它們的線程優先級從高到低。硬件中斷線程主要用來處理響應時間要求嚴格的請求,同時它的優先級最高,能搶占當前運行的其他線程及時運行,本設計各線程運行調度狀態如圖6所示。

圖中黑色陰影部分表示線程運行,白色不封表象線程掛起。高速A/D處理的數據量最大,對處理響應的時間要求嚴格,故將它的優先級設為最高,能搶占當前運行的其他線程及時運行,保證數據實時上傳,低速A/D線程和數字多用表線程的優先級根據其對時間的要求逐次降低。

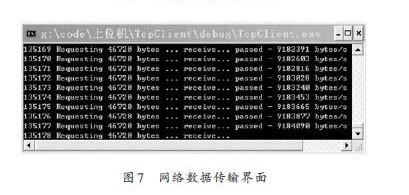

4 測試

為了測試接口板的網絡通訊功能,使用PC 機作為客戶端,與設備通過路由器連在局域網內。設備作為服務器端,在PC機端采用VS2005編寫上位機網絡通訊程序,每次傳輸46 720 B數據,在開始和結束數據傳輸時刻讀取系統時間,并計算出網絡傳輸的速率,如圖7所示。

DM642中L2的Cache大小會影響網絡傳輸速度,實驗發現,當Cache大小在128 KB是,傳輸速率達到了最佳,為89.2 Mb/s,由于在局域網中網絡環境相對復雜等原因,沒有達到理想的100 Mb/s的傳輸速率。A/D數據采集和數字多用表功能的測試,利用Agilent E3631A直流電源、Agilent 34110A6位半數字多用表和正泰TDGC2-0.2電源模塊等儀器,測試結果如表1和表2所示。

5 結語

本設備選用高性能高集成芯片,采用DSP+FPGA的主控方案,實現了數據采集設備的小型化。前端調理電路支持多種信號的寬動態范圍測量,并具有可靠的過壓保護,保證了設備的通用性與安全性。以DM642 的硬件資源為基礎,通過調用NDK提供的APIs,實現了百兆以太網的傳輸。同時,利用DSP/BIOS的多任務機制,實現網絡控制、數據采集以及網絡通訊的有效配合,保證底層高速采集的大數據量快速可靠得上傳給上位機。

實際應用表明,該設備穩定可靠、實時性強、兼容多種被測系統,在數據采集領域中有一定的應用價值。

-

dsp

+關注

關注

553文章

7987瀏覽量

348773 -

FPGA

+關注

關注

1629文章

21729瀏覽量

603020 -

數據采集

+關注

關注

38文章

6057瀏覽量

113625

發布評論請先 登錄

相關推薦

注塑機實現數據采集數字化轉型

FPGA的多通道數據采集傳輸系統

小型化晶振的影響有哪些

天拓四方:設備數據采集網關如何有效解決生產設備數據采集的難題?

PLC采集網關如何實現多品牌PLC數據采集

小型化電路如何設計?工程師:只需注意這5點!

數據采集處理設備是什么?數據采集處理設備的功能

物通博聯PLC網關實現mewtocol協議PLC設備數據采集

基于DSP技與+FPGA器件實現數據采集設備的小型化

基于DSP技與+FPGA器件實現數據采集設備的小型化

評論