l 引 言

隨著近年來芯片制造技術的不斷發展,以及市場對高性能數字信號處理器的需求,新的功能更強,速度更快,功耗更低的數字信號處理器(DSP)產品不斷推出,給電路設計帶來了極大的方便。但與此同時,這些高性能器件的使用對供電模塊的設計提出了更高的要求。高效、穩定、滿足上電次序的供電模塊設計具有重要意義,將直接影響整個系統的穩定,甚至整個系統的實現。

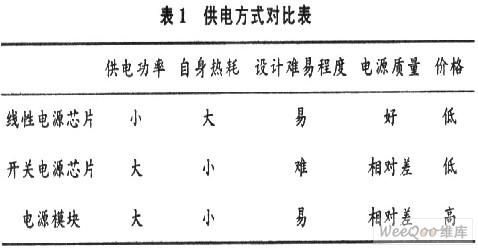

當前,DSP、FPGA等芯片的供電方式主要有3種:采用線性電源芯片,采用開關電源芯片,采用電源模塊。這3種方式的一個總體對比如表1所示。

線性電源的基本原理是根據負載電阻的變化情況來調節自身的內阻,從而保證輸出端的電壓在要求的范圍之內。由于采用線性調節原理,瞬態特性好,本質上沒有輸出紋波。但隨著輸入輸出電壓差的增大或是輸出電流增加,芯片發熱會成比例增加,因此線性電源要求有較好的散熱處理控制。線性電源的輸入電流接近于輸出電流,它的效率(輸出功率/輸入功率)接近于輸出/輸入電壓比。因此,壓差是一個非常重要的性能,因為更低的壓差意味著更高的效率。LDO線性電源的低壓差特性有利于改善電路的總體效率。線性電源對電流輸入較小的應用系統提供了一種體積小、廉價的設計方案。

開關電源利用磁場儲能,無論升壓、降壓或是兩者同時進行,都可以實現相當高的變換效率。由于變換效率高,因此發熱很小,散熱處理得以簡化。又由于是開關穩壓器電源,與LDO線性電源相比,DC/DC調整器輸出紋波電壓較大、瞬時恢復時間較慢、容易產生電磁干擾(EMI)。要取得低紋波、低EMI、低噪聲的電源,關鍵在于電路設計,尤其是輸入/輸出電容、輸出電感的選擇和布局。因此在三種電源設計方案中,開關電源的設計要較另兩種電源設計方案復雜。但由于開關電源設計靈活,耗熱小,成本也較低,在系統電源模塊設計中,仍不失一種較好的選擇。

電源模塊原理上講是個開關穩壓器,效率非常高。相對于普通開關穩壓器,它的集成度更高,外圍只需要一個輸入電容和一個輸出電容即能工作,設計簡便,適合D要求開發周期非常短的應用。

2 芯片選型和功能介紹

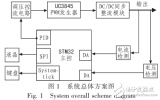

由于ADSPTSl01信號處理部分僅是整個系統的一個子部分,結合其他部分的供電要求,FPGA芯片采用ATERA公司的EPlCl2F324,IO電壓3.3 V,內核電壓1.5 V,ADSPTS101的IO供電壓3.3V,內核電壓1.2V。其中EPlCl2F324對上電次序的要求并不是太嚴格,電源設計較為簡單,采用AS2830一1.5電源芯片即可達到要求。而ADSPTSl01對上電次序有較為嚴格的要求,當上電次序沒有達到要求時,既使上電后進行復位初始化后,初始狀態仍然可能不對。因此,系統電源部分設計的重點在于滿足ADSPTS101的上電要求。當然,采用電源模塊,如PT*4芯片可以滿足設計要求,但基于開關電源和電源模塊的比較優勢,本系統采用進行設計。采用的電源芯片為TI公司的TPS54616和TPS54312。

TPS54616是一款TI公司推出的適合DSP,FPGA,ASIC等多芯片系統供電的電源芯片,是一款低電壓輸入、大電流輸出的同步降壓DC/DC調整器,內含30MQ、12 A峰值電流的MOSFET開關管,最大可輸出6A電流。輸出電壓固定3.3V,誤差率為1%。開關頻率可固定在350 kHz或550 kHz,也可以在280 kHz到700 kHz之間調整。另外,它還具有限流電路、低壓閉鎖電路和過熱關斷電路。

TPS54312也同樣是TI推出的一款低電壓輸入,大電流輸出的同步降壓DC/DC調整器。所不同的是,TPS54312對于連續3 A的電流高效輸出,集成的MOS-FET開關管為60MQ,同時其固定電壓輸出為1.2V。

另外,TPS54616和TPS54312均采用集成化設計,減少了元件數量和體積,因此,可廣泛用于低電壓輸入、大電流輸出的分散電源系統中。

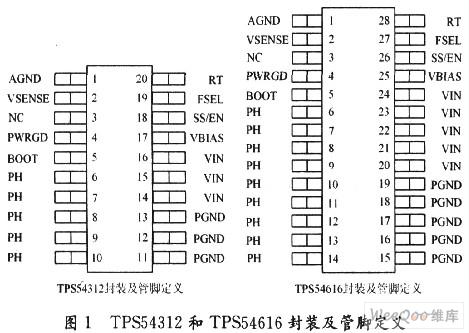

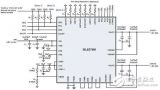

TPS54616和TPS54312功能管腳定義類似,其引腳封裝分別如圖1所示。

以TPS54616為例,簡述各引腳功能,TPS54312對應命名相同的引腳功能相似。AGND:模擬地;BOOT:啟動輸入,應和PH腳間連接一個0.02~O.1μF的電容;NC:不連;PGND:電源地,使用時與AGND單點連接;PH:電壓輸出端;WRGD:當VSENSE>90%參考電壓時,輸出為高阻,否則輸出為低電平,利用這點,可用于I/O口電壓和內核電壓的控制,設計出符合要求的上電次序;RT:頻率設置電阻輸入,選擇不同的阻值連接,可設置不同的電源開關頻率;SS/ENA:慢啟動或輸入輸出使能控制;FSEL:頻率選擇;VBIAS:內部偏壓調節,與AGND間應連接一個0.1~1μF的陶瓷電容;VIN:外部電壓輸入;SENSE:誤差放大反饋輸入,可直接連到輸出電壓端。

3 電路設計

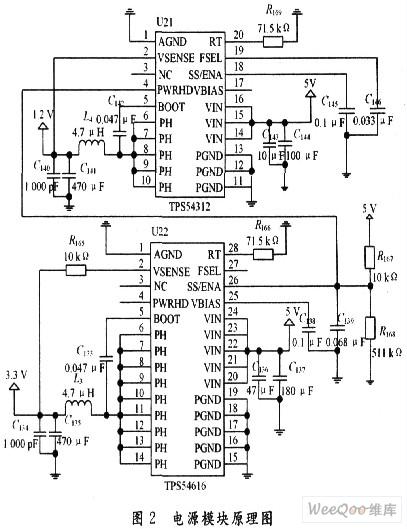

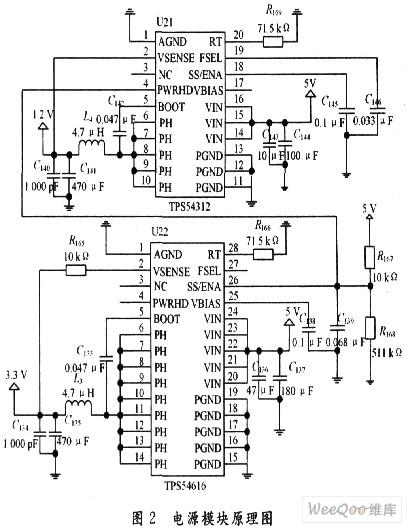

在Protel中搭建原理圖,如圖2所示。

設計主要考慮了輸入濾波、反饋回路、頻率操作、輸出濾波、延時啟動等問題。

3.1 輸入輸出濾波

兩電源芯片輸入電壓均為5 V,為有效慮除輸入電源中的高頻分量,輸入端均接一個10μF的旁路電容。同時,為減少輸入紋波電壓,各接入一個100μF和180μF的濾波電容。經過這樣的組合濾波,可以得到一較為干凈的輸入電源。在輸出端,為了得到質量較好的輸出波形,輸出濾波網絡由一個4.7μH電感及一個470μF和1 000 pF的電容組成。

3.2 反饋回路

TPS54312上為直接反饋,經過濾波輸出后的電壓直接連接到VSENSE上,TPS54616加上一個反饋電阻,作用其實是相同的,都是直接反饋。

3.3 開關頻率設計

如果讓RT腳空接,FSEL接地或接在VIN上,則開關頻率為350 kHz或550 kHz。如果采用外接電阻進行開關頻率選擇,有計算阻值的公式為:R=500 kHz/選擇的開關頻率×100 kΩ。設計中選用開關頻率700 MHz,計算得應接電阻阻值為71.5 kΩ。

3.4 延時啟動

兩芯片均有慢啟動和輸出輸入使能控制功能。通過在腳SS/EN上連接不同容值的電容,可以獲得不同的慢啟動時間。盡管有專門的計算公式可以進行計算,但這里設計可以利用TI為專門電源設計推出的軟件swift desig-ner,可以為設計提供很大的方便。swift designer提供一系列的電源芯片支持設計,包括對TPS54312和TPS54616的支持。

在swift designer中設置參數,然后按“GO”,軟件即能自動按照要求的參數選擇電源芯片和搭建好外圍電路。設參數為:輸出電壓1.2V,輸出電流3A,輸入最小電壓4.8V,最大5.2V,慢啟動時間3 ms,開關頻率700 kHz。軟件可以自動生成電路圖,軟件自動選擇的電源芯片是TPS54312,同時外圍電路已經連接好。

同樣修改參數,輸出電壓3.3V,輸出電流6A,輸入最小電壓4.8V,最大5.2V,慢啟動時間6 ms,開關頻率700 kHz。同樣,這時軟件自動生成5V轉3.3V的電路圖(略)。

在swift designer軟件的幫助下,使設計變得靈活和簡便。要獲得正確的上電次序,設計中還應做一些調整。將TPS5431 2的PWRGD腳接至TPS54616的SS/ENA腳,如圖2中原理圖所示,同時接成上拉狀態。這樣,只有當TPS54312輸出電壓大于1.2 V*90%時,腳PWRGD輸出為低,從而使能TPS54616,產生3.3 V的電壓輸出,從而獲得正確的上電次序要求。在TPS54312輸出電壓沒有達到要求時,TPS54616被上拉,不能產生3.3 V輸出。這樣通過慢啟動時間的設置和對使能端引腳的控制兩重保險.可以完全確保正確的上電延時和上電次序。同時,我們可以根據不同芯片對上電延時和上電的次序進行靈活調整,滿足上電要求。

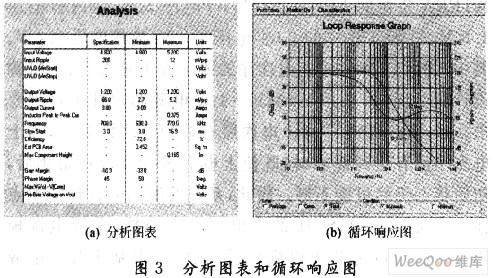

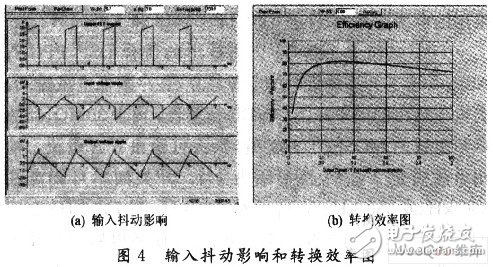

4 仿真分析

swift designer軟件還提供了初步的仿真分析,能直觀地給出分析表,循環響應圖,輸入電壓抖動的影響圖,效率圖和PCB布線圖。下面是一系列相關仿真分析。

從仿真可以看出,設計所采用的電源轉換具有較高的轉換效率,同時由于輸入抖動而帶來的影響也在系統可接受范圍之內,加上外圍電容濾波后,輸出電壓紋波效果還會有所改進。由于軟件沒有對上電次序的先后給出直觀仿真,但通過對兩電源芯片慢啟動時間的設置先后和使能端的控制,系統上電次序得到了較好保證。

5 結 語

供電模塊設計對整個系統實現和系統良好運行意義重大,尤其對一些特殊供電要求的高性能器件而言更是如此。在電源模塊的設計中,要綜合考慮系統要求,設計靈活性,實現難易程度,成本、效率、封裝等相應因素,從而做出全面的、折衷的考慮,以尋求最佳的設計方案。經過在雷達信號處理板上的實際應用,設計滿足各項電壓、電流和功耗要求,同時由于采用較好的上電次序設計,保證了ADSPTSl01的內核先于IO上電,從而使整個系統穩定性和可靠性得到了較好保證。

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603798 -

芯片

+關注

關注

456文章

50879瀏覽量

424136 -

開關電源

+關注

關注

6465文章

8343瀏覽量

482272

發布評論請先 登錄

相關推薦

如何測試FPGA的供電電源

DC_DC開關電源模塊并聯供電系統均流控制研究

基于FPGA異步串行通信接口模塊設計與實現

光開關模塊控制電路工作時序的FPGA實現方法

程控開關電源并聯供電系統的設計與實現

數字電源模塊在FPGA供電設計的應用

如何吧項目實現在FPGA芯片中

FPGA_ASIC-S698MSoC芯片中EDAC模塊的設計與實現

開關電源模塊并聯供電系統總結

開關電源模塊并聯供電系統的設計報告

基于FPGA芯片實現開關供電模塊的設計

基于FPGA芯片實現開關供電模塊的設計

評論