Altera 公司的Cyclone IV 系列FPGA包括兩個(gè)系列:Cyclone IV E和Cyclone IV GX,具有低成本、低功耗的FPGA 架構(gòu),6 K 到150 K 的邏輯單元,高達(dá)6.3 Mb 的嵌入式存儲(chǔ)器,小于1.5 W 的總功耗;Cyclone IV GX 器件提供高達(dá)八個(gè)3.125 Gbps高速收發(fā)器,用于大批量,成本敏感的應(yīng)用如無(wú)線、有線、廣播、工業(yè),用戶以及通信等行業(yè)。本文介紹了Cyclone IV 器件系列主要特性,收發(fā)器通道框圖以及Cyclone IV GX FPGA開(kāi)發(fā)套件主要特性,框圖,電路圖和材料清單。

Altera 新的Cyclone?IV 系列 FPGA 器件鞏固了Cyclone 系列在低成本、低功耗FPGA市場(chǎng)的領(lǐng)導(dǎo)地位,并且目前提供集成收發(fā)器功能的型號(hào)。Cyclone IV 器件旨在用于大批量,成本敏感的應(yīng)用,使系統(tǒng)設(shè)計(jì)師在降低成本的同時(shí)又能夠滿足不斷增長(zhǎng)的帶寬要求。

Cyclone IV 器件系列是建立在一個(gè)優(yōu)化的低功耗工藝基礎(chǔ)之上,并提供以下兩種型號(hào):

■ Cyclone IV E- 最低的功耗,通過(guò)最低的成本實(shí)現(xiàn)較高的功能性

■ Cyclone IV GX- 最低的功耗,集成了3.125 Gbps 收發(fā)器的最低成本的FPGA

Cyclone IV 器件集成了一個(gè)可選擇的低成本收發(fā)器,在未影響性能的情況下,節(jié)省了功耗及成本。針對(duì)無(wú)線、有線、廣播、工業(yè),用戶以及通信等行業(yè)中的低成本的小型應(yīng)用,Cyclone IV 器件無(wú)疑是最理想的選擇。

Cyclone IV 器件系列主要特性:

■ 低成本、低功耗的FPGA 架構(gòu):

■ 6 K 到150 K 的邏輯單元

■ 高達(dá)6.3 Mb 的嵌入式存儲(chǔ)器

■ 高達(dá)360 個(gè)18 × 18 乘法器,實(shí)現(xiàn)DSP 處理密集型應(yīng)用

■ 協(xié)議橋接應(yīng)用,實(shí)現(xiàn)小于1.5 W 的總功耗

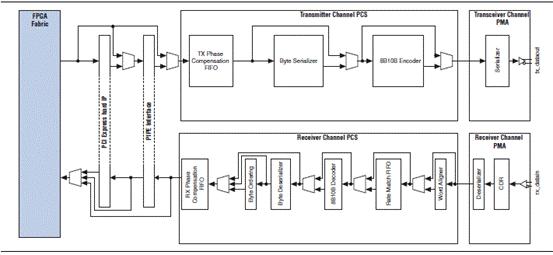

■ Cyclone IV GX 器件提供高達(dá)八個(gè)高速收發(fā)器以支持:

■ 高達(dá)3.125 Gbps 的數(shù)據(jù)速率

■ 8B/10B 編碼器/ 解碼器

■ 8-bit 或者10-bit 位物理介質(zhì)附加子層(PMA) 到物理編碼子層(PCS) 接口

■ 字節(jié)串化器/ 解串器(SERDES)

■ 字對(duì)齊器

■ 速率匹配FIFO

■ 公共無(wú)線電接口(CPRI) 的TX 位滑塊

■ 電路空閑

■ 動(dòng)態(tài)通道重配置以實(shí)現(xiàn)數(shù)據(jù)速率及協(xié)議的即時(shí)修改

■ 靜態(tài)均衡及預(yù)加重以實(shí)現(xiàn)最佳的信號(hào)完整性

■ 每通道150 mW 的功耗

■ 靈活的時(shí)鐘結(jié)構(gòu)以支持單一收發(fā)器模塊中的多種協(xié)議

■ Cyclone IV GX 器件對(duì)PCI Express (PIPE)(PCIe)Gen 1 提供了專用的硬核IP:

■ ×1,×2, 和×4 通道配置

■ 終點(diǎn)和根端口配置

■ 高達(dá)256-byte 的有效負(fù)載

■ 一個(gè)虛擬通道

■ 2 KB 重試緩存

■ 4 KB 接收(Rx) 緩存

■ Cyclone IV GX 器件提供多種協(xié)議支持:

■ PCIe (PIPE) Gen 1×1,×2, 和×4 (2.5 Gbps)

■ 千兆以太網(wǎng)(1.25 Gbps)

■ CPRI ( 高達(dá)3.072 Gbps)

■ XAUI (3.125 Gbps)

■ 三倍速率串行數(shù)字接口(SDI)( 高達(dá)2.97 Gbps)

■ 串行RapidIO(3.125 Gbps)

■ Basic 模式( 高達(dá)3.125 Gbps)

■ V-by-One( 高達(dá)3.0 Gbps)

■ DisplayPort(2.7 Gbps)

■ 串行高級(jí)技術(shù)附件(Serial Advanced Technology Attachment (SATA))( 高達(dá)3.0 Gbps)

■ OBSAI( 高達(dá)3.072 Gbps)

■ 高達(dá)532 個(gè)用戶I/O

■ 高達(dá)840 Mbps 發(fā)送器(Tx), 875 Mbps Rx 的LVDS 接口

■ 支持高達(dá)200 MHz 的DDR2 SDRAM 接口

■ 支持高達(dá)167 MHz 的QDRII SRAM 和DDR SDRAM

■ 每器件中高達(dá)8 個(gè)鎖相環(huán)(PLLs)

■ 支持商業(yè)與工業(yè)溫度等級(jí)

Cyclone IV 器件系列體系結(jié)構(gòu)

這一部分介紹了Cyclone IV 器件的體系結(jié)構(gòu),其中包括以下幾方面內(nèi)容:

■ FPGA 核心架構(gòu)

■ I/O 特性

■ 時(shí)鐘管理

■ 外部存儲(chǔ)器接口

■ 配置

■ 高速收發(fā)器( 僅適用于Cyclone IV GX 器件)

■ PCI Express 的硬核IP( 僅適用于Cyclone IV GX 器件)

FPGA 核心架構(gòu)

Cyclone IV 器件采用了與成功的Cyclone 系列器件相同的核心架構(gòu)。這一架構(gòu)包括由四輸入查找表(LUTs) 構(gòu)成的LE, 存儲(chǔ)器模塊以及乘法器。

每一個(gè)Cyclone IV 器件的M9K 存儲(chǔ)器模塊都具有9 Kbit 的嵌入式SRAM 存儲(chǔ)器。您可以把M9K 模塊配置成單端口、簡(jiǎn)單雙端口、真雙端口RAM 以及FIFO 緩沖器或者ROM,通過(guò)配置也可以實(shí)現(xiàn)表1-7 中的數(shù)據(jù)寬度。

Cyclone IV 器件中的乘法器體系結(jié)構(gòu)與現(xiàn)有的Cyclone 系列器件是相同的。嵌入式乘法器模塊可以在單一模塊中實(shí)現(xiàn)一個(gè)18 × 18 或兩個(gè) 9 × 9 乘法器。Altera 針對(duì)乘法器模塊的使用提供了一整套的DSP IP,其中包括有限脈沖響應(yīng)(FIR), 快速傅里葉變換(FFT) 和數(shù)字控制震蕩器(NCO) 功能。Quartus?II 設(shè)計(jì)軟件中的DSP Builder 工具集成了MathWorks Simulink 與MATLAB 設(shè)計(jì)環(huán)境,從而實(shí)現(xiàn)了一體化的DSP 設(shè)計(jì)流程。

圖1.Cyclone IV GX 器件的收發(fā)器通道框圖

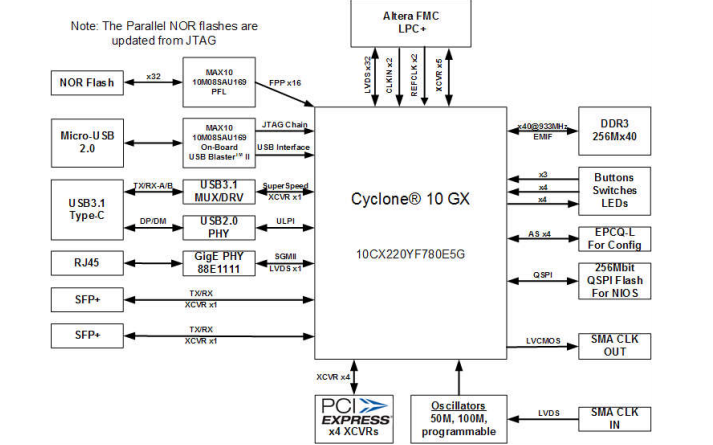

Altera Cyclone IV GX FPGA開(kāi)發(fā)套件

Altera? Cyclone? IV GX FPGA開(kāi)發(fā)套件為迅速開(kāi)始開(kāi)發(fā)低成本、低功耗FPGA系統(tǒng)級(jí)設(shè)計(jì)提供了全面的、同類最佳的設(shè)計(jì)環(huán)境。該套件幫助您縮短了產(chǎn)品開(kāi)發(fā)周期,使您能夠更迅速的將產(chǎn)品推向市場(chǎng),樹(shù)立新的產(chǎn)品里程碑。采用這一平臺(tái),您能夠:

使用Cyclone IV GX PCI Express硬核知識(shí)產(chǎn)權(quán)(IP)和PCI-SIG?兼容電路板,開(kāi)發(fā)并測(cè)試PCI Express? Gen1 x1、x2、x4端點(diǎn)設(shè)計(jì)。

使用板上DDR2存儲(chǔ)器,通過(guò)其擴(kuò)展功能,高速中間鏈接卡(HSMC)連接器,開(kāi)發(fā)并測(cè)試多通路協(xié)議橋接設(shè)計(jì)。Altera合作伙伴提供30多種不同的HSMC,以及CPRI、SATA和SDI等支持協(xié)議。

重新使用套件電路板測(cè)試系統(tǒng)提供的實(shí)例設(shè)計(jì),加速您的FPGA設(shè)計(jì)。

針對(duì)您產(chǎn)品的低成本和低功耗電路板,使用套件的主板作為設(shè)計(jì)模型。

Cyclone IV GX FPGA開(kāi)發(fā)套件包括:

Cyclone IV GX FPGA開(kāi)發(fā)板(參見(jiàn)圖1)

安裝的器件

F896封裝的Cyclone IV GX EP4CGX150N FPGA

配置狀態(tài)和設(shè)置單元

通過(guò)MAX? II EPM2210 CPLD和閃存進(jìn)行被動(dòng)串行(PS)配置

使用Quartus?II編程器的板上USB-BlasterTM下載電纜

時(shí)鐘

板上時(shí)鐘振蕩器:50 MHz、100 MHz(可設(shè)置)和125 MHz

用于外部時(shí)鐘輸入的SMA連接器

用于時(shí)鐘輸出的SMA連接器

通用用戶輸入和輸出

LCD顯示屏

按鍵和雙列直插封裝(DIP)開(kāi)關(guān)

存儲(chǔ)器件

128-MB DDR2 SDRAM,支持32位數(shù)據(jù)總線。

64-MB同步閃存和4-MB SSRAM

元件和接口

PCI Express邊沿連接器

10/100/1000-Mbps以太網(wǎng)PHY,提供RJ-45連接器。

兩個(gè)HSMC連接器

電源測(cè)量電路

電源

筆記本計(jì)算機(jī)直流輸入

PCI Express邊沿連接器電源

其他特性

PCI Express短卡

符合RoHS

Cyclone IV GX FPGA開(kāi)發(fā)套件軟件組成

設(shè)計(jì)實(shí)例

電路板更新入口,含有Nios?II處理器網(wǎng)絡(luò)服務(wù)器,支持遠(yuǎn)程系統(tǒng)更新。

電路板測(cè)試系統(tǒng)

免費(fèi)的Quartus II網(wǎng)絡(luò)版軟件,包括對(duì)Cyclone IV FPGA的支持,以及:

Nios II嵌入式設(shè)計(jì)套裝

MegaCore?IP庫(kù)包括PCI Express、三速以太網(wǎng)、SDI和DDR2高性能控制器MegaCore IP內(nèi)核

通過(guò)OpenCore Plus進(jìn)行IP評(píng)估

回環(huán)和調(diào)試HSMC

電源適配器和電纜

圖2.Cyclone IV GX FPGA開(kāi)發(fā)套件外形圖和主要元件分布圖

The board features the following major component blocks:

■ Cyclone IV GX EP4CGX150DF31 FPGA in the 896-pin FineLine BGA (FBGA)package

■ 1.2-V core power

■ MAX? II EPM2210GF256 CPLD in the 256-pin FBGA package

■ 1.8-V core power

■ FPGA configuration circuitry

■ MAX II CPLD EPM2210 System Controller and flash fast passive parallel (FPP) configuration

■ Active serial configuration

■ On-board USB-BlasterTM for use with the Quartus? II Programmer

■ JTAG header for external USB-Blaster with the Quartus II Programmer

■ On-Board ports

■ Embedded USB-Blaster

■ One gigabit Ethernet port

■ Communication ports

■ PCI Express (PCIe) edge connector

■ 10/100/1000BASE-T Ethernet PHY with RJ-45 connector

■ Two High-Speed Mezzanine Card (HSMC) interfaces

■ On-Board memory

■ 4-MB (x16) Synchronous Static Random Access Memory (SSRAM)

■ Two 32-MB (x32) DDR2 SDRAM

■ 64-MB flash

■ On-Board clocking circuitry

■ 50.000-MHz oscillator

■ 125.000-MHz oscillator

■ SMA clock input

■ SMA clock output

■ Programmable oscillator (default: 100.000-MHz)

■ General user I/O

■ LEDs and display

■ Eight FPGA user LEDs

■ One configuration done LED

■ One error LED

■ Five Ethernet status LEDs

■ One USB status LED

■ One power status LED

■ Five configuration LEDs

■ A two-line 16-character LCD display

■ Push-Button switches

■ One CPU reset push-button switch

■ One MAX II configuration reset push-button switch

■ One program-load push-button switch-configure the FPGA from flash memory

■ One program-select push-button switch-select image to load from flash memory or serial configuration (EPCS) device

■ Four general user push-button switches

■ DIP switches

■ Board settings DIP switch

■ JTAG chain select DIP switch

■ PCIe control DIP switch

■ Configuration settings DIP switch

■ User DIP switch

■ Power supply

■ 16-V DC input

■ 2.5-mm barrel jack for DC power input

■ On/Off slide power switch

■ On-Board power measurement circuitry

■ 20-W per HSMC interface

■ Mechanical

■ PCIe small form factor board

■ Bench-top operation

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

602997 -

嵌入式

+關(guān)注

關(guān)注

5082文章

19104瀏覽量

304810 -

編碼器

+關(guān)注

關(guān)注

45文章

3638瀏覽量

134426 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7484瀏覽量

163763

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Altera宣布開(kāi)始提供Cyclone V SoC開(kāi)發(fā)套件

什么是Altera系列低成本Cyclone IV FPGA?

Altera交付Stratix IV GX收發(fā)器信號(hào)完整性開(kāi)

Altera提供Arria II GX開(kāi)發(fā)套件,加速高性能3

Altera推出面向Stratix IV FPGA的最新開(kāi)發(fā)

Altera推出具有530K邏輯元件FPGA 的開(kāi)發(fā)套件

低功耗Cyclone IV FPGA

基于Arria II GX FPGA的開(kāi)發(fā)方案

Altera Cyclone IV GX系列FPGA開(kāi)發(fā)方案

Altera交付業(yè)界最全面的28nm FPGA系列開(kāi)發(fā)套件

Altera全面28nm FPGA及開(kāi)發(fā)套件快速突擊

Cyclone 10 GX開(kāi)發(fā)套件板的電路原理圖免費(fèi)下載

Altera Cyclone IV GX系列的特性及FPGA開(kāi)發(fā)套件的設(shè)計(jì)方案介紹

Altera Cyclone IV GX系列的特性及FPGA開(kāi)發(fā)套件的設(shè)計(jì)方案介紹

評(píng)論