隨著IEEE Std 1394-1995技術的高速發展,IEEE 1394已經成為眾多電子設備基本的外部接口。然而,要進一步擴展它的適用領域,就必須克服其接口被限制工作在較短距離以及不適用于較高數據傳輸率的缺陷。IEEE Std 1394b-2002作為其修訂版本支持800 Mb·s-1傳輸速率,且中繼距離長達100m。它將原來的DS(Data-Strobe)編碼方式改進為8B/10B編碼方式,這對于1394性能的改進起著決定性作用。同時,1394b是向下兼容的,也就是說同一個電路既可以選擇使用DS編碼也可以選擇使用8B/10B編碼。

現在符合1394b標準的鏈路層和物理層控制芯片都遵循1394 OHCI(開放式主機控制接口協議),它的主要功能是實現總線的鏈路層協議。本系統通過NIOSII處理器,根據1394 OHCI,對FPGA以及1394套片進行控制,實現了雙向數據傳輸。其主要功能是將外部視頻數據打包,按照1394b協議,傳輸到主機端進行實時顯示,并實現與主機的相互通信。

1 1394 OHCI的特點

支持事務層和總線管理層,而且帶有一個PCI主機總線接口,以及高速率數據傳輸所需要的DMA引擎。支持兩種數據傳輸:異步傳輸和等時傳輸。

異步傳輸:1394 OHCI可以發送和接收所有1394所定義的數據包格式。無論是從主機存儲器中讀出發送數據包,還是將接收到的數據包寫入主機存儲器,都是通過DMA來實現的。在向主機總線存儲空間讀和寫時,1394 OHCI也可以通過直接執行1394讀和寫請求而作為主機總線和1394之間的總線橋。

等時傳輸:1394 OHCI可以執行循環控制器的功能。也就是說它包含了一個循環計時器和計數器,可以在8 kHz時鐘的每個上升沿后安排一個循環開始包的傳輸。1394 OHCI可以產生內部時鐘。當它不是循環控制器時,1394 OHCI根據循環開始包,通過更正其循環計時器來保持它的內部時鐘與主節點的周期同步。1394 OHCI為等時發送和等時接收各提供了一個DMA控制器。每個DMA控制器支持高達32個不同的DMA上下文(context)。等時發送DMA控制器可以在每個周期,從每個上下文發送數據。而每個上下文只能從唯一的等時信道發送數據。等時接收DMA控制器可以在每個周期,從每個上下文接收數據。但是每個上下文既可以從唯一的等時信道接收數據,也可以從多個等時信道接收數據。

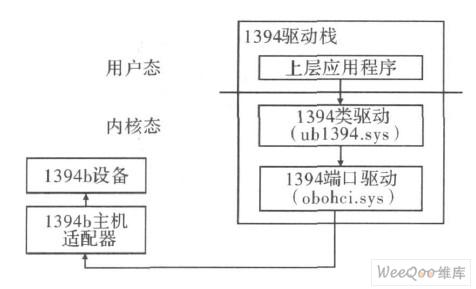

2 硬件結構

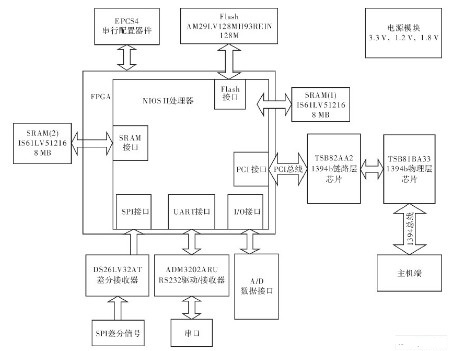

以FPGA內嵌的NIOSII處理器為開發平臺,控制實現數據的雙向傳輸。其硬件結構框圖如圖1所示。主要由NIOSII系統模塊、SPI口的數據輸入輸出模塊、1394套片模塊、SRAM模塊、串口(UART)通信模塊、電源管理模塊、EPCS模塊和Flash模塊組成。其中,FPGA芯片為主控芯片,選擇Ahera公司Cyclone II系列的EP2C70F672C8N;Flash芯片用于存儲NIOSII嵌入式處理器的代碼和數據,FPGA上電后從中讀取;SRAM芯片一個用于對外部大量視頻數據進行緩存,另一個作為C代碼的運行空間。串口主要用以產生異步數據,外部視頻數據則主要通過SPI口進行等時傳輸。

圖1 系統的硬件結構框圖

3 軟件工作流程

在NIOSII IDE集成環境下,根據1394 OHCI協議,使NIOSII處理器實現對總線的初始化,以及管理,并通過DMA方式實現等時和異步數據傳輸。其中等時數據傳輸僅考慮將外部視頻數據打包發送到主機,而異步數據傳輸分為主機發起的異步傳輸和1394設備發起的異步傳輸。

3.1 系統的自舉

主要為系統初始化、檢測電纜以及根節點的確定。系統初始化主要是配置鏈路層芯片寄存器,使其工作在需要的狀態下。分為對PCI寄存器的初始化和對OHCI寄存器的初始化。對PCI寄存器的初始化包括對TSB82AA2設備ID和PCI廠商ID的驗證,OHCI基地址寄存器的設置以及對指令狀態寄存器的配置。而對OHCI寄存器的初始化則包括對各個中斷寄存器和DMA上下文的設置,以及控制寄存器的配置。檢測電纜是否插入是通過讀取物理層芯片某寄存器的相應位來判斷的。電纜插入后,通過檢查和配置Node ID寄存器,強制設置本節點為子節點,主機為根節點,直到成功為止。

3.2 數據的傳輸

在1394 OHCI中,不管是等時傳輸,還是異步傳輸,都是通過DMA方式實現的,而且每個DMA都有一個FIFO,用于暫時存放數據。其中各FIFO的存儲容量為:異步發送(AT)FIFO為5 kB,異步接收(AR)F7FO為2 kB,等時發送(IT)fIFO為2 kB,等時接收(IR)FIFO為2 kB。無論是物理層接收到的還是要發送出去的數據包,都被暫時存放在相應的FIFO中,由1394套片的內部邏輯控制將其傳送到1394總線上。

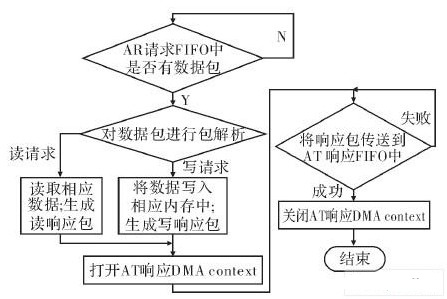

(1)主機發起的異步傳輸。

主機發起的異步傳輸即由主機發出異步傳輸請求,1394設備進行響應,因此在這一部分,主要是異步請求包的接收以及異步響應包的發送。其工作流程如圖2所示。1394設備接收到主機發來的異步請求包后,就會產生異步接收請求中斷,這可由鏈路層芯片中斷寄存器的RQPkt位表征。當一個數據包傳送完畢后,數據包的最后一個指令描述符的xferStatus字段將被重置,這時數據包已被成功傳送到AT響應FIFO中。

圖2 主機發起的異步傳輸工作流程

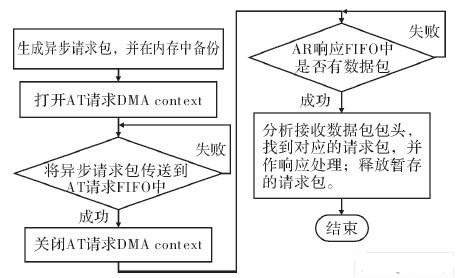

(2)1394設備發起的異步傳輸。

同樣,由1394設備發起的異步傳輸即由1394設備發出異步傳輸請求,主機進行響應。因此,這一部分主要是異步請求包的發送以及異步響應包的接收,其工作流程如圖3所示。這時會產生異步請求輸出DMA中斷,這可由鏈路層芯片中斷寄存器的reqTxComplete位表征。1394設備接收到主機發來的異步響應包后,會產生異步接收響應中斷,這可通過鏈路層芯片中斷寄存器得知。另外,發送出去的請求包也將被暫時存放在內存中,以便與返回的響應包對應。

圖3 1394設備發起的異步傳輸的工作流程

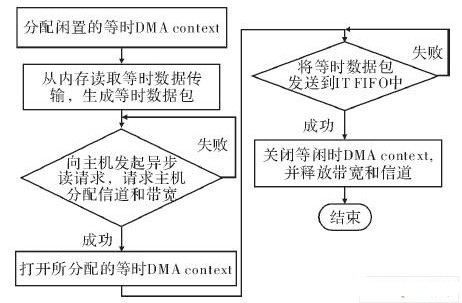

(3)等時傳輸。

等時傳輸主要實現的功能是通過1394設備將外部的視頻數據等時傳輸到主機進行實時顯示。外部視頻數據與FPGA的SPI接口相連,FPGA把接收到的數據緩存在SRAM中,等時傳輸時,FPGA讀取SRAM中的數據,生成等時數據包。這一部分的主要工作就是等時數據包的發送,其工作流程如圖4所示。

圖4 等時傳輸的工作流程

4 測試結果分析

為了測試系統性能,進行了最快傳輸速度測試。設置總線傳輸速度為800Mb·s-1,根據1394總線協議的規定,每個數據包最大為4 096 bit。理論上一個傳輸周期125μs傳送一個數據包,因此每秒最多傳輸數據31.25 Mb,轉換為比特率,最大傳輸速度為250 Mb·s-1。實測的最快傳輸速度可達227 Mb·s-1,相對于1394a理論上的最大速度125 Mb·s-1提高了較多,因此該系統在傳輸速度上具有較大優勢。同時,主機端實時顯示的視頻實時性和可靠性也較好。

5 結束語

本系統,采用800 Mb·s-1的總線傳輸速率,利用FPGA內嵌的NIOSII處理器作為控制核心,實現了雙向傳輸,用異步傳輸方式傳輸主機端指令和攝像頭方位及狀態信息,用等時傳輸方式將攝像頭數據傳輸到主機端進行實時顯示。實驗表明,相對于1394a,該方案具有高速通信、可靠性高、實時性強等優點,達到了預定目標,運行良好。本系統研究的是1394設備與主機間的通信,在此基礎上還可以研究在脫離計算機的環境下,兩個1394設備間的通信傳輸以及多個設備的組網傳輸。

-

處理器

+關注

關注

68文章

19920瀏覽量

235644 -

FPGA

+關注

關注

1646文章

22059瀏覽量

619117 -

芯片

+關注

關注

460文章

52565瀏覽量

441762

發布評論請先 登錄

基于IEEE1394b的雙向傳輸設備驅動程序設計

基于FPGA和DSP的1394b雙向數據傳輸系統

面向回路供電應用的隔離式單線雙向數據傳輸參考設計包括BOM,PCB文件及光繪文件

采用音頻接口實現數據傳輸模塊設計

如何正確實現EndDevice和Coordinator之間的數據傳輸?

采用DataSocket技術實現遠程數據傳輸設計

基于IEEEl394b總線雙向數據傳輸設備驅動程序設計

基于IEEE1394b的雙向傳輸設備驅動程序設計

基于STM32微處理器的GPRS數據傳輸技術的研究

1394b數據傳輸有什么特點?如何利用FPGA設計一個1394b雙向數據傳輸系統?

利用Fir-eAPI SDK開發IEEE1394b設備驅動程序設計

評論