1 引 言

串行通信實際上就是兩臺電子設備之間一位一位地發送和接收數據,它分為同步通信和異步通信兩類。異步串行通信無需數據時鐘、幀同步時鐘等時鐘信號,數據的發送和接收是自同步的,完全依靠收發雙方約定的傳輸波特率和數據線自身的電平變化來正確地收發數據位流,而且又因為它連線簡單,可以直接與PC機等帶異步串口的設備相連,同時它又采用RS 232電平,傳輸的距離要比同步通信的長。正因為有上述的優點,異步串行通信被廣泛應用在要進行遠距離遙測遙控的航天電子工程中。

但是,一般的處理器芯片都帶有同步串行接口,只有少數韻處理器,如TMS320F2XX、TMS320F24XX帶有速度相對較低的異步串口。為了實現那些沒有帶有異步串行接口的處理器能夠與其他設備進行異步串行通信,可以采用復雜可編程邏輯器件CPLD技術,并結合異步串行通信的協議,對異步串行通信接口電路進行設計與實現,該方法開發周期短,并且CPLD的時序嚴格,速度較快,可編程性好,還可以用于完成電子系統的其他邏輯功能的設計,如實現系統的譯碼和專門的緩沖電路。這樣一塊電路板上的外圍元器件數量就大大減少,系統的靈活性更好,調試也變得簡單的多了,同時,系統的功能模塊完成后可以先通過計算機進行仿真,再實際投入使用,降低了使用風險性。

2異步串行通信的原理

異步串行通信方式是把一個字符看作一個獨立的信息單元,并且字符出現在數據流中的相對時間是任意的,而每一個字符中的各位是以固定的時間傳送。因此這種方式在同一字符內部是同步的,而字符間是異步的。

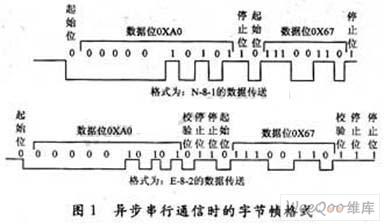

異步通信的主要特點是字符幀的傳輸格式,這樣就使得發送方可以在字符之間可根據實際的需要插入不同的時間問隔,即每一個字符的發送是隨機的。異步串行通信是以數據幀的格式傳送的,1個字符開始傳輸前,輸出線必須在邏輯上處于‘1’狀態,這稱為標識態。傳輸一開始,輸出線由標識態變為‘0’狀態,從而作為起始位。起始位后面為5~8個信息位,信息位由低到高排列,即第1位為字符的最低位,在同一傳輸系統中,信息位的數目是固定的。信息位后面為校驗位,校驗位可以按奇校驗設置,也可以按偶校驗設置,不過,校驗位也可以不設置。最后的數位為‘1’,它作為停止位,停止位可為1位、1.5位或者2位。如果傳輸完1個字符以后,立即傳輸下一個字符,那么,后一個字符的起始位便緊挨著前一個字符的停止位了,否則,輸出線又會立即進入標識態,即邏輯上處于‘1’。圖1是兩個字節0XA0和0X67被傳輸的幀的格式。

在通信中發送方和接收方之間允許沒有共同的時鐘,所以在異步通信中,收發雙方取得同步的方法是采用在字符格式中設置起始位和停止位的辦法。每一個字符傳輸前,信號線上始終為高電平,一旦開始傳送就要先傳送一個低電平的起始位,這樣接收方就開始接收數據,從而與發送方保持同步(格式上的同步)。通信雙方可按使用需要隨時改變通信協議,即改變數據位、奇偶校驗位和停止位長度和數據傳輸率。

3異步串行通訊控制器的結構設計

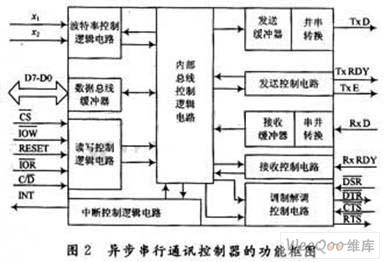

異步串行通訊控制器的內部結構可分為控制邏輯電路和寄存器組兩大部分。在控制邏輯電路中,包括波特率控制電路、讀寫控制邏輯電路、發送控制電路、接收控制電路、調制解調器控制邏輯電路、中斷控制邏輯電路和內部總線控制邏輯電路。寄存器組分為模式寄存器、控制寄存器和狀態寄存器。結構框圖如圖2所示。

該異步串行通訊控制器提供的模式寄存器和控制寄存器,用來設定奇偶校驗、傳輸速率、握手機制以及中斷。在這個設計中,提供了3種奇偶校驗選擇:不采用、奇校驗或偶校驗。傳輸速率的設定是通過向模式寄存器中設置特定的數值,來選擇波特率因子,再結合外部連入的時鐘信號就可以得出傳輸的波特率了。它們之間的關系是:時鐘頻率=波特率因子×波特率。

3.1發送數據模塊

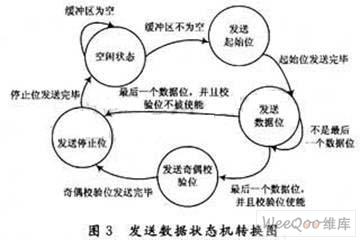

串行異步通信的發送器的實現要比接收器簡單很多。沒有數據要發送時,發送數據寄存器為空,發送器處于空閑狀態;當檢測到發送數據寄存器滿信號后,發送器開始發送起始位,同時8個數據位被并行裝入發送移位寄存器,停止位緊接著數據位指示數據幀結束。只有發送數據寄存器為空時,待發送的數據才能被裝入,在設計中用一個TxE信號來告訴CPU此時控制器的發送寄存器為空。程序中使用計數器來保證發送數據時時鐘的正確。這里使用一個狀態機描述發送過程,圖3是發送器狀態機狀態轉換示意圖。

3.2接收數據模塊

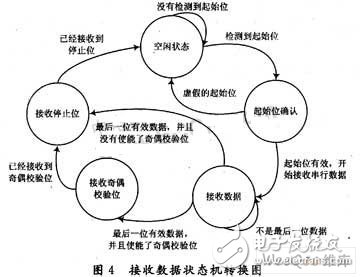

串行數據幀與接收時鐘是異步的,所以接收器功能實現中的關鍵是接收器時鐘與每個接收字符的同步。一個有效的方法是接收器采用高速率時鐘對串行數據進行采樣,通常采樣頻率是位時鐘頻率的整數倍,也就是選擇比較高的波特率因子。理論上倍數越高接收數據各位的分辨率越高,實際中一般最大選擇16倍。

接收器應該盡可能地在靠近每個數據位周期的中心處進行采樣。如果接收器能很好地預測起始位的開始,那么它可在起始位的下降沿到來之后,等待半個位周期再采樣數據位。此后,接收器每等待一個位周期采樣一個數據位,直至收到最后一位為止。

接收過程主要由一個3位狀態機實現,其狀態有空閑狀態、接收起始位、接收數據位、接收奇偶校驗位以及接收停止位。每一個狀態表明了當前正在接收到數據屬于哪一種字符,并且根據當前接收字符的狀態驅動其他部件進行合適的操作。狀態轉換機的轉換圖如圖4所示。

4基于CPLD的實現和仿真

可編程邏輯器件(PLD)是在20世紀80年代迅速發展起來的一種新型集成電路,隨著大規模集成電路的進一步發展,出現了PAL和GAL邏輯器件,而復雜可編程邏輯器件CPLD是在此邏輯器件基礎上發展起來的,它是由大量邏輯宏單元構成的。通過配置,可以將這些邏輯宏單元形成不同的硬件結構,從而構成不同的電子系統,完成不同的功能。正是CPLD的這種硬件重構的靈活性,使得設計者能夠將用硬件描述語言(如VHDL或者Veritog HDL)描述的電路在CPLD中實現。這樣一來,同一塊CPLD能實現許多完全不同的電路結構和功能。同時也大大簡化了系統的調試,從而能極大地縮短系統的研發周期。

于是我們在驗證這一環節中,采用Xilinx公司的XC9500系列的XC95108 CPLD來驗證該方案的合理性。在用VHDL語言實現圖2的功能時,采用自頂向下的設計方法,先設計一個TOP頂層模塊,它里面包括了接口控制電路模塊,調制解調模塊,發送模塊和接收模塊。其中接口控制電路模塊包含了圖2中的波特率控制邏輯電路,數據總線緩沖器和讀寫控制邏輯電路。設計實現中比較復雜的部分就是接口控制電路的實現。在接口控制電路模塊中,設計了接收緩沖寄存器(RBR),發送保持寄存器(THR),中斷使能寄存器(IER),中斷標識寄存器(IIR),模式選擇控制寄存器(LCR),調制解調控制寄存器(MCR),接收發送狀態寄存器(LSR),調制解調狀態寄存器(MSR),它們的存儲器映射地址分別設置為000~110,因為該設計中把控制器設計為不能同時接收和發送,所以接收緩沖寄存器(RBR)和發送保持寄存器(THR)共用一個地址。其中,模式選擇控制寄存器(LCR)用來設置,要發送數據的位數(從低到高發送),奇偶校驗位的位數和停止位的位數。

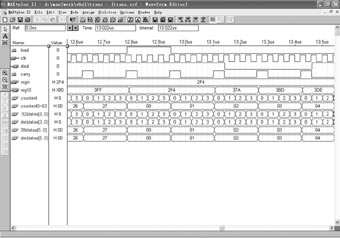

采用Xilinx公司的ISE工具發送和對接收這兩個關鍵模塊分別進行仿真,發送模塊的時序波形圖如圖5所示,接收數據模塊的時序波形圖如圖6所示。

在發送模塊的仿真測試程序中,讓CPU的數據總線連續發送55H,AAH,5AH,A5H,并在控制器的模式控制寄存器中設置發送的數據位5位,1個奇偶校驗位(偶校驗),1個停止位。在TxRDYn信號變低的時候,開始發送一幀新的數據。根據圖5中數據輸出信號Sout上信號變化的情況可以驗證該模塊設計是正確的。

在接收模塊仿真波形圖中,Sin信號是負責接收串行數據的信號線,RBR是該控制器內部的緩沖寄存器,負責存儲經過串并轉換后的數據,RxRDYn是控制器的外部信號,用來告訴CPU,控制器已經轉換完一幀數據,CPU可以把數據從緩沖寄存器中取出。中斷信號INTR會在數據傳輸完后,產生一個正脈沖。在測試接收數據模塊的文件中,使產生一個連續的AAH和56H的串行數據,在圖6中可以看到在Sin信號每接收完一個數據幀后,數據便存入RBR寄存器,RBR寄存器的數據位AAH和56H,并且在AAH傳完后,RxRDYn立即變為低電平。

5 結語

本文在對異步串行通信協議進行分析的基礎上,根據實際工程的需要,對異步串行通信控制器進行了詳細設計,并結合CPLD器件,采用VHDL語言,對設計方案進行了實現和驗證,通過最后時序仿真的波形圖得出了設計方案的正確,而且加載了該設計程序的CPLD在實際工程中能夠很好地與處理器進行連接來收發數據,從而為那些沒有串行異步接口的處理器提供一個比較理想的設計方案。(李洪威,張遂南)

-

cpld

+關注

關注

32文章

1248瀏覽量

169478 -

控制器

+關注

關注

112文章

16418瀏覽量

178791 -

vhdl

+關注

關注

30文章

817瀏覽量

128211

發布評論請先 登錄

相關推薦

利用可編程器件CPLD/FPGA實現VGA圖像控制器的設計方案

基于CPLD和FPGA的VHDL語言電路優化設計

異步串行通信接口電路的VHDL語言設計

采用CPLD/FPGA的VHDL語言電路優化原理設計

基于CPLD的GPIB控制器

基于VHDL語言和可編程邏輯器件實現Petri網邏輯控制器的設計

采用VHDL語言結合CPLD器件實現異步串行通訊控制器的設計

采用VHDL語言結合CPLD器件實現異步串行通訊控制器的設計

評論