相位差的測量在研究網(wǎng)絡(luò)特性中具有重要作用,如何快速、精確地測量相位差已成為生產(chǎn)科研中的重要課題。測量相位差的方法很多,有集成電路設(shè)計(jì)的,也有采用數(shù)字信號(hào)處理(DSP)實(shí)現(xiàn)的,現(xiàn)在普遍采用電子計(jì)數(shù)式的方法。但傳統(tǒng)的瞬時(shí)相位差計(jì),需要用鎖相環(huán)電路鎖相跟蹤被測信號(hào),廉價(jià)的低端FPGA芯片無法完成,同時(shí)被測信號(hào)的頻率范圍也限制在低頻內(nèi),為了解決上述問題,提出平均值相位差計(jì)的原理,并采用VHDL語言編程,F(xiàn)PGA芯片實(shí)現(xiàn),巧妙地簡化了鎖相跟蹤電路,擴(kuò)展了被測信號(hào)的頻率范圍,提高相位差計(jì)的性能參數(shù),也大大降低了成本,具有很高的性價(jià)比。

1 總體設(shè)計(jì)方案與基本原理

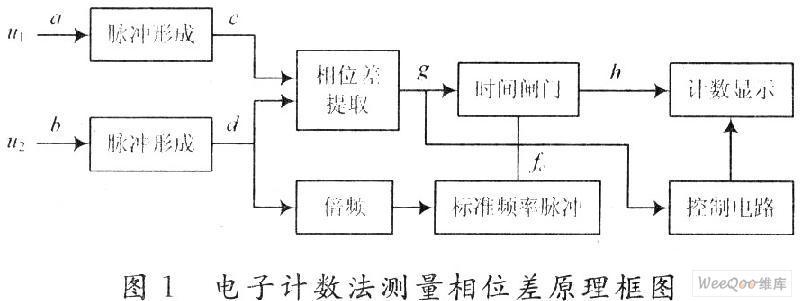

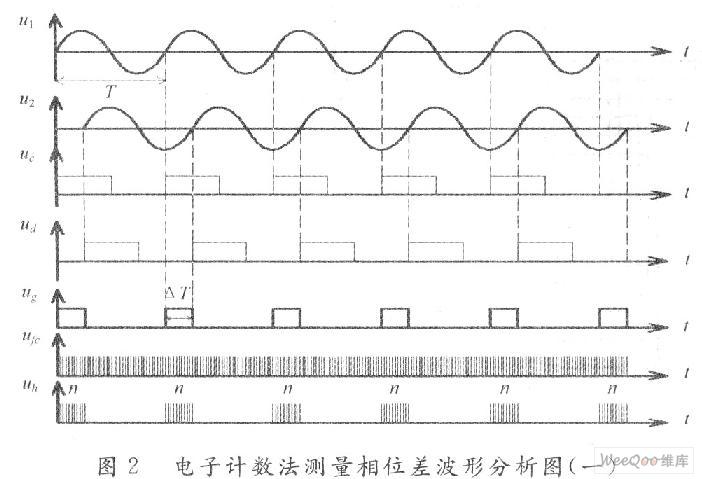

數(shù)字式相位計(jì)的基本原理如圖1所示,兩路同頻率的信號(hào)U1,U2通過脈沖形成電路,產(chǎn)生兩路過零脈沖信號(hào)U1,U2,再經(jīng)過相位差提取電路得到寬度等于兩信號(hào)相位差對應(yīng)時(shí)間寬度的信號(hào)Ug,最后通過閘門、計(jì)數(shù)、顯示就可以測量到相位差的數(shù)值。各點(diǎn)的波形分析如圖2中的U1,U2,U3,Ud,Ug,Ufc及Uf。其中:U1,U2是同頻率不同相位的兩個(gè)信號(hào);△T表示兩個(gè)同頻率正弦波過零點(diǎn)的時(shí)間差;Ufc為經(jīng)過倍頻的計(jì)數(shù)標(biāo)準(zhǔn)脈沖。設(shè)被測信號(hào)的頻率為f,信號(hào)的周期為T,若倍頻數(shù)為360×10k,則fc=360×10kf,假設(shè)在1個(gè)信號(hào)周期內(nèi)能計(jì)到的Ufc脈沖數(shù)為N,在相位差所對應(yīng)的時(shí)間△T內(nèi)計(jì)到的Uk脈沖數(shù)為n,那么N=fcT=360×10kfT=360×10k,所以相位差ψ=360△T/T=360n/N=10-bn,即計(jì)數(shù)值n的數(shù)字就代表兩信號(hào)中相位差的度數(shù);6表示小數(shù)點(diǎn)的位置。

這種測量原理,必須保持fc與f的嚴(yán)格比例關(guān)系,因此必須用到鎖相倍頻電路,若用FPGA實(shí)現(xiàn),就必須選用含鎖相環(huán)的高端芯片,成本提高;同時(shí),由于.fc=360×lOkf,若f=1 MHz,測量精度為±1°,則fc=3 600 MHz,系統(tǒng)的頻率就相當(dāng)高,目前的FPGA芯片幾乎無法實(shí)現(xiàn)。

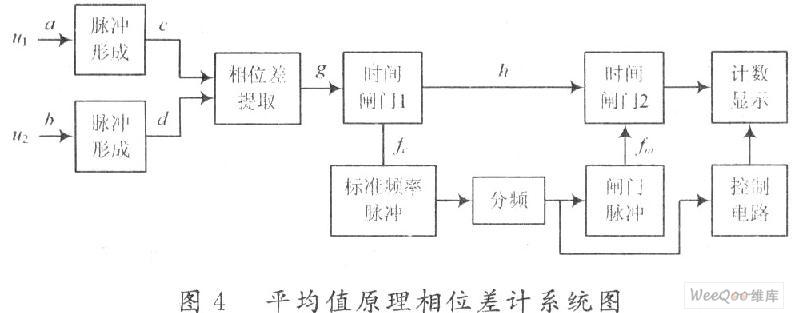

為了解決這兩個(gè)問題,利用平均值相位差計(jì)的原理,對上述測量方法進(jìn)行改進(jìn),原理如圖4所示。各點(diǎn)的波形分析如圖2和圖3所示。可以看出,就是增加了一個(gè)時(shí)間閘門2,波形分析也就是多了2個(gè)Ufm和Uj。

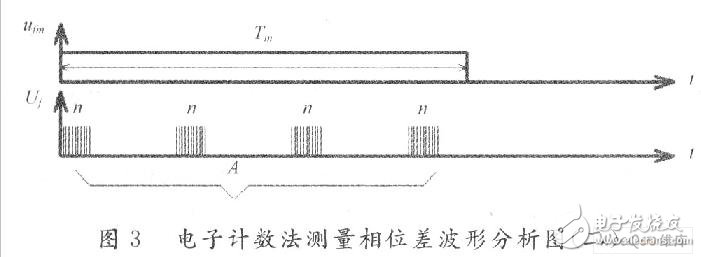

閘門脈沖發(fā)生器由晶振分頻器、閘門電路組成,它送出的波形如圖3所示。Ufm波形所示寬度為Tm的門控信號(hào)Ufm;Tm遠(yuǎn)遠(yuǎn)大于被測信號(hào)的周期Tmax,一般取Tm=kT;k是為比例系數(shù)。

這一閘門信號(hào)使時(shí)間閘門2開啟,在Tm內(nèi)通過時(shí)間閘門1的標(biāo)準(zhǔn)頻率脈沖有通過時(shí)間閘門2.得到的波形如圖3所示。

設(shè)在時(shí)間Tm內(nèi)計(jì)到的脈沖總數(shù)為A,對圖3中的Ufm及Uj點(diǎn)波形分析可知,A=kn;考慮到k=Tm/T;n=fc△T;φ=360△T/t,所以A=(Tmfc/360)φ=aφ。式中:a=Tmfc/360,若選取適當(dāng)分頻數(shù)m=fc/fm=Tmfc的值,使a=10g,φ=A×10-g,則計(jì)數(shù)值A(chǔ)的數(shù)值就是被測信號(hào)相位差的度數(shù);g表示小數(shù)點(diǎn)的位置。從上述原理分析可以看出,標(biāo)準(zhǔn)信號(hào)不必再跟蹤被測信號(hào),F(xiàn)PGA芯片就可以選用低端的,大大降低成本,同時(shí)被測信號(hào)的頻率也可以提高到系統(tǒng)頻率同一數(shù)量級,從而大大擴(kuò)大了被測信號(hào)的頻率范圍。

2 誤差分析

相位差的測量誤差主要有標(biāo)準(zhǔn)頻率誤差和量化誤差。標(biāo)準(zhǔn)頻率由晶振產(chǎn)生,誤差很小,在此主要討論量化誤差。因?yàn)棣?A×10-g,所以△φ=△A×10-g,A=kn。誤差合成理論有△A=△kn+k△n=(±1×n)+k(±1)=±(k+n)=±(△Tfc+f/fm),△A=±[(φ/360)(fc/f)+(mf/fc)]。當(dāng)被測信號(hào)的頻率f很高,接近系統(tǒng)頻率fc時(shí),k很大,n很小,△A△±k=±m(xù)f/fc;當(dāng)被測信號(hào)的頻率f很低,接近脈沖閘門信號(hào)頻率fm時(shí),k很小,n很大,△A△±n=±(φ/360)(fc/f)。例如:信號(hào)頻率若為f=10×103Hz,則系統(tǒng)頻率為fc=10×105Hz,相位差為φ=90°,分頻數(shù)m=360×103,帶入誤差公式計(jì)算得極限誤差△A=610°,△φ=610。×10-3=O.61°。

3 硬件編程及FPGA實(shí)現(xiàn)

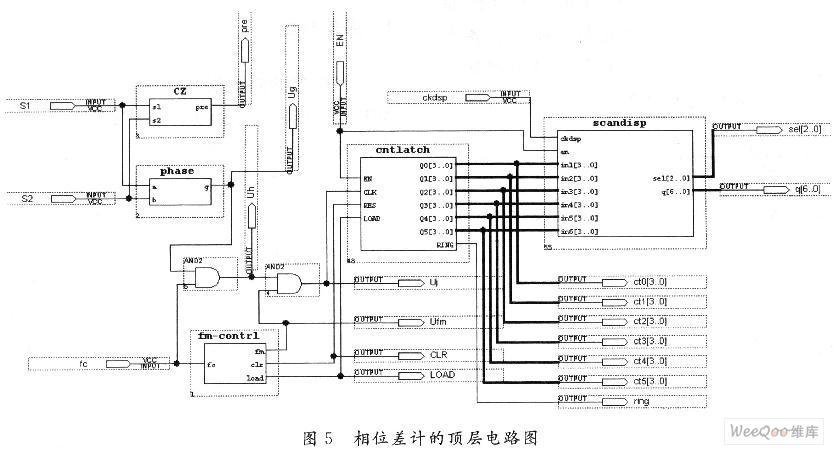

選用Atlera公司的ACEX系列的EPlK30QC208-3芯片,用VHDL進(jìn)行編程,在QrutusⅡ6.O平臺(tái)上設(shè)計(jì)的頂層電路圖如圖5所示。

頂層電路只畫出了數(shù)字部分,脈沖形成等模擬環(huán)節(jié)都是標(biāo)準(zhǔn)電路,在此不討論。數(shù)字電路部分主要包括相位超前滯后CZ模塊、相位差信號(hào)提取phase模塊、標(biāo)準(zhǔn)頻率產(chǎn)生及控制電路fm-control模塊、計(jì)數(shù)鎖存cntlatch模塊、動(dòng)態(tài)掃描及譯碼顯示scandisp模塊等環(huán)節(jié)。其中輸入端有2個(gè)同頻率,具有相位差的信號(hào)輸入端s1,s2、系統(tǒng)頻率fc、使能信號(hào)EN、動(dòng)態(tài)顯示的掃描頻率clkdisp。輸出端口有七段顯示數(shù)碼q[6..O]、顯示選擇信號(hào)sel[2..O]、計(jì)數(shù)溢出響鈴信號(hào)ring。為了方便觀察分析,還設(shè)置了一些中間信號(hào),如ct0[3..O]~ct5[3..0]是鎖存住要顯示的數(shù)字。

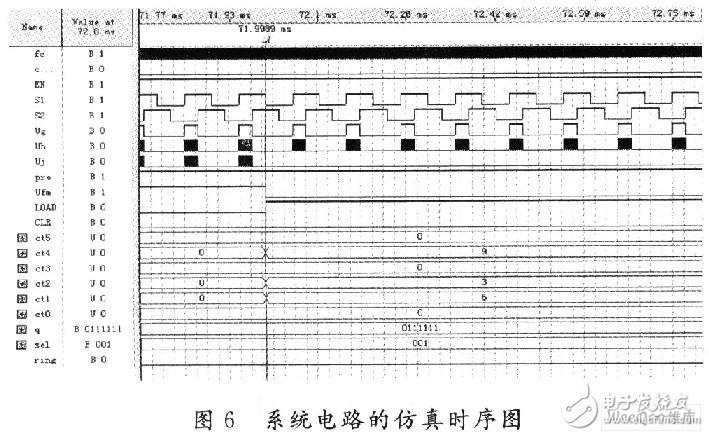

頂層系統(tǒng)電路的仿真設(shè)置如下:信號(hào)頻率若為f=10×103Hz,系統(tǒng)頻率為fc=10×106Hz,相位差為φ=90°,分頻數(shù)m=360×103。仿真結(jié)果如圖6所示。

在圖6中可以看出S1,S2是兩個(gè)有相位差90°的矩形信號(hào)。

測量線所在的位置就是fm的下降沿,計(jì)數(shù)結(jié)束,開始鎖存相位差數(shù)字ct0[3..0]~ct5[3..0],鎖存信號(hào)結(jié)束,清零信號(hào)到來,清零信號(hào)結(jié)束,下個(gè)周期從新循環(huán)開始。

pre輸出為高電平1,表明信號(hào)s1超前信號(hào)s2,鎖存的相位差數(shù)字是90.360°,與設(shè)置的相位差完全吻合,誤差也小于極限誤差。仿真表明,設(shè)計(jì)是正確完善的,能夠達(dá)到測量要求。

4 結(jié) 語

通過對平均值相位差計(jì)原理的分析和程序設(shè)計(jì)、仿真,用FPGA芯片實(shí)現(xiàn)了一個(gè)高精度、寬頻率范圍的相位差計(jì)。該測量方法的最大優(yōu)點(diǎn)是系統(tǒng)電路簡單,不需要鎖相環(huán),占用的邏輯資源少,選用低端FPGA芯片完全能滿足要求,大大提高了被測信號(hào)的頻率范圍及測量精度,具有一定的應(yīng)用價(jià)值。

-

dsp

+關(guān)注

關(guān)注

553文章

7987瀏覽量

348756 -

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603008 -

vhdl

+關(guān)注

關(guān)注

30文章

817瀏覽量

128121

發(fā)布評論請先 登錄

相關(guān)推薦

高精度相位差計(jì)的設(shè)計(jì)

有關(guān)數(shù)字相位差計(jì)的設(shè)計(jì)資料

如何使用VHDL語言設(shè)計(jì)一個(gè)系統(tǒng)用于輸出最大值、最小值和平均值

用示波器測量相位差

【干貨】如何使用示波器測量相位差

如何使用FPGA芯片實(shí)現(xiàn)相位差計(jì)的設(shè)計(jì)?

基于LabVIEW的虛擬相位差計(jì)的研制

什么是平均值? 平均值是什么意思?

相位差與相位關(guān)系、相位差的數(shù)字測量

模擬量平均值濾波是什么

RC電路中相位差是如何引起的?電路中的相位差與哪些因素有關(guān)?

使用泰克示波器觀察相位差

采用VHDL語言與FPGA芯片實(shí)現(xiàn)平均值相位差計(jì)的設(shè)計(jì)

采用VHDL語言與FPGA芯片實(shí)現(xiàn)平均值相位差計(jì)的設(shè)計(jì)

評論