Verilog HDL中,有兩種過程賦值方式,即阻塞賦值(blocking)和非阻塞賦值(nonblocking)。阻塞賦值執行時,RHS(right hand statement)估值與更新LHS(left hand statement)值一次執行完成,計算完畢,立即更新。在執行時阻塞同塊中的其他語句的執行。阻塞式(blocking)的操作符為 “ = ”。它的執行很像傳統程序設計語言。非阻塞賦值RHS估值與更新LHS值分兩步執行。在單位仿真周期開始時RHS估值,在同一單位仿真周期末更新LHS值,不阻塞同塊中其他語句的執行。非阻塞式(non-blocking)的操作符為 “ <= ”,它的執行更像并行電路,使描述電路更自然。阻塞賦值與非阻塞賦值是Verilog HDL程序設計的難點,它們既有共同點,也有差異,深入剖析其異同,對于硬件程序的開發具有重大意義。

1 Verilog 事件處理機制

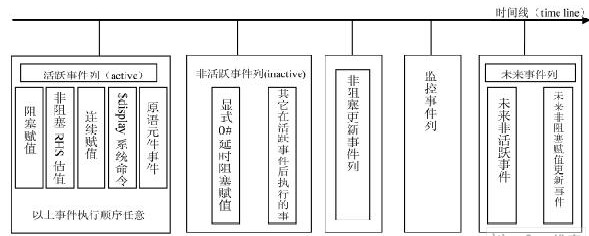

層積事件列(The Stratified Event Queue)是一個事件管理概念模型,而非硬件邏輯。模型內事件的具體實現與EDA軟件生產商的算法策略有關。在IEEE-2001中,Verilog把事件分為5個不同部分,按照時間順序如圖1所示。

觸發的任何事件可以加入到這5個事件列中的任何事件列中,但只能從活躍事件列中移出。即上面的5個事件列中的事件最后都將被激活而放入活躍事件列中。層積事件列是層次模型,層積事件列的執行順序是按優先級排列的。任何EDA軟件都只能執行活躍事件。其他事件列都按優先級級別依次激活本列事件以供執行。

1.1 活躍事件列

由圖1可見,大部分事件都被放入活躍事件列。活躍事件列里包括非阻塞賦值RHS估值。但是,非阻塞賦值的更新不是在活躍事件列,它被列成獨立的非阻塞更新事件列。活躍事件列是仿真的執行源,從一開始執行活躍事件列到活躍事件列執行完畢稱為一個仿真周期。活躍事件列中的事件可以觸發活躍或非活躍等其他事件。當活躍事件列中的所有事件執行完后,EDA軟件會按優先級依次觸發其余事件列以供仿真執行。但在當前活躍事件列中的事件執行順序是不確定的。

1.2 非活躍事件列

發生在當前仿真時間里并且在活躍事件列執行完后執行的事件列,即非活躍事件列執行優先級僅次于活躍事件列。如帶PLI例程的回調過程(tf_synchronize()、vpi_register_cb(cb_readwrite))。非活躍事件列中的事件亦可以觸發其他事件。如果觸發了優先級更高的活躍事件,非活躍事件列中的其余事件執行后移。

1.3 非阻塞賦值更新事件列

活躍事件列中的每個非阻塞賦值RHS估值,都會觸發一個與之對應的非阻塞賦值更新事件,這些事件被放在非阻塞賦值更新事件列中,執行優先級次于活躍與非活躍事件列。非阻塞賦值更新事件亦可以觸發其他事件。若在非阻塞賦值更新事件列中,存在多個對同一變量的先后賦值,只有最后一個有效,其余值將被覆蓋。

1.4 監控事件列

監控事件列被放在非阻塞賦值更新事件列后。由此可見,用監控事件列中的監控命令監控得到的值都是賦值后的值,活躍事件列$display系統命令則可以查看非阻塞更新前的值。

1.5 未來事件列

在執行事件時,如果事件含有延時,為不阻礙仿真的繼續執行,該事件將被掛起而放入未來事件列。未來事件包含未來非活躍事件和未來非阻塞賦值更新事件。

理解阻塞與非阻塞賦值就需要深入理解層積事件列,層積事件列反應了Verilog事件處理機制。

2 應用及分析

通常非阻塞賦值產生寄存器等存儲元件,對應的物理器件是帶存貯功能的元件,如寄存器、觸發器等。阻塞賦值則對應網線(wire)類型,通常與物理連線對應。這是兩種賦值方式的最明顯的差異,也是時序邏輯用非阻塞、組合邏輯用阻塞的重要原因。但這并不是絕對的,事實上阻塞賦值對應網線(wire)型,亦可對應寄存器(reg)型;阻塞賦值也能生成存貯元件,因此不能片面理解。在組合邏輯里,鎖存器可能引發測試問題,帶來隱患。說明在建模時,首先要從硬件出發來考慮問題,應先在頭腦中形成電路結構,由于賦值方式的不同,綜合結果差異甚大,運用不當很可能會導致建模失敗。阻塞賦值在時序邏輯中亦有著重要應用,在需要實時更新的組合邏輯中只有阻塞賦值能滿足要求。

以下示例代碼的功能是計算傳送過來的data中1和0的個數。

reg [5:0]count0,count1;

always @(posedge clk,negedge Rst_n)

begin

if(!Rst_n)

...

else

begin

count0 = 0; //語句1

count1 = 0; //語句2

for(i = 0;i <= 11;i = i+1)

begin

if(data[i] == 1)

count1 = count1 + 1; //語句3

else if(data[i] == 0)

count0 = count0 - 1; //語句4

else

count0 = count0 + 0; //防止生成鎖存器

end

end

end

在這段代碼里,count0、count1的值必須在每次計數之前被清零,count0、count1必須實時更新。顯然,只有阻塞賦值能滿足要求。非阻塞賦值分兩步完成,所有的更新事件在單位仿真周期末同時執行,只有最后一個值有效,所以非阻塞賦值無法完成計數任務。阻塞賦值卻能很好地勝任,因為阻塞賦值估值和更新一次性完成。

事件上,在時序邏輯中經常碰到上述實時更新問題,非阻塞賦值往往無法實現,如用阻塞賦值則可很好地解決問題。

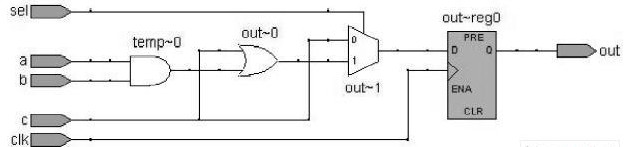

正如阻塞賦值在時序邏輯中有重要應用一樣,非阻塞賦值在組合邏輯中亦有不可替代的應用。在組合邏輯中用非阻塞賦值可以把組合邏輯改造成流水線。可執行如下所示純組合邏輯代碼,將生成純組合邏輯,綜合結果如圖2所示。

input a,b,c,clk,sel;

output out;

reg out,temp;

always @(posedge clk)

begin

temp = a & b; //語句1

if(sel)

out = temp | c; //語句2

else

out = c; //語句3

end

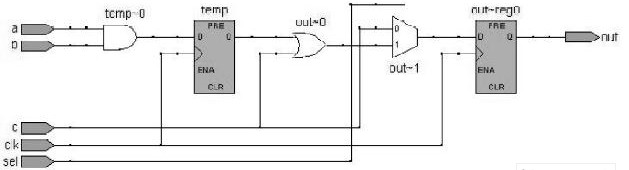

若把上面代碼中語句1、語句2、語句3阻塞賦值(" = ")改為非阻塞賦值(" <= "),則綜合結果如圖3所示。

流水線設計方法在高性能、需經常進行大規模運算的組合邏輯中可以到廣泛運用。

在組合邏輯中,如在begin、end塊中同時有許多非阻塞賦值,則它們的賦值順序是并發的。實際上它們賦予的都是上一個時鐘送入寄存器的值。這與使用同一時鐘沿觸發的許多在同一個使能控制信號下賦值完全一致,并且這種賦值因為數據保存在寄存器中,當時鐘沿到來時都已穩定,所以存入的數值是可靠的。用這種方法可以避免由組合邏輯產生的競爭冒險[2]。

在相關應用中,非阻塞賦值能較好地解決零時刻競爭冒險問題。因為非阻塞賦值分兩步完成,非阻塞賦值更新事件是在所有活躍與非活躍事件執行完之后執行,能確保所有敏感變量值在零時刻都被觸發[3]。

在同一always塊混合使用阻塞賦值與非阻塞賦值,利弊共存,混合使用的結果可能事半功倍,亦可能功虧一簣。只有了解其處理機制,深刻理解阻塞與非阻塞賦值底層實現的異同,方可靈活運用。

本文通過Verilog事件處理機制,詳細討論了阻塞與非阻塞賦值的區別、聯系及其應用示例。由本文可知,阻塞與非阻塞賦值靈活多變,底層實現也差異甚大。因而在數字電路設計時,依據預期功能,從硬件實現出發,斟酌差異,仔細選用阻塞與非阻塞賦值才能有效避免出錯,縮短開發周期。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603011 -

軟件

+關注

關注

69文章

4921瀏覽量

87403 -

eda

+關注

關注

71文章

2755瀏覽量

173205

發布評論請先 登錄

相關推薦

Verilog語言中阻塞和非阻塞賦值的不同

Verilog中阻塞賦值和非阻塞賦值的正確使用

verilog中阻塞賦值和非阻塞賦值

簡述Verilog HDL中阻塞語句和非阻塞語句的區別

通過Verilog事件處理機制實現阻塞與非阻塞賦值的區分

通過Verilog事件處理機制實現阻塞與非阻塞賦值的區分

評論