引言

當今的嵌入式系統開發人員面臨前所未有的挑戰,努力向市場推出最具競爭力的產品。

直到最近,實現的大部分系統還局限于需要大量軟件而且功耗非常高的多芯片系統或者昂貴的SoC ASIC.但是,越來越多的設計團隊感到受市場壓力以及資源限制的影響,這些方法的吸引力越來越低。而對于基于ARM 的嵌入式系統,FPGA 技術、知識產權(IP) 以及設計工具的發展促進了用戶可定制SoC FPGA 的誕生。這些器件不但克服了傳統方法的缺點,而且在嵌入式系統實現上非常獨特,具有明顯的優勢。

應用廣泛的ARM 處理器

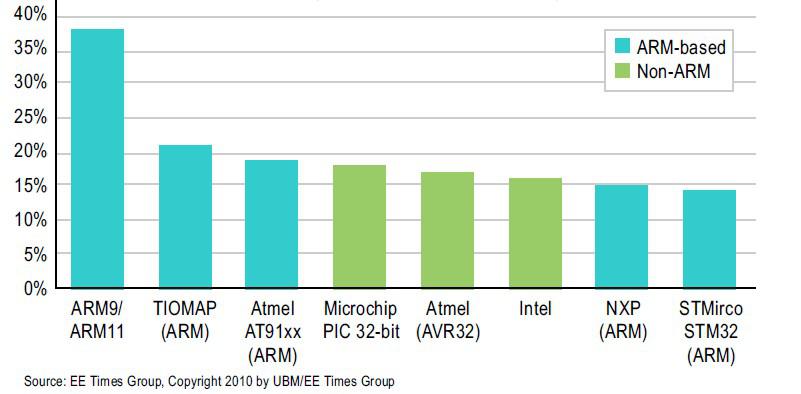

僅僅幾年前,處理器市場還是四分五裂。PowerPC、RISC、MIPS、SPARC 以及很多其他平臺都在競爭市場主導地位。但是,隨著市場的成熟,而且越來越專業化,某些平臺在一些應用領域中脫穎而出。特別是嵌入式系統應用領域的ARM ?處理器( 圖1) 尤其如此。

圖1. 嵌入式系統應用中流行的平臺

在發展迅速的嵌入式系統市場上應用非常廣泛的ARM 處理器非常適合設計人員使用。

首先,發展非常成熟的軟件、開發工具和ARM 兼容器件輔助系統實現了能夠協同工作的解決方案工具箱。其次,受迅速發展的ARM 市場規模經濟因素的影響,出現了更好、更先進的系統實現選擇。

嵌入式系統設計挑戰

與以往相比,嵌入式系統開發人員必須建立高性價比系統。迅速擴張的全球市場對設計人員的要求越來越高。但中國、印度和拉丁美洲等新興市場領域的機遇也越來越多,這些市場越來越重要,不容忽視。為滿足越來越高的用戶基本需求,需要支持各種標準和價格、性能以及特性的平臺。而且,競爭在全球展開,這對設計團隊的壓力更大,要求在越來越小的市場窗口內推出特性豐富的產品。

然而,對嵌入式產品的要求如此之高,設計團隊卻在不斷減少。經濟壓力迫使很多公司縮減規模,設計資源也由此受到影響。結果,開發團隊的規模在縮減,而工作強度卻在增大。

對成本非常關注的基于ARM 的嵌入式系統設計人員越來越明顯的感受到這一壓力,清楚的認識到傳統實現方法的缺點。多芯片解決方案實現起來相對容易一些,但是成本高,缺乏靈活性,性能/ 功耗指標達不到目前應用的需求。采用了軟核處理器的單芯片解決方案實現起來也相對容易一些,但是難以達到功耗和性能目標。ASIC SoC 具有板上硬核ARM 內核,功耗和性能表現非常出色,但是面市時間長,不靈活,對于大部分應用而言成本過高。為提高競爭力,嵌入式系統開發人員需要一種能夠幫助他們開發獨具優勢產品的解決方案,非常靈活,效率也非常高。

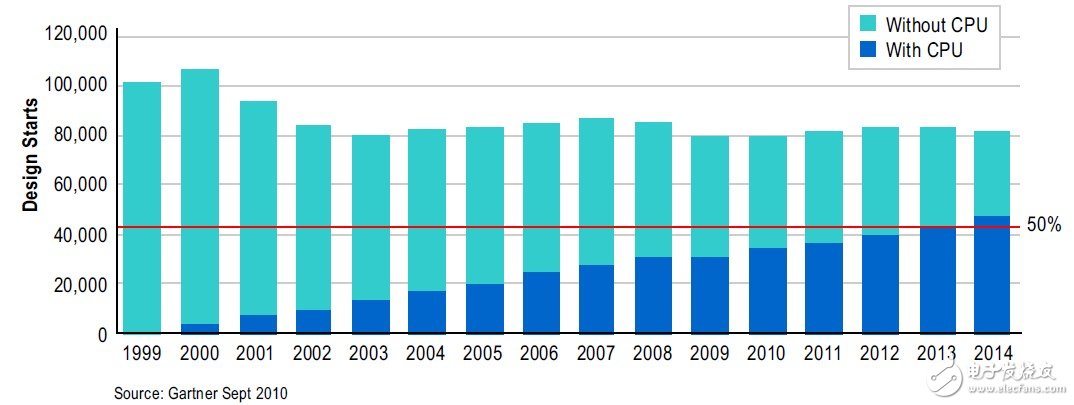

新一類SoC

在過去十年中,FPGA 內置嵌入式處理器的應用在穩步增長( 圖2)。由于Altera 在FPGA 技術上的進步,出現了新一類SoC 器件,滿足了目前嵌入式系統應用的多種功能需求。基于ARM 的SOC FPGA 在一個SoC 中結合了硬核ARM 處理器、存儲器控制器以及外設和可定制FPGA 架構。這些SoC FPGA 解決了設計人員面臨的很多難題,突出了產品優勢,價格和性能達到最優,產品能夠及時面市,延長了產品使用壽命。

圖2.FPGA 中處理器的發展

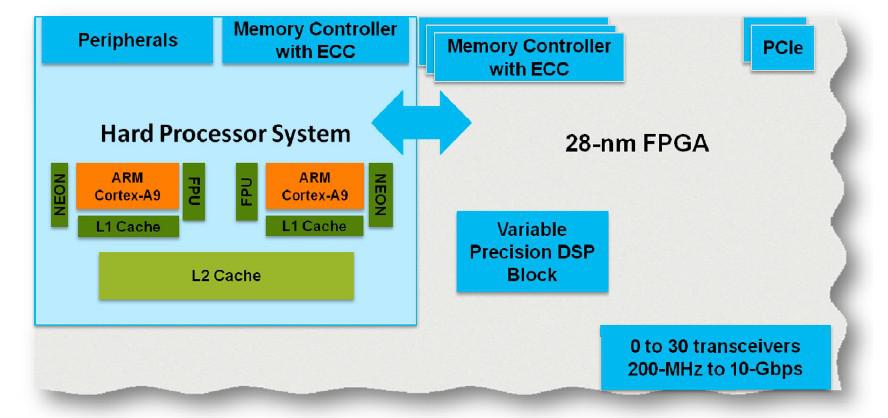

SoC FPGA

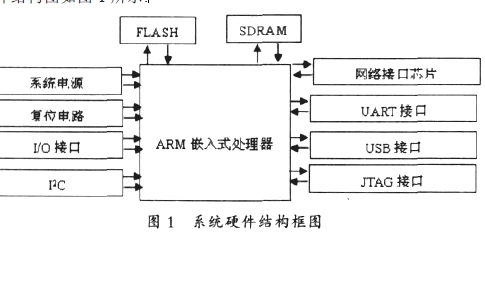

基于ARM 的SoC FPGA ( 圖3 所示) 在單片FPGA 中緊密結合了經過優化的"硬核"處理器系統(HPS) 模塊。HPS 包括雙核ARM 處理器、多端口存儲器控制器以及多個外設單元,處理器性能達到4,000 DMIPS (Dhrystones 2.1 基準測試),功耗不到1.8 W.這些硬核IP 模塊提高了性能同時降低了功耗和成本,減少了對邏輯資源的占用,突出了產品優勢。用戶可以定制片內FPGA 架構,開發專用邏輯。可編程功能支持采用新的或者修改后的通信標準和網絡協議,進一步調整性能。

圖3. 處理器與FPGA 架構緊密集成

與傳統的解決方案相比,SoC FPGA 在性能上有明顯的優勢。硬核單元相對于軟核IP 進行了很大的優化,在所采用的工藝節點上,實現了最好的性能、最低的功耗以及最高的密度。FPGA 通常是新工藝節點最先推出的器件,因此,設計人員利用SoC FPGA 能夠使用最新最好的半導體技術。而且,與基于電路板的解決方案相比,片內總線緊密連接各個單元,進一步提高了性能和功效。從系統整體角度看,SoC FPGA 明顯減小了系統體積,降低了功耗和成本。

產品更迅速面市

通過現場可編程平臺,使用現成的器件開發定制基于ARM 的SoC FPGA,其開發時間和成本只是其他定制器件的一小部分。可靠的FPGA 設計工具、直觀的系統集成工具以及成熟的ARM 輔助系統相結合,加速了開發過程,降低了風險。即使是第一次實現FPGA的設計人員,目前常用的工具支持接口格式和標準,因此,他們可以比較輕松的重新使用已有軟件、IP 和其他設計內容。使用SoC FPGA 平臺,利用開發基礎支撐條件,開發人員能夠很快抓住嵌入式系統市場的機遇。

靈活性

在嵌入式系統市場上應對競爭需要很高的靈活性。網絡和通信應用必須適應新的或者變化的標準。工業和醫療供應商不一定需要大批量產品,但是對專業化產品有很大的需求。不考慮特殊應用領域,嵌入式系統開發人員必須能夠靈活的應對激烈的競爭,利用最新的技術,很快抓住新的市場機遇。

SoC FPGA 非常適合滿足嵌入式市場需求。基于ARM 的SoC FPGA 中的邏輯部分很容易應對各種變動,適用性較強。在SoC FPGA 中,邏輯是現場可編程的,意味著很容易迅速修改,以突出產品優勢,進行更新或者重制某一產品型號。在有保證的情況下,即使設備在現場部署后,也可以進行重新配置。

可更新和設計重用

設計重用是管理成本、縮短市場窗口、提高設計資源利用率的關鍵手段。能夠在多個器件和系列中調整并重新使用設計內容,這種能力是無價的。當把現有設計或者IP 模塊應用到體積、功耗和性能需求都不同的器件上時,借助這種方法,設計人員不需要從頭開始重新進行設計。由于越來越多的設計團隊分散在世界各地,重新使用功能不但提升了效能,而且提供了共享和利用已有內容的好方法。

SoC FPGA 體系結構支持多個IP 內核,靈活的適應不同的器件系列。很多應用都有不同的價格、性能、功耗和其他限制,采用可重用和可更新內容很容易滿足這些需求。隨著工藝技術的進步,采用這類FPGA 系列,通過在下一代產品中導入IP,能夠方便的移植到下一工藝節點。

長壽命產品

對于很多應用而言,長壽命產品是要考慮的重要因素。產品生命周期,特別是醫療、工業和軍用器件,長達10 到15 年,甚至更長。但是,IC 供應商的產品一般只供應較短的時間。當這類產品的產品生命周期超過其IC 組件時,設計人員會有很大的成本代價,花費寶貴的設計資源進行設計移植,或者重制。

為避免產品過時或者失效問題的不利影響,建議需要較長產品生命周期的嵌入式系統開發人員選擇經過嚴格可靠性測試的實施方案,供應商在預期的產品生命周期內都能夠提供支持。由于其長壽命并且容易移植,工業、軍事、航空航天、汽車以及醫療應用一直在采用FPGA.長壽命器件意味著很少在現場進行產品維護,從而降低了維護成本,支持將設計資源應用到新產品上。

Altera SoC FPGA

作為2011 年啟動的"嵌入式計劃"的一部分,Altera 為嵌入式系統市場提供28-nm基于ARM 的SoC FPGA.這些Altera ?產品具有:

■ 先進的硬核ARM 處理器、外設和高速互聯。

■ 片內Altera FPGA 架構、第二個存儲器控制器以及PCI Express ? (PCIe ? ) 接口。

■ 支持已有內容和IP 集成的設計工具。

■ 采用或者不采用硅片,加速軟件開發的仿真環境。

硅片

在28-nm 工藝節點,Altera 使用了定制方法,在Arria ? V 和Cyclone ? V FPGA 系列中提供ARM 處理器,以滿足多種嵌入式應用需求。在相同的TSMC 28-nm 低功耗(28LP)工藝上生產的兩種系列產品都能夠滿足嵌入式系統的系統低功耗和低成本需求。

Altera 的Cyclone V FPGA 系列非常適合對功耗和體積要求較高的應用,而Arria VFPGA 系列在體系結構上為滿足高性能嵌入式應用而量身定制。

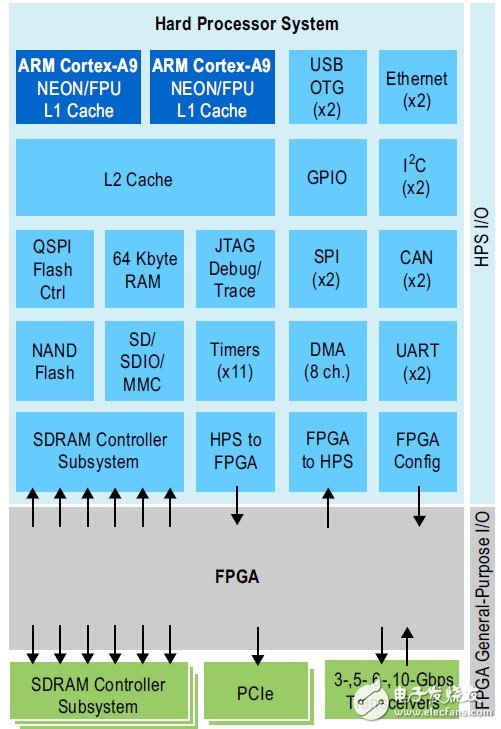

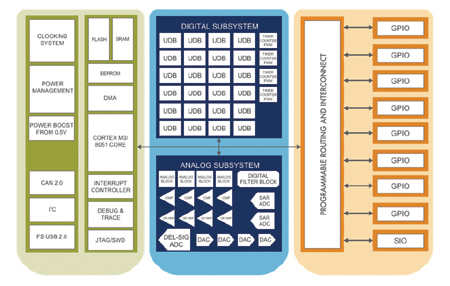

Altera ARM HPS ( 圖4) 在全功能HPS 中結合了雙核ARM Cortex ? -A9 MPCore ?處理器、存儲器控制器以及外設IP.28-nm 工藝節點的高性能雙核ARM Cortex-A9 MPCore 處理器工作速率高達800 MHz.雙核配置實現了靈活的SoC FPGA 產品,其性能能夠進一步滿足未來的需求。內置NEON ?媒體處理引擎和雙精度浮點單元為多媒體和信號處理應用提供了標準化加速功能。每個內核32 個32-KB Level-1 高速緩存,在512-KB 共享Level-2 高速緩存的支持下,通過減小延時和存儲器訪問時間,有助于提升性能。

圖4. 基于ARM 的硬核處理器系統簡介

除了ARM 內核本身,HPS 還包括SDRAM 控制器子系統、通用外設陣列,以及高速片內互聯。外設組包括增強閃存控制器、MMC、DMA、USB 2.0、以太網、UART、SPI 和GPIO 接口。最后,Altera 獨特的片內總線體系結構通過高速互聯連接了HPS 和FPGA,總帶寬大于125-Gbps.

在片內Altera FPGA 中實現了專用邏輯。由于能夠長期穩定的為Cyclone V 和Arria VFPGA 系列提供支持,Altera 產品在正常工作條件下,使用壽命一般能夠達到20 年以上。

快速系統設計工具

Altera 的Quartus ? II 開發軟件提供了高效的設計環境,幫助開發人員迅速實現基于ARM 的SoC.所包含的Qsys 系統集成工具在IP 功能和子系統之間自動生成互聯邏輯,從而顯著縮短了設計時間,減輕了設計工作量。對于使用AMBA ?等通用接口標準和協議編寫的IP,Qsys 自動識別IP,將其與SoC 連接。利用這一工具,很容易實現重用功能,在一片SoC FPGA 中同時使用已有或者第三方IP 單元以及不同的標準接口。此外,開發人員很容易利用現有的內容,迅速實現FPGA 開發。

軟件開發

軟件開發是開發嵌入式系統時非常重要的工作。出于這一原因,嵌入式軟件開發人員一般使用名為"虛擬目標"的仿真環境,在能夠使用硅片之前,編寫、仿真并調試軟件。利用Altera SoC FPGA 虛擬目標仿真環境,開發人員即使在拿到第一個硅片之前,也能夠開始寄存器和二進制兼容軟件開發。設計人員通過使用虛擬目標,提前完成大部分軟件開發工作,降低了設計風險,更迅速的將產品推向市場。

結論

與以往相比,目前的嵌入式系統開發人員必須面對激烈的競爭,迅速應對多變的標準、協議和需求,以更少的資源滿足越來越高的各種市場需求。含有硬核處理器內核的SoCFPGA 不但支持設計人員解決這些設計難題,而且還幫助他們獲得了明顯的產品及時面市、價格/ 性能、突出產品特點以及長壽命產品等優勢。與傳統方案相比,現在已經到達了一個關鍵點,基于FPGA 的SoC 成為可行而且是首選的方法,必將在市場上獲得廣泛應用。

-

FPGA

+關注

關注

1630文章

21762瀏覽量

604469 -

ARM

+關注

關注

134文章

9111瀏覽量

368122 -

控制器

+關注

關注

112文章

16406瀏覽量

178660 -

嵌入式

+關注

關注

5087文章

19149瀏覽量

306275

發布評論請先 登錄

相關推薦

基于Java平臺的可編程嵌入式系統設計

使用Java平臺怎么實現可編程嵌入式系統?

新型系統級可編程芯片設計方案

基于ARM的嵌入式系統的Altera可編程芯片系統(SoC)方法

干貨!使用嵌入式處理器對可編程邏輯器件重編程

利用嵌入式處理器對可編程邏輯器件進行重編程

采用ARM的嵌入式的可編程芯片系統的設計方案介紹

采用ARM的嵌入式的可編程芯片系統的設計方案介紹

評論