隨著信號處理技術及集成電路制造工藝的不斷發展,全數字化SPWM(正弦脈寬調制)算法在調速領域越來越受到青睞。實現SPWM控制算法的方法很多,其中模擬比較法因電路復雜、且不易與數字系統連接而很少采用;傳統的微處理器因不能滿足電機控制所要求的較高采樣頻率(≥1 kHz)而逐漸被高性能的DSP硬件系統所取代,但該系統成本高、設計復雜。與傳統方法相比,在現場可編程邏輯器件FPGA上產生一種新的SPWM控制算法,具有成本低、研發周期短、執行速度高、可擴展能力強等優點。該技術進一步推動了變頻調速技術的發展。

本文結合SPWM算法及FPGA的特點,以Actel FPGA作為控制核心,用Verilog HDL語言實現了可編程死區延時的三相六路SPWM全數字波形,并在Fushion StartKit開發板上實現了各功能模塊,通過邏輯分析儀和數字存儲示波器上驗證了SPWM波形及死區時間,為該技術進一步應用和推廣提供了一個平臺。

Actel Fushion系列器件是一款具有模擬功能的Flash架構FPGA,結合先進的Flash FPGA數字技術和模擬技術,融合了FPGA數字內核、ADC、Flash存儲器、模擬的I/O、RTC等部分。Fushion器件內部具有2 Mbit到8 Mbit不等的用戶可用的Flash存儲器;30個通道、最高12位精度、最高600 kS/s采樣率的ADC;片內100 MHz的RC振蕩器與PLL(鎖相環)共同為FPGA提供時鐘;Fushion內部40 bit的RTC除支持典型的RTC應用外,還可以控制片內1.5 V的電壓調整器以實現低功耗的睡眠和喚醒模式。這些特點極大地提高了單芯片的功能,簡化了整個系統設計,大幅度減少了電路板面積和系統的總成本。

Fushion系列AFS600內部含有用戶使用的容量為4 Mbit的Flash存儲器,內部存儲器模塊以Flash memory Block(FB)形式劃分,每個FB限制為2 Mbit的空間,用戶可以單獨使用每個FB塊,也可以自行用邏輯來級聯所有的FB塊以構建大容量的Flash存儲器。Flash 存儲器讀操作可以從FB陣列、頁面緩沖區或狀態寄存器中讀取數據。

2 數字系統電路總體設計方案

2.1 SPWM算法原理]

正弦脈寬調制技術(SPWM)是調制波為正弦波、載波為三角波或鋸齒波的一種脈寬調制法,是現代變頻調速系統中應用最為廣泛的脈寬調制方式,目前有自然采樣法、規則采樣法、等面積法等。其中規則采樣法計算簡單,但諧波含量較大;一種改進的等面積法諧波含量低,但計算復雜,不利于系統實現;自然采樣法是在正弦波和三角波的自然交點時刻控制功率開關器件的通斷,是最理想的采樣方法。

本文采用等腰三角波和三路相差120°的正弦波比較生成SPWM波,在Fushion StartKit開發板上采用自然采樣法,結合數字頻率合成技術DDS,生成死區延時可調的SPWM全數字波形。

2.2 數字系統電路總體方案設計

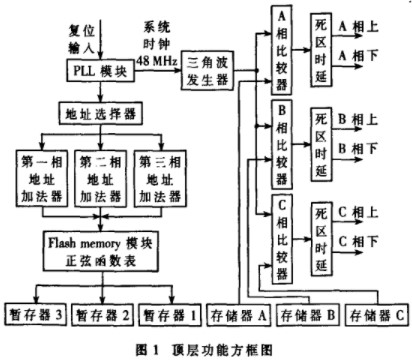

Verilog HDL硬件描述語言具有很好的易讀性和可重用性,結合Verilog HDL硬件描述語言設計規范及SPWM工作機理,用自頂向下的分割方法對整個系統進行總體方案設計。首先從系統設計入手,在頂層進行功能方框圖的劃分和結構設計。系統頂層功能方框圖如圖1所示。

根據頂層設計的思想,采用Verilog HDL語言分別實現各個模塊的設計,最后把各個模塊嵌入到頂層模塊中,使各個模塊有機地組成一個完整的整體。

3 系統模塊的設計與實現

3.1 直接數字頻率合成模塊[8]

直接數字頻率合成DDS是采用數字化技術,通過控制頻率控制字直接產生所需的各種不同頻率信號,突破了模擬頻率合成法的原理,從“相位”的概念出發進行頻率合成。這種合成方法不僅可以給出不同頻率的正弦波,而且還可以給出不同初始相位的正弦波,甚至可以給出各種任意波形。電路一般包括基準時鐘、頻率累加器、相位累加器、幅度/相位轉換電路、D/A 轉換器。在設計中,將要輸出的波形數據(如正弦函數表)預先存在ROM(或RAM)單元中,然后在系統標準時鐘頻率下,按照一定的順序從ROM(或RAM)單元中讀出數據,再進行D/A轉換,就可以得到一定頻率的輸出波形。本設計直接利用從Flash存儲器的存儲單元中讀出的離散正弦函數值與生成的三角波進行比較,實現系統的全數字化要求。

3.2 三角波產生模塊

本模塊采用同步三角波調制方法,利用可逆計數器對輸入時鐘進行計數。計數器先執行加法,從0計數到255,再執行減法計數從255到0,從而形成三角載波。如此反復就可以得到峰峰值255連續的三角波形。輸入時鐘是系統時鐘通過鎖相環輸出的1 MHz的時鐘。

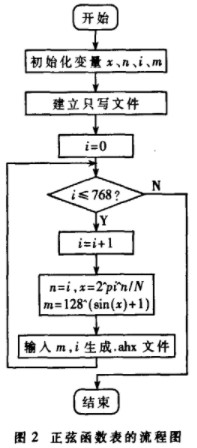

3.3 建立正弦函數表

三角波的幅值范圍在0~255,而正弦波的幅值在-1~+1之間,為了實現等幅值比較,將正弦波上移一個單位后,再將所有值同乘以128,使正弦波的幅值也在0~255之間。即:

m=128×(sin(x)+1) (1)

式(1)用C語言對此函數在一個周期(0~2π)內完成768個量化并且直接生成Flash存儲器的初始化文件(.ahx)格式,再用SmartGen輸入將Flash 存儲器配置成常用的數據存儲器,將預先生成的.ahx文件導入生成data Storage宏模塊,就建立了正弦函數表。生成正弦函數表的流程圖如圖2所示。

3.4 三相正弦波產生和輸出模塊

FPGA的Fushion芯片理論上可以實現任何方式的數學運算邏輯,但由于芯片的容量限制,并不是任何計算都能實現的。因此需事先將正弦函數離散并加載到FPGA的Flash存儲器中,在正弦調制波的離散過程中即可將一個周期完整地離散。因此,只對其中A相進行離散化處理,數據存儲在Flash存儲器中,每個數據分配1個地址。即可以利用計數器來產生取正弦波數據的地址,通過數字頻率合成技術改變計數器的計數頻率就可以改變正弦波的頻率。這樣即可先輸出一路的正弦波,另外兩路正弦波產生的方法與此類似,只是起始取數據的地址相差120°,即分別從第256和第512個數據開始取數。

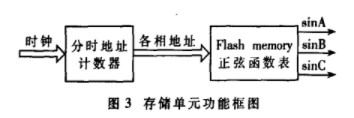

為了在每個調制波周期查找正弦函數表以及分別與載波進行比較,在設計中采用時分復用技術。即依據三相關系,由一個地址計數器,通過基本量加1轉移到另一地址計數器中,并且在跳轉過程中,這一地址計數器加1指向下一單元,從而分時取出三相地址單元的內容。利用對正弦表尋址的高速度,使一個正弦表在不同時間段查詢不同相的正弦波的幅值,以達到減少正弦表所占用的FPGA資源的目的。這樣就大大減少了邏輯數目,僅增加了地址選擇器和三個同步存儲器,實現了正弦函數表的復用,在很大程度上節省了芯片的資源。

電路的具體實現:相位互差120°的三路地址數據并行輸入,通過一個三選一的選擇器進行選擇,選擇器的控制端接三進制的計數器。如計數器為0時,輸出A相地址,取出A相正弦值;為1時,輸出B相地址,取出B相正弦值;為2時,輸出C相地址,取出C相正弦值。因此只要使輸入的三相地址周期性變化,就可實現并行輸入的三相地址數據在時間上的連續,也就實現了三相地址數據的合成。其存儲單元功能框圖如圖3。這樣就可以利用一個正弦表來得到三相的正弦值,達到減少正弦表占用FPGA資源的目的。

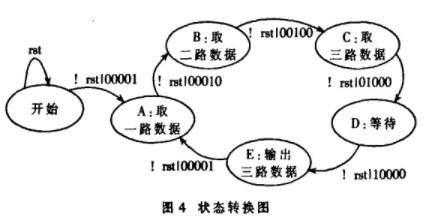

查表時每次只能輸出一相的數據,所以每次產生的數據需利用寄存器先暫存一下。首先輸出A相,通過暫存器l存入到A相存儲器;接著輸出B相,利用暫存器2存入到B相存儲器;最后輸出C相,利用暫存器3存入到C相存儲器中。這樣,三相正弦波數據都存儲在各自的存儲器中,這三個寄存器采用同步控制信號,當控制信號觸發時,同時輸出三相的正弦波數據用于后面的比較。該部分用狀態機實現,其狀態轉換圖如圖4所示。

其部分程序代碼如下:

case(state1)

A: //初始化狀態

begin

ADDRES1《=addr1; //時分復用第一路地址

READ_EN《=1′b1; //讀使能開

NEXT《=1′b1; //開啟預讀模式

if(addr1==18‘d767) //生成地址

addr1《=18’d0;

else if (!BUSY) //如不忙狀態開始讀

begin

addr1《=addr1+18′d1;//地址自增

out0《=DATAOUT; //數據暫存

state1《=B; //取第二路數據地址

end

end

B: //取第二路數據

begin

ADDRES1《=addr2; //時分復用第二路地址

READ_EN《=1′b1;

NEXT《=1′b1;

if(addr2==18′d767)

addr2《=18′d0;

else if (!BUSY)

begin

addr2《=addr2+18′d1;

out1《=DATAOUT;

state1《=C;

end

end

C: //取第三路數據

begin

ADDRES1《=addr3; //時分復用第三路地址

READ_EN《=1′b1;

NEXT《=1′b1;

if(addr3==18′d767)

addr3《=18′d0;

else if (!BUSY)

begin

addr3《=addr3+18′d1;

out2《=DATAOUT;

state1《=D;

end

end

D: //空操作狀態

begin

state1《=E;

end

E: //數據存儲,同時取出三路數據

begin

outdata0《=out0;

outdata1《=out1;

outdata2《=out2;

state1《=A;

end

endcase

3.5 三角波與正弦波比較控制模塊

該模塊用于輸出三相六路SPWM脈沖序列。用模塊1中輸出的三角波分別與模塊4輸出的三相正弦波相比較,從而先得到三路SPWM脈沖序列。當正弦波數據大于三角波數據時,輸出高電平;反之,輸出低電平。每相輸出又分為互補的兩路輸出,利用一個逆變器對輸入波形取反,就可以得到與SPWM脈沖序列互補的波形。

其部分程序代碼如下:

always@(outdata0 or outdata1 or outdata2 or out2)//比較器

begin

if(outdata0》out2)

outdata4=1;

else outdata4=0;

if(outdata1》out2)

outdata5=1;

else outdata5=0;

if(outdata2》out2)

outdata6=1;

else outdata6=0;

end

3.6 時延控制死區輸出模塊

對于SPWM三相橋式逆變器,由于開關管固有開關時間Ts的影響,開通時間Ton往往小于關斷時間Tof,因此容易發生同臂兩只開關管同時導通的短路故障。為了避免這種故障的發生,通常要設置開關死區ΔT,以保證同橋臂上的一只開關管可靠關斷后,另一只開關管才能開通。死區的設置方式有兩種:一種是提前關斷、延時開通的雙邊對稱設置;另一種是按時關斷、延滯Δt開通的單邊不對稱設置。根據FPGA的編程特點,選擇了按時關斷、延滯Δt開通的單邊不對稱設置,并且時延死區的調節與控制與時延控制死區模塊的輸入時鐘clk有關。

根據延時模塊中延時信息:Δt=2×Tclk

clk是鎖相環輸出時鐘CLK 1 MHz(本文采用的是1 MHz)的2次分頻得到的時鐘,只要改變頂層模塊中對CLK 1 MHz的分頻系數,就可以精確控制延滯Δt的大小,本文計算值Δt=4μs。

另外,死區調節單元還能消除由于FPGA器件本身時延造成的毛刺。其部分死區控制程序代碼如下:

always@(posedge clk or posedge rst)

begin

if(rst) //異步復位

begin //初始化寄存器

q《=0;

q0《=0;

end

else

begin //延時輸出的D觸發器

if(d)

begin

q0《=1′b1;

q《=q0;

end

else

begin //立即清零

q《=0;

q0《=0;

end

end

end

有關clk生成與調節的程序代碼如下:

always@(posedge CLK1M or posedge rst) //分頻產生時延控制時鐘

begin

if(rst) //異步復位

begin

clk《=0; //時鐘初始狀態清零

couter《=0; //計數初值設置零

end

else

begin

if(couter==2′b01)

begin

clk《=~clk;

couter《=0;

end

else

couter《=couter+1′b1; //計數器加1

end

end

3.7 時鐘輸出控制模塊

FushionAFS600器件的系統時鐘是48 MHz,因本設計正弦波的掃描頻率和三角波的掃描頻率預設為1 MHz,為減少時鐘輸出模塊的數量以及能方便更改系統輸出SPWM波形的占空比和頻率,本設計充分利用Fushion器件的時鐘調整電路,用SmartGen生成一個靜態PLL宏模塊,把系統時鐘分頻成1 MHz的時鐘分別是CLK 1 M和CLK 2 M,并連接到全局網絡上。當需要一定頻率和不同占空比的SPWM脈沖時,只需計算出載波和調制波形的掃描頻率,而后直接在SmartGen宏模塊中修改靜態PLL輸出時鐘,就可實現輸出SPWM波形密度的控制與調節,從而滿足各種工作頻率的需求。

4 基于FPGA的SPWM實現及系統測試

4.1 SPWM控制技術的FPGA實現

根據頂層功能圖(如圖1),分別用Verilog HDL語言和SmartGen輸入描述了各個功能單元模塊,并分別在Libero 8.1集成開發環境下通過編譯和仿真驗證。最后用Verilog HDL語言編寫一個頂層模塊實現各個功能模塊的有機組合,以實現總體功能,再在Libero 8.1集成開發環境下進行編譯、邏輯綜合、布局布線后下載到目標器件Fushion AFS600器件FPGA上,實現了三相六路可控SPWM全數字算法的片上系統。

4.2 系統測試結果

圖5是從邏輯分析儀上對系統測試的結果。從圖中可以看出所設計電路完全符合功能要求,且觀測到的時延死區時間均為4 μs,與理論計算值一致。下載后觀測與功能仿真,布局布線后仿真圖形也都完全一樣,達到了設計的預期要求。

圖5 邏輯分析儀測試時序結果

-

FPGA

+關注

關注

1630文章

21791瀏覽量

605092 -

微處理器

+關注

關注

11文章

2273瀏覽量

82644 -

DDS

+關注

關注

21文章

636瀏覽量

152834

發布評論請先 登錄

相關推薦

Verilog HDL語言在FPGA/CPLD開發中的應用

采用Verilog HDL語言與DDS技術實現SPWM控制算法的FPGA設計

采用Verilog HDL語言與DDS技術實現SPWM控制算法的FPGA設計

評論