引 言

System on Chip的縮寫,稱為系統級芯片,也有稱片上系統,意指它是一個產品,是一個有專用目標的集成電路,其中包含完整系統并有嵌入軟件的全部內容。 它是信息系統核心的芯片集成,是將系統關鍵部件集成在一塊芯片上;從廣義角度講, SoC是一個微小型系統,如果說中央處理器(CPU)是大腦,那么SoC就是包括大腦、心臟、眼睛和手的系統。國內外學術界一般傾向將SoC定義為將微處理器、模擬IP核、數字IP核和存儲器(或片外存儲控制接口)集成在單一芯片上,它通常是客戶定制的,或是面向特定用途的標準產品。 集成電路的發展已有40年的歷史,它一直遵循摩爾所指示的規律推進,現已進入深亞微米階段。由于信息市場的需求和微電子自身的發展,引發了以微細加工(集成電路特征尺寸不斷縮小)為主要特征的多種工藝集成技術和面向應用的系統級芯片的發展。隨著半導體產業進入超深亞微米乃至納米加工時代,在單一集成電路芯片上就可以實現一個復雜的電子系統,諸如手機芯片、數字電視芯片、DVD 芯片等。在未來幾年內,上億個晶體管、幾千萬個邏輯門都可望在單一芯片上實現。 SoC設計技術始于20世紀90年代中期,隨著半導體工藝技術的發展,IC設計者能夠將愈來愈復雜的功能集成到單硅片上, SoC正是在集成電路( IC)向集成系統( IS)轉變的大方向下產生的。1994年Motorola發布的FlexCore系統(用來制作基于68000和PowerPC的定制微處理器)和1995年LSILogic公司為Sony公司設計的SoC,可能是基于IP核完成SoC設計的最早報導。由于SoC可以充分利用已有的設計積累,顯著地提高了ASIC的設計能力,因此發展非常迅速,引起了工業界和學術界的關注。

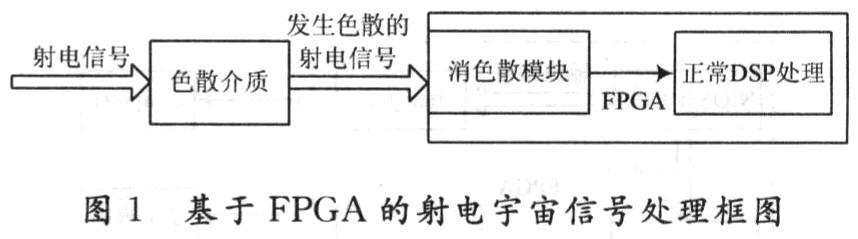

l 系統總體設計

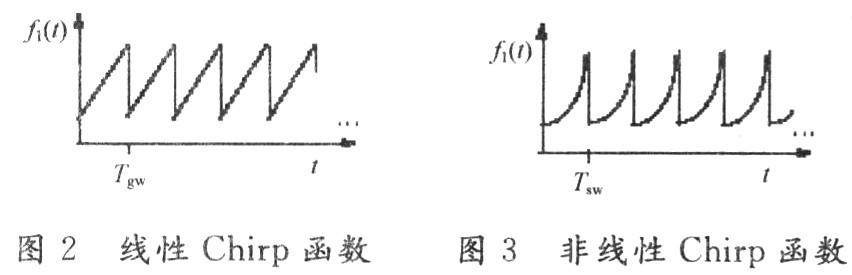

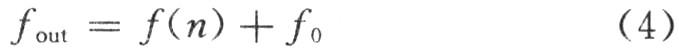

該設計是基于SoPC技術設計的Chirp函數信號發生器,該系統把微處理器模塊和DDS模塊集成到單片FPGA芯片內部,通過在嵌入式操作系統μC/OS-Ⅱ編寫的程序,實時控制微處理器對DDS的控制字輸出,DDS模塊根據頻率控制字的不同,輸出不同的數字化正弦波。使之符合Chirp函數的時變頻率特征。Chirp函數根據輸出頻率的遞變規律一般分為兩種:線性Chirp函數和非線性Chirp函數,以下是兩種Chirp函數在頻域上的表現圖如圖2,圖3所示。

從圖2,圖3可以看出Chirp函數的頻率輸出與時間的f-t關系可以總結為:

(1)對于線性Chirp函數

在連續域時間域內有關系式:

式中:k為常數;f0為初始輸出頻率;t為連續時間。

在離散時間域有關系式:

式中:k為常數;f0為初始輸出頻率;n為采樣點。

(2)對于非線性Chirp函數

在連續域時間域內有關系式:

式中:f為非線性函數;f0為初始輸出頻率;t為連續時間。

在離散時間域有關系式:

式中:f為非線性函數;f0為初始輸出頻率;n為采樣點。

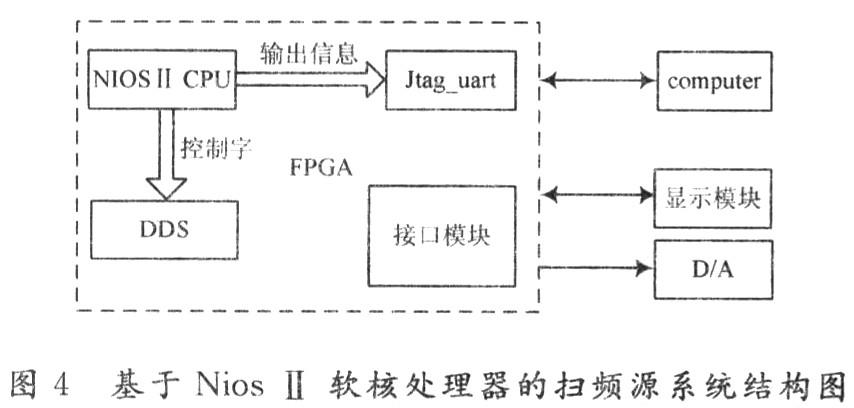

因此該Chirp信號源的功能是:在NiosⅡ中建立的微控制器;使用嵌入式操作系統μC/OS-Ⅱ建立對DDS頻率控制字輸出實時改變的任務;根據線性和非線性Chirp函數的特點控制字的輸出根據需要線性或者非線性輸出,并且在此設計中將該任務的優先級設置為最高。利用VHDL語言編寫DDS模塊,首先根據Matlab計算出需要的正弦數據,然后將這些數據存儲于ROM中供DDS模塊調用,具體結構如圖4所示。

2 DDS模塊的設計

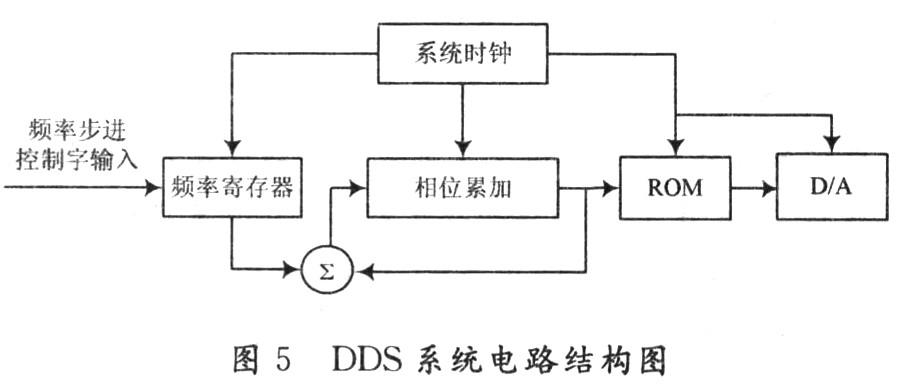

一塊DDS芯片中主要包括頻率控制寄存器、高速相位累加器和正弦計算器三個部分(如Q2220)。頻率控制寄存器可以串行或并行的方式裝載并寄存用戶輸入的頻率控制碼;而相位累加器根據頻率控制碼在每個時鐘周期內進行相位累加,得到一個相位值;正弦計算器則對該相位值計算數字化正弦波幅度(芯片一般通過查表得到)。DDS芯片輸出的一般是數字化的正弦波,因此還需經過高速D/A轉換器和低通濾波器才能得到一個可用的模擬頻率信號。在各行各業的測試應用中,信號源扮演著極為重要的作用。但信號源具有許多不同的類型,不同類型的信號源在功能和特性上各不相同,分別適用于許多不同的應用。目前,最常見的信號源類型包括任意波形發生器,函數發生器,RF信號源,以及基本的模擬輸出模塊。信號源中采用DDS技術在當前的測試測量行業已經逐漸稱為一種主流的做法。

數字式頻率合成器(DDS)模塊的工作原理是:將O~2π的正弦函數值分為N份,將各點的幅度值存入ROM中,再用一個相位累加器每次累加相位值ωT,得到當前的相位值,通過查找ROM得到當前的幅度值。其系統框如圖5所示。

DDS的幾個主要參數是:系統時鐘頻率,頻率控制字長,頻率分辨率,ROM單元數,ROM字長。該設計的DDS是32位的,時鐘頻率為50 MHz,頻率控制字長為32位,ROM單元數為2的11次方,ROM字長為16位。而且有如下關系:

頻率分辨率=系統時鐘頻率/232;

頻率控制字(FTW)=f×232/T;

其中:f為要合成的頻率;T為系統時鐘。

DDS的工作過程為:每次時鐘的上升沿到來時,相位累加器(32位)中的值累加上頻率寄存器(32位)中的值,再利用累加器的高11位作為地址進行ROM查表,輸出相應的幅值數字信號。

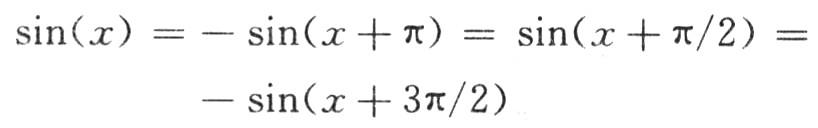

如果是掃頻工作,只需要根據一定的規律實時修改頻率控制字,就可以達到掃頻輸出的目的。但是該系統的性能受到以下兩個方面的制約:ROM單元數和ROM數值的有限字長。由于ROM大小的限制,ROM的單元地址位數一般都遠小于相位累加器的位數,這樣只能取相位累加器的高位作為ROM的地址進行查詢,這就相當于引入了一個相位誤差。為了解決ROM的受限問題,該設計采用ROM壓縮技術。因為正弦函數存在對稱和反轉特性,即:

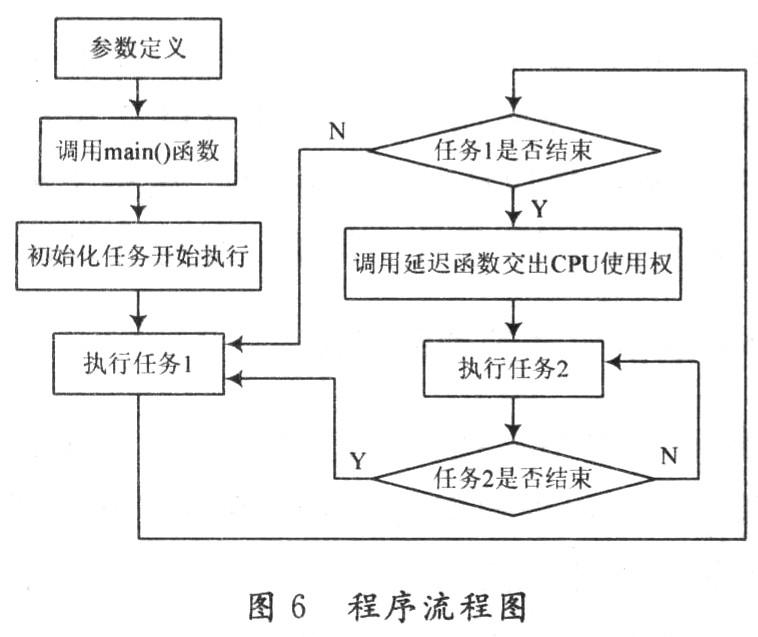

對于O~2兀的幅度值,可以只存儲O~π/2的部分。這樣原本需要的2的11次方個單元的ROM現在只需要2的9次方個單元的ROM就可以實現。在MatIab中產生16位512點的O~π/2正弦波數據的命令如下:

將Y數據依次存入Altera公司提供的Megawiz-ard宏單元實現的ROM中即可。

3 嵌入式微處理器的實現

嵌入式微控制器的典型代表是單片機(Microcontroller Unit),這種8位(8根數據線,8位指令)的電子器件目前在嵌入式設備中仍然有著極其廣泛的應用。微控制器的最大特點是單片化,體積大大減小,從而使功耗和成本下降、可靠性提高。嵌入式微處理器的設計包括3個部分:利用SoPCBuilder定制的軟核CPU,在QuartusⅡ環境下設計的電路和NiosⅡ編程。

本設計的軟核CPU采用NiosⅡ/S標準型內核,帶有16 KB的Cache;集成了外部的FLASH和SDRAM控制器用于保存程序數據;Jtag_Hart電腦開發板傳輸接口用于建立良好的用戶交互接口使用戶能在console界面上觀察程序運行情況;兩個位寬分別為8位和3位的輸出口作為輸出DDS模塊的控制字。

NiosⅡ的編程主要是基于嵌入式操作系統μC/OS-Ⅱ,μC/OS-Ⅱ是一個完整的、可移植、固化和剪裁的占先式實時多任務核(Kernel)。從1992年發布至今,μC/OS-Ⅱ已經有了上百個的商業應用案例,在40多種處理器上成功移植。

μC/OS-Ⅱ提供以下系統服務:任務管理(TaskManagement);事件標志(Event Flag);消息傳遞(Message Passing);內存管理(Memory Management);信號量(Semaphores);時間管理(Time Management)。

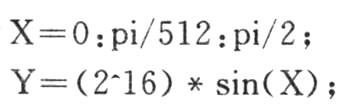

在該設計中建立一個主函數和兩個任務函數,主函數的功能:調用系統任務初始化函數OSTaskCreateExt()初始化兩個任務函數:調用系統開始函數OSStart()啟動系統開始工作。

任務1:實時的改變DDS控制字的輸出,并且保持一段時間,在遍歷完所有的需要頻率以后,延遲調用系統延遲函數OSTimeDlyHMSM(),延遲63 s將該使用權交付給任務2。

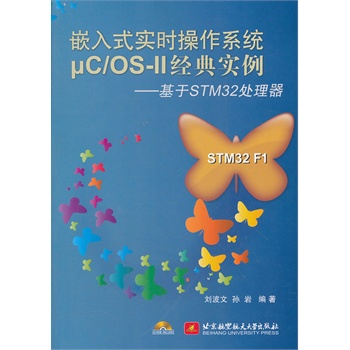

任務2:為了保證該系統以后能有功能擴展,建立一個任務,其僅僅是通過函Jtag_uart接口使用函數printf(),向電腦發送一個任務2已經開始工作的提示信息,如果以后需要擴展功能則只需修改任務2即可。程序的具體流程圖如圖6所示。

在任務1中實時改變變量i的值步進為1,通過定義的Chirp函數關于時間和輸出頻率控制字之間的關系函數function(),計算得到此時的頻率控制字f,并且將f的值通過API函數IOWR_ALTERA_AVALON_PIO_DATA()從I/O端口輸出以控制DDS,然后延遲2 s使DDS保持該輸出頻率一段時間,并且通過Jtag_uart端口在Console調試界面向用戶提示當前的信號源的輸出頻率,程序如下:

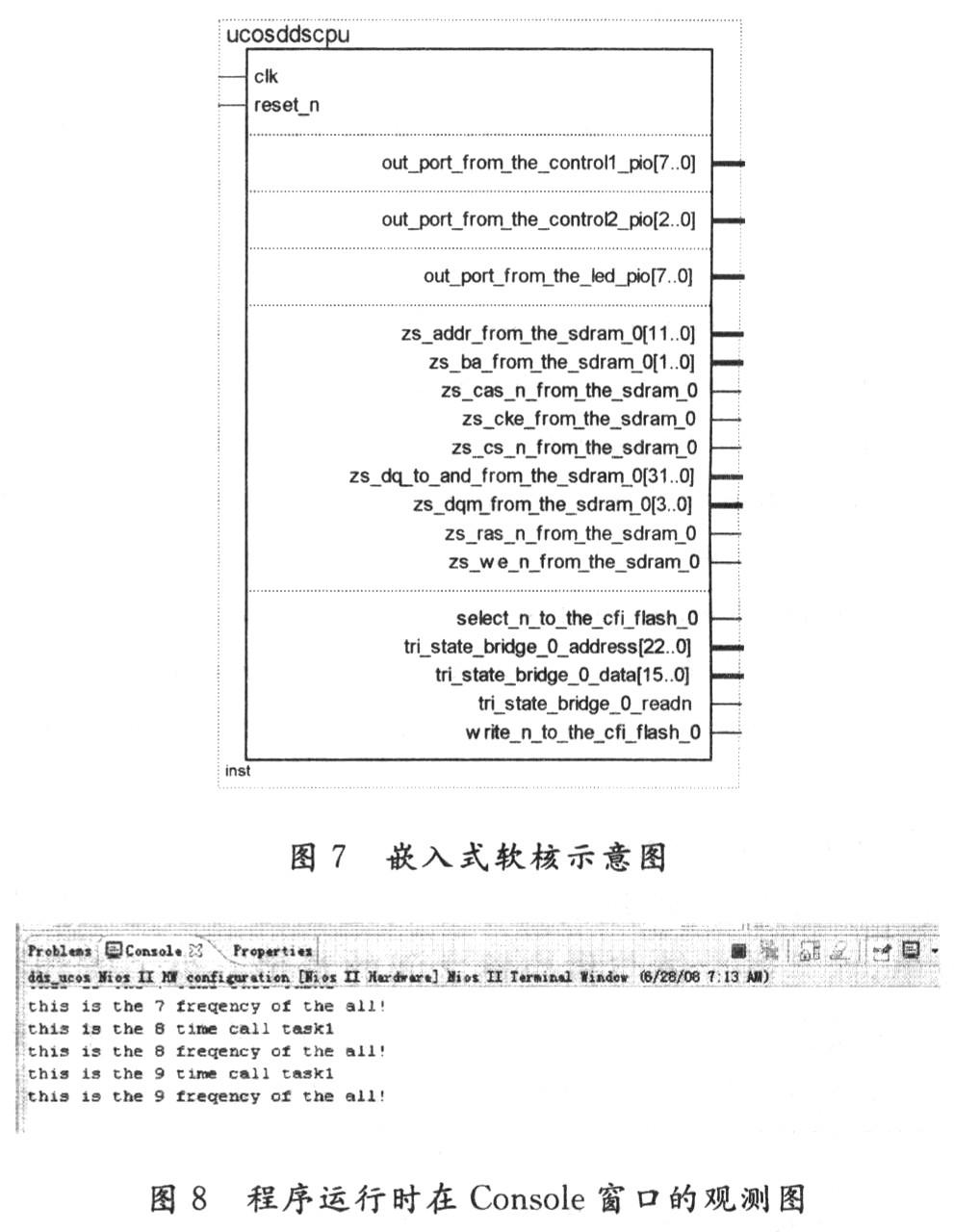

圖7為QuartusⅡ中生成的嵌入式軟核示意圖。

4 結 語

該設計在21controll公司提供的V4.O FPGA/SoPC開發學習套件上面通過仿真驗證,該套件的核心芯片為CycloneⅡ系列:EP2C20F484C8,其具有18 752個邏輯單元(LE)和52個M4K RAM塊,能夠很好地設計存儲需要的數據,完全符合設計要求。

-

嵌入式

+關注

關注

5086文章

19140瀏覽量

305865 -

操作系統

+關注

關注

37文章

6838瀏覽量

123396 -

信號發生器

+關注

關注

28文章

1476瀏覽量

108809

發布評論請先 登錄

相關推薦

ARM與C/OS-Ⅱ嵌入式系統設計與實例開發

嵌入式實時操作系統μC/OS-Ⅱ在LPC1788上的移植及應用

基于嵌入式操作系統μC/OS-Ⅱ的Chirp函數信號發生器設計

基于嵌入式操作系統μC/OS-Ⅱ的Chirp函數信號發生器設計

評論