現代模擬仿真技術廣泛應用在系統設計、系統分析以及教育訓練中。在模擬過程中,存在大量向前端模擬裝置或仿真模塊發送指令數據,以及從模擬工作設備上讀取狀態參量的情況。在對大型工業設備和系統進行模擬仿真時,數據采集控制的復雜程度愈加惡劣。通過改進數據采集控制器的結構,提高數據采集控制器的自動化和集成化程度,可以有效地提高大型模擬仿真設備數據采集和控制的效率。

FPGA及SoPC技術的發展為此提供了新的解決方案。IP核(IP Core)是具有特定電路功能的硬件描述語言程序,可較方便地進行修改和定制,以提高設計效率。本文研究了基于FPGA的數據采集控制器IP 核的設計方案和實現方法,該IP核既可以應用在獨立IC芯片上,還可作為合成系統的子模塊直接調用,實現IP核的復用。

1 系統結構

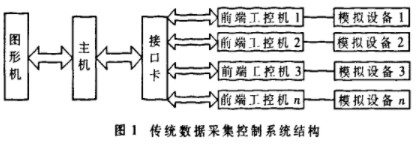

數據采集控制器主要分為發送機制和接收機制兩部分。在傳統的模擬仿真系統中,發送機制負責將模擬仿真系統主機控制程序模擬運算的數據傳給事先定義的變量,通過專用接口卡將其放在絕對內存地址單元中,再借助智能雙端口的工控機將數據發至前端,以驅動前端設備(如儀表、顯示燈等)進行顯示,或使前端設備(如開關、閥門、步進電機等)進行動作;接收機制與之相反,即實時地將從前端工控機采集的模擬設備的動作量和狀態量(包括模擬實際情況的溫度量、壓力量等)讀到計算機內存地址單元中,并通過專寫程序把這些變量值轉換成主控程序所需要的數據。

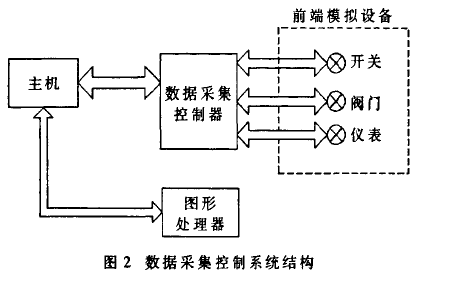

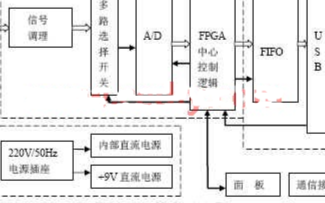

前端設備種類繁多,因此實際中需有針對性地進行設計,以實現工控機對前端設備的控制。此外,工控機與主機之間還必須通過專用接口進行通信,如圖1所示。其結構復雜,不利于設計和調試,同時降低了模擬仿真系統的實時性和效率。

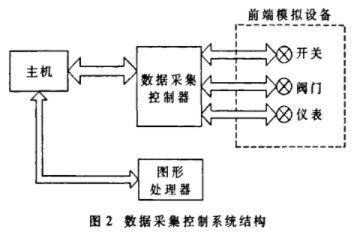

本文設計的IP 核將傳統結構中工控機和接口卡兩級的數據采集控制系統結合起來,設計了一個集成的控制器,由其完全承擔主機與前端設備的數據交換與通信任務。這樣,主機僅負責對整個系統的監控以及對模擬仿真模型的規格運算,而不再分出資源來管理前端模擬設備的控制和數據采集,從而降低了系統的復雜度。結構如圖2所示。

2 系統設計

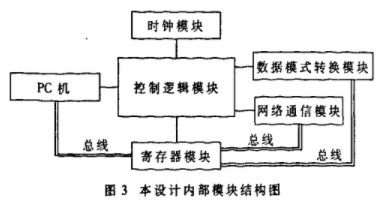

基于前述數據采集控制過程,本IP核分發送數據和采集數據兩種處理機制進行設計。相應地,將本IP核內部劃分為IP核控制邏輯模塊、數據模式轉換模塊、網絡通信模塊、寄存器模塊、總線模塊以及時鐘模塊六部分。其相互關系如圖3所示。

主要模塊功能及其特征描述如下:

(1)IP核控制邏輯模塊:負責整個IP核的控制與運行,當接收到主機發來的工作命令后,該模塊根據命令的種類(發送數據或采集數據)向相應的模塊發送控制命令;出現異常時,本模塊根據事先定義好的規則對異常情況進行處理;

(2)數據模式轉換模塊:該模塊在接收到IP核控制邏輯模塊發來的工作命令后,啟動數字信號——模擬信號的轉換;

(3)網絡通信模塊:采用專用的快速以太網控制器,利用其內部集成的控制器及協議棧,可以方便地與前端模擬設備連接通信;同時利用其支持10/100 M全雙工傳輸模式的性能,實現快速收發數據的目的;

(4)寄存器模塊:包括寄存器訪問和寄存器單元兩部分。寄存器訪問部分的作用在于,當寄存器訪問程序被IP核控制邏輯選中調用時,IP核控制邏輯可通過其對寄存器單元進行讀或寫操作訪問;寄存器單元部分作為發送或采集機制流水線工作時,數據流動的中間暫存介質。基于本系統的設計目標,選擇SDRAM作為寄存器單元的硬件支撐,因其讀寫時序較復雜,需在本系統中集成專用的SDRAM控制器IP 核與其對接;

(5)總線模塊:負責各模塊之間信息的傳輸,如提供Avalon接口供寄存器訪問時使用,它使用Avalon必需的信號來訪問寄存器,并支持任務邏輯傳輸類型;

(6)時鐘模塊:產生相應頻率的時鐘供給IP核,時鐘的頻率由系統時鐘頻率分頻所得。

3 系統實現

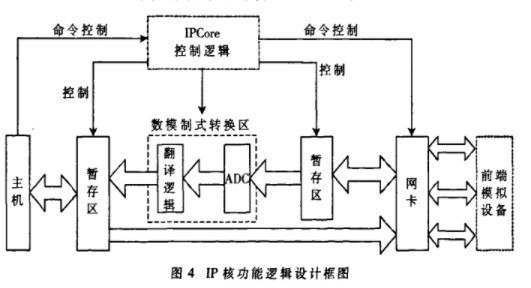

本IP 核功能邏輯的設計基于其任務邏輯定制的基本功能和技術指標。本設計的任務邏輯主要完成對模擬仿真系統前端模擬設備發送指令以及采集前端模擬設備狀態量數據。其功能邏輯也基于發送指令和接收數據兩個數據流來設計,如圖4所示。

為避免高速、高頻系統時序中常存在的競爭、毛刺危險以及建立與保持時間相抵觸等問題,本IP核采用同步設計的方案。同時,為解決實際中仍會經常出現系統產生毛刺和時鐘偏斜等問題。本IP核中擬將時鐘控制改為觸發器輸入允許,將時鐘選擇改為獨立的時鐘分析。

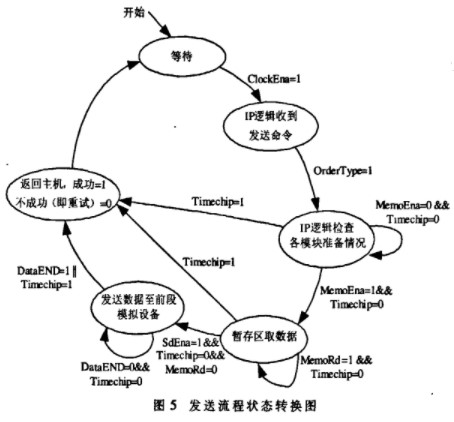

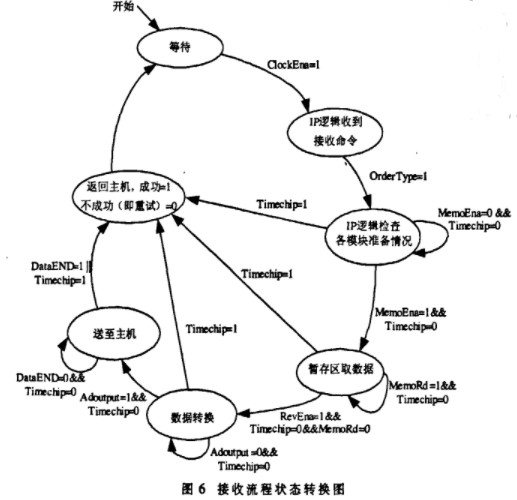

為加快本設計的運行速度及處理效率,本IP核的設計以功能邏輯處理機制為基礎,分別對發送流程和接收流程設計狀態機并實現。

在發送流程的狀態轉換過程中,共有6個狀態,如圖5所示。IP核的控制邏輯判斷來自主機的發送數據命令后,首先檢查其各功能模塊的準備情況,如果準備好,即開始發送數據,從寄存器單元中取出待發送數據并送至網絡通信模塊,由其發送至前端模擬設備。在此過程中,不斷檢測發送完成標志位DataEND,如果該標志位變為有效則表示發送成功,將此信息反饋給主機并進入下一工作周期等待狀態;如果超時該標志位仍未變化,則反饋回主機發送失敗的信息,并請求重發。

相應地,如圖6所示,接收流程的狀態轉換過程有7個狀態。其工作大致與發送流程相同,只是接收數據從寄存器單元讀出后,要先經過數據模式的轉換后,再發送給主機使用。

4 仿真與驗證

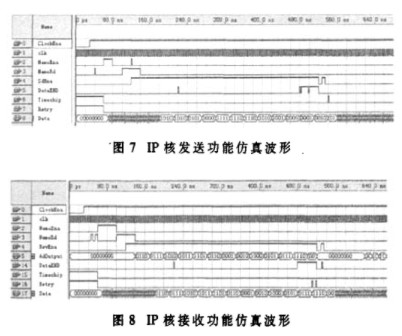

本文選用Altera公司的Cyclone系列的EP1C12240C8器件,并在Quartus7.2環境下采用VHDL語言實現前述IP 核的方案設計。IP核設計完成后,利用SoPC Builder對其進行功能仿真和時序分析。在仿真測試中,以按鍵模擬實際開關動作;以數碼顯示器數值變化模擬實際儀器儀表或傳感器動作,分別對該IP核的發送和接收功能進行仿真測試。

本IP核發送功能仿真測試所得波形如圖7所示。系統的時鐘允許信號ClockEna有效后,系統寄存器有效信號MemoEna及寄存器讀信號MemoRd相繼變為有效,系統在IP 核處理邏輯給出發送信號SdEna之后開始發送寄存器中讀出的數據。在此過程中,不斷檢測發送完成信號DataEND及超時控制信號Timechip,如DataEND有效則停止發送,如前述兩信號同時有效或直到Timechip信號變為有效,則停止本次發送,向IP 核處理邏輯反饋重發信號Retry。同理,IP 核接收功能仿真測試所得波形如圖8所示。通過分析波形可以得出,IP 核處理過程與前述功能邏輯設計一致。

本文提出了一種數據采集與控制系統軟IP核的設計方案,對其采用VHDL語言描述實現,并進行了功能仿真測試。經測試證明,該方案能滿足設計要求,且成本較低,處理邏輯簡單,可方便地移植到多種大型的工業模擬仿真系統中,應用前景廣泛。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603009 -

控制系統

+關注

關注

41文章

6604瀏覽量

110576 -

vhdl

+關注

關注

30文章

817瀏覽量

128121

發布評論請先 登錄

相關推薦

基于FPGA的數據采集控制器IP核的設計方案和實現方法研究

VHDL密碼控制系統的設計

基于FPGA軟核技術應用于高速數據采集系統設計的方法減少開發時間

如何使用FPGA進行仿真系統數據采集控制器IP核設計的資料概述

基于Altera的FPGA器件和VHDL語言實現數據采集系統的設計

采用VHDL語言實現數據采集與控制系統軟IP核的設計

采用VHDL語言實現數據采集與控制系統軟IP核的設計

評論