引言

在廣播和傳送系統中,采用一種或者兩種串行接口來傳輸數字視頻:沒有壓縮的數據使用視頻串行數字接口(SDI),壓縮數據使用異步串行接口(ASI)。在視頻設備中,主要采用移動圖像和電視工程師聯盟(SMPTE)定義的SDI來傳送視頻和音頻數據。

視頻設備能夠支持標準清晰度(SD)數字視頻格式、高清晰度(HD)數字視頻格式,或者同時支持。SD視頻傳輸的SDI速率為270Mbps, 360 Mbps或者540 Mbps,而HD視頻傳輸的SDI速率為1.485 Gbps或者1.485/1.001 Gbps。HD提供高質量的視頻,代表了今后數字視頻廣播的發展方向。隨著HD視頻需求的增長,要求硬件能夠處理HD技術所需的大數據吞吐量。

在數字視頻傳送環境中,數據傳送的主要方式是ASI的270 Mbps單節目傳送流(SPTS)或者多節目傳送流(MPTS),這些方式由數字視頻廣播(DVB)協會定義。

廣播設備開發人員通常使用ASSP來實現SDI和DVB-ASI功能,也可以利用可編程邏輯器件(PLD),使用PLD中的邏輯和其它嵌入式資源構建所需的各種數字功能,來實現這些接口。通過使用PLD(而不是ASSP),可以顯著降低總成本。某些情況下,在每ASI通道或者每SDI端口的基礎上,PLD不到ASSP成本的1/10。

SDI的可編程邏輯解決方案

要達到SDI和DVB-ASI需要的270Mbps數據速率,可編程解決方案需要提供以下功能:

LVDS I/O

足夠的邏輯容量

數據恢復能力

對于HD-SDI數據速率,需要采用支持嵌入式SERDES技術、時鐘數據恢復,并集成了高速收發器通道的PLD,例如Altera的Stratix GX系列FPGA。

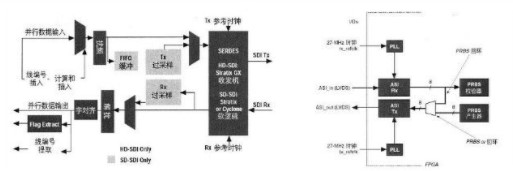

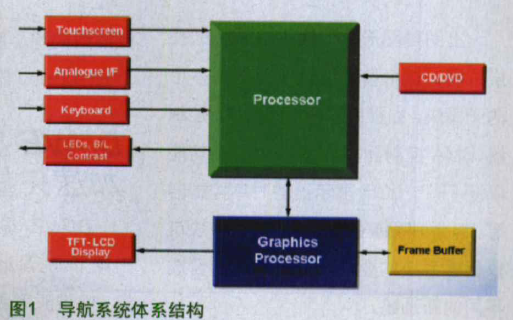

圖1所示為Altera可編程邏輯中實現SD-SDI和HD-SDI功能所需的構成單元。SD-SDI解決方案在邏輯單元(LE)中利用過采樣技術來恢復數據。FPGA中的基本構建模塊LE在SERDES模塊中表示為“軟邏輯”。在HD-SDI解決方案中,嵌入式SERDES和CDR電路完成時鐘和數據恢復功能。

HD-SDI方案中的其它功能包括發射機側的線編號插入和循環冗余校驗(CRC)計算,以及接收機側的線編號提取和循環冗余校驗。

基于可編程邏輯的DVB-ASI解決方案

可以采用FPGA來實現DVB-ASI所需的數據速率,FPGA為ASI接收機和發射機提供LVDS I/O,并為接收機和發射機輸入基準時鐘提供PLL。Altera的Cyclone、Stratix和Stratix GX系列FPGA具備這些功能。圖2所示為在FPGA中實現DVB-ASI所需的構成單元,包括發射機和接收機耦合的回環通道,以及用于內置測試操作的偽隨機二進制序列(PRBS)校驗器和PRBS產生器。

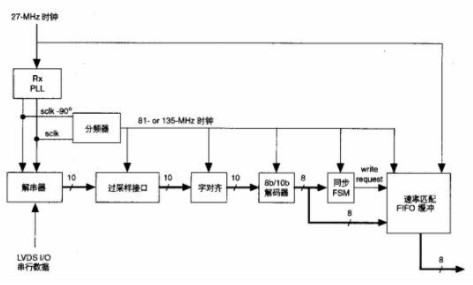

ASI接收機組成:

解串器,將到達的串行數據轉換為10比特寬的并行數據

過采樣接口,實現數據恢復和位同步

字對齊

8位/10位編碼器,將10位并行數據轉換為8位寬原始數據

同步狀態機探測字同步或者同步丟失

速率匹配FIFO緩沖匹配到達比特和發送(或者系統)時鐘的速率。

圖3. ASI接收機結構框圖

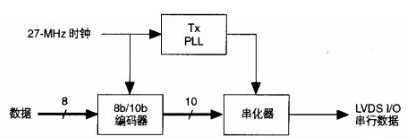

ASI發射機含有一個8位/10位編碼器和一個串化器,編碼器將8位寬的字轉換為10位,串化器將10位并行字轉換為串行數據,采用一個10位移位寄存器實現該功能,以字速率從編碼器輸入,以LVDS輸出緩沖比特率輸出。27MHz基準時鐘乘以10的PLL提供比特率時鐘,支持抖動受控ASI傳輸串化。ASI發射機構成單元如圖4所示。

在可編程邏輯中實現SDI和DVB-ASI

一般情況下,采用FPGA實現一個ASI通道需要的LE數量少于1,000。Cyclone II FPGA每通道成本低于1美元比現有ASSP方案低得多。

一個10位SD-SDI全雙工端口在Altera FPGA中只需要400個LE。對于Cyclone II FPGA中的10位SD-SDI數據,其每端口成本也遠遠低于現有的ASSP方案。對于20位HD-SDI數據,收發器通道邏輯大約需要1,000個LE,在Stratix GX器件中實現這些邏輯時,每端口成本等于甚至低于ASSP的每端口成本。當考慮到可編程邏輯的其它集成性能時, Stratix GX方案的優勢更加突出。

可編程邏輯集成功能還具有其它優勢

在典型應用中,DVB-ASI和SDI只是廣播設備全部功能的一部分。例如,DVB-ASI通常用于廣播數據轉發系統,需要進行視頻復用、壓縮、調制和解調、時隙復用、編解碼等信號處理。這些操作需要前向糾錯(FEC)、濾波、間插、正交振幅調制(QAM)映射、Viterbi和Reed-Solomon解碼等數字信號處理功能。這些功能可以利用FPGA中的資源來實現,包括LE、Cyclone II器件中的乘法器,以及Stratix器件中的DSP模塊。

圖4. ASI發射機結構框圖

通過將這些功能集成到幾個器件中,基于FPGA的解決方案進一步降低了開發成本,節省了電路板空間,降低了系統復雜性。FPGA所具有的靈活性使開發人員能夠定制實現設計中每一單元之間的接口,在最短的時間內加入各種功能,突出設計質量。設計人員還可以得到與單個可編程器件相同的ASI通道或者SDI端口數,而采用ASSP就必須使用多個分立器件。

參考設計加速產品上市

在SDI參考設計中,對三個SMPTE建議抖動參數進行了評估:

抖動產生器——器件或者系統產生一個串行數字信號(在這種情況下是HD-SDI),它含有某一振幅和頻率的正弦抖動。產生的抖動也可以是非正弦的。

接收抖動容限——當應用于器件或者系統輸入時,正弦抖動的峰-峰值振幅會導致性能劣化。

抖動傳送——輸入抖動導致的器件或者系統輸出抖動。

DVB-ASI標準并沒有針對抖動容限提供任何規范,但可以采用下面的抖動參數用于評估Altera的DVB-ASI參考設計:

發射機的抖動產生

接收機的抖動容限

接收機靈敏度

輸出振幅和邊沿速率

Cyclone視頻演示板和Stratix GX串行視頻演示說明板可以演示這些參考設計。

結語

與ASSP相比,Altera的DVB-ASI和SDI可編程邏輯解決方案能夠顯著降低廣播設備的開發成本。將DVB-ASI和SDI功能集成到少量器件中,進一步降低了成本、節省了電路板空間,降低了復雜性。

-

FPGA

+關注

關注

1629文章

21754瀏覽量

604211 -

收發器

+關注

關注

10文章

3437瀏覽量

106059 -

發射機

+關注

關注

7文章

505瀏覽量

48050

發布評論請先 登錄

相關推薦

什么是可編程邏輯

可編程邏輯器件發展歷史

請問有人知道Spartan6 LXT設備中DVB-ASI TS接口的工作解決方案嗎?

PLD可編程邏輯器件

可編程邏輯控制器的特點

可編程邏輯器件向什么目標前進

可編程邏輯器件的分類有哪些

可編程邏輯器件測試方法

基于國產可編程邏輯芯片的工業網絡解決方案

什么叫可編程邏輯器件 可編程邏輯器件有哪些特征和優勢?

LMH0340/040/070/050 DVB-ASI SDI串行器和電纜驅動器數據表

基于可編程邏輯的DVB-ASI解決方案提高廣播應用的集成度

基于可編程邏輯的DVB-ASI解決方案提高廣播應用的集成度

評論