鎖相環(PLL)頻率合成技術是頻率源設計的一種現代化技術,已廣泛應用于通信、導航、電子偵查、電子對抗、遙控遙測及現代化儀器儀表等領域中。

1、 集成鎖相環芯片PE3240介紹

PE3240是Peregrine公司最新生產的一種可在高達2.2GHz頻段工作的分頻次數可編程的數字鎖相環芯片,正常工作狀態下功耗低于0.6W。PE3240采用了UltraCMOS技術,具有超低相位噪聲的優良性能。

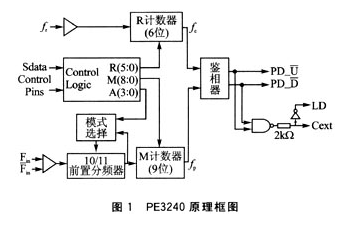

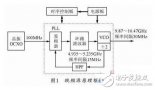

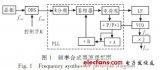

圖1為PE3240芯片的原理框圖。PE3240由雙模前置分頻器、計數器、鑒相器和控制邏輯組成。雙模前7置分頻器采用吞脈沖分頻技術,通過模式選擇確定對VCO輸出頻率是10分頻還是11分頻,通過20位寄存器的置數值,主計數器M和參考計數器R分別對雙模前置分頻器輸出頻率和參考頻率進行分頻,另外的計數器A,用于模式選擇,鑒相器產生上下頻率控制信號,還提供鑒相器測試和時鐘檢測輸出功能。PE3240的分頻置數采用三線串行模式。該芯片具有功耗低、相位噪聲低、雜散小、分頻頻率高、編程靈活方便等優點。

PE3240主要電路性能為:

雙模前置分頻器(10或11分頻);

9位M和4位A吞吐脈沖計數器;

6位R參考頻率計數器;

輸出頻率范圍為200-2200MHz;

參考頻率最高為100MHz;

三線串行編程模式。

2、 頻率源設計方案

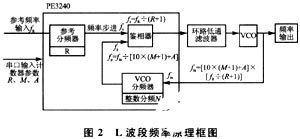

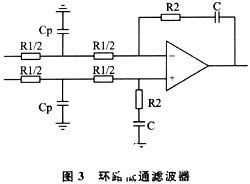

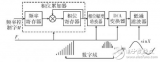

如圖2所示,頻率源原理框圖以PE3240為核心。PE3240需要外接環路濾波器和壓控振蕩器。本設計中環路低通濾波器采用有源比例積分濾波器。如圖3所示,環路低通濾波器的作用是濾除鑒相器輸出電流中的無用組合頻率分量及其他干擾分量,以保證環路所要求的性能,并提高環路的穩定性。

根據鎖相環參數確定R、C等元件的值。需要注意的是,要將環路帶寬設置在鑒相器噪聲基底與VCO自由振蕩時相位噪聲的交叉點上,以提高PLL的相位噪聲性能。

如圖2所示,通過三線串口,由單片機將分頻參數M、R、A置入PE3240,將輸出頻率進行[10×(M+1)+A]分頻,作為鑒相器的一路輸入,另一路鑒相器輸入是將參考頻率fR進行(R+1)分頻,通過鑒相器后,得到與兩路信號的相位誤差成比例的誤差電壓,經環路低通濾波器,取出有用的直流電壓分量,控制VCO的輸出頻率鎖定在[10×(M+1)+A]×[fR/(R+1)]頻率上。

本設計中,參考頻率選為28MHz,R=39,A=3。這樣,通過改變M值(119-159,步進為1),可得到頻率間隔為7MHz,范圍為842,1-1122.1MHz的穩定輸出頻率。

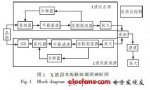

3、 與單片機接口及軟件編程

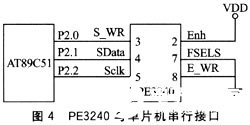

PE3240與單片機接口只有一種方式,即三線串口模式,電路連接如圖4所示。

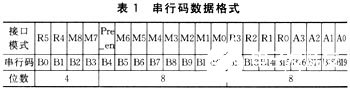

分頻參數R、M、A是以20位串行碼形式輸入PE3240的。其中,R為6位,M為9位,A為4位,還有一位Pre_en為常0,數據格式如表1所列。

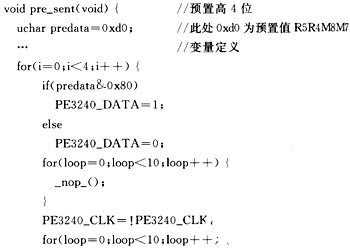

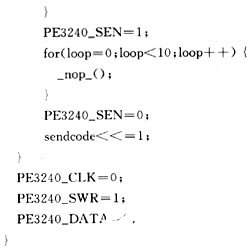

PE3240串口模式與SPI串口及RS232串口都不同,必須按照特定的時序實現串行碼輸入,即當S_WR為低電平時,在Sclk的上升沿,串行碼被串行輸入PE3240主寄存器,注意,高位R0先入。

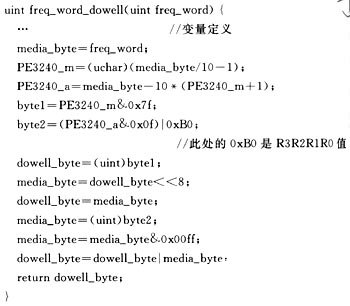

根據串口時序和數據格式,我們編寫了使用高效的AT89C51單片機與PE3240的C51串口通信函數。具體如下:

本串口通信函數的設計十分巧妙,由于單片機一個字節是8位,因此把20位串行碼分為高4位和低16位分別發送,高4位由預置函數置入,低16位由串行輸入函數置入。

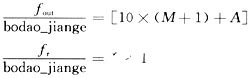

其中,分頻參數R、M、A是根據輸出頻率的首頻率和波道間隔,按下式計算:

4 、總結

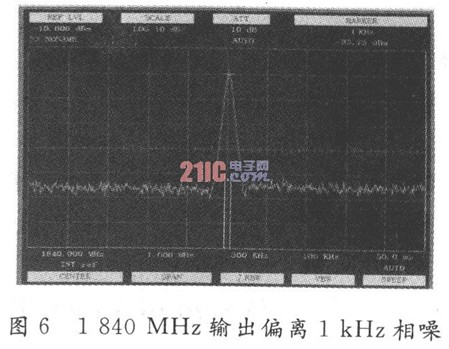

根據本設計方案,制作的L波段頻率源,已成功應用于無人機分米波儀表著陸系統設備中。性能指標良好:輸出頻率范圍為842.1-1122.1MHz,頻率間隔為7MHz,波道數為40;雜散抑制度>350dB;相位噪聲≤-85dB(偏離中心頻率10KHz處);頻率穩定度為±1×10-6。

責任編輯:gt

-

芯片

+關注

關注

455文章

50732瀏覽量

423270 -

pll

+關注

關注

6文章

776瀏覽量

135139 -

計數器

+關注

關注

32文章

2256瀏覽量

94485

發布評論請先 登錄

相關推薦

基于HMC704LP4的一種X波段跳頻源設計方案

L波段細步進捷變頻頻率綜合器設計

DDS+PLL高性能頻率合成器的設計方案

基于DDS+PLL在電臺設計中的應用

X波段低相噪跳頻源的設計

一種X波段頻率合成器的設計方案

C波段頻率源設計及性能分析

基于DDS的短波射頻頻率源設計方案解析

X波段間接式頻率綜合器的方案分析

基于PE3240 PLL芯片實現L波段頻率源的設計方案

基于PE3240 PLL芯片實現L波段頻率源的設計方案

評論