很多嵌入式系統,特別是應用于圖像處理與高速數據采集等場合的嵌入式系統,都需要高速緩存大量的數據。DDR(Double Data Rate,雙數據速率)SDRAM由于其速度快、容量大,而且價格便宜,因此能夠很好地滿足上述場合對大量數據緩存的需求。但DDR SDRAM的接口不能直接與現今的微處理器和DSP的存儲器接口相連,需要在其間插入控制器實現微處理器或DSP對存儲器的控制。

隨著密度與性能的不斷提升,現場可編程門陣列(FPGA)已被廣泛應用于各種嵌入式系統中。而且,現在很多的FPGAs都提供了針對DDR SDRAM的接口特性:其輸入輸出引腳都與SSTL-Ⅱ電氣特性兼容,內部提供了DDR觸發器、鎖相環等硬件資源。使用這些特性,可以更加容易地設計性能可靠的高速DDR SDRAM存儲器控制器。

1 DDR SDRAM在嵌入式系統中的應用

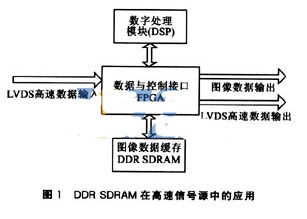

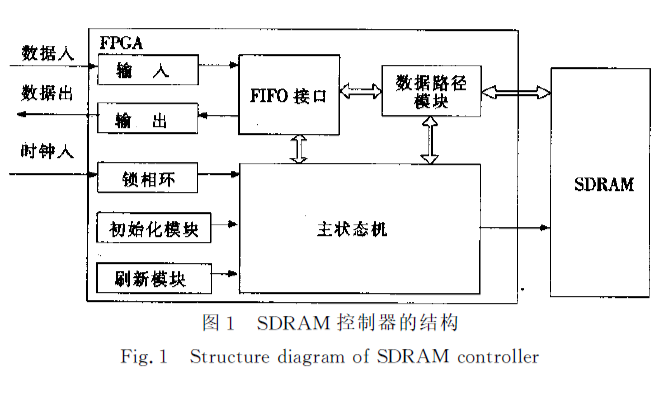

圖1是DDR SDRAM在高速信號源系統中的應用實例。

在該系統中,由FPGA的完成各模塊之間的接口控制。FPGA接收從前端傳送過來的高速數字信號,并將其存儲在DDR SDRAM中;DSP通過FPGA讀取DDR中的數據,處理后再送回到DDR SDRAM,最后由FPGA負責將數據分兩路輸出。

該系統對存儲器的要求是能夠高速地存儲大量的數據,DDR SDRAM正好能滿足這一要求,此時,FPGA是否能對DDR SDRAM進行有效控制就成為影響系統性能的關鍵。最后的試驗結果表明,FPGA是能夠勝任這一任務的。

2 DDR SDRAM的工作方式

在DDR SDRAM能夠被存取數據之前,需要先對其初始化。該初始化流程是預先定義好的。不正確的操作將導致無法預料的結果。初始化的過程中將設置DDR SDRAM的普通模式寄存器和擴展模式寄存器,用來制定DDR SDRAM的工作方式,這些設置包括突發長度、突發類型、CAS潛伏期和工作模式以及擴展模式寄存器中的對DDR SDRAM內部DLL的使能與輸出驅動能力的的設置。模式寄存器可以被再編程,這時需要DDR SDRAM的各個區(bank)處于空閑狀態,從而改變存儲器的工作模式。如果操作正確,對模式寄存器的再編程不會改變存儲器內存儲的數據。

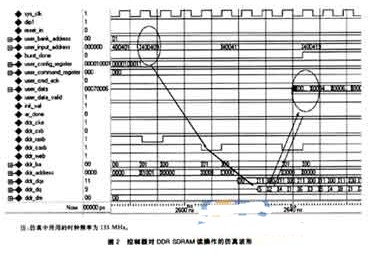

初始化完全之后,DDR SDRAM便進入正常的工作狀態,此時便可對存儲器進行讀寫和刷新。DDR SDRAM在一對差分時鐘(CLK與CLKn;CLK的上升沿與CLKn的下降沿的交點被認為是CLK的上升沿)的控制下工作。命令(地址和控制信號)在每個時鐘(CLK)的上升沿被觸發。隨著數據一起傳送的還包括一個雙向的數據選通信號,接收方通過該信號來接收數據。DQS作為選通信號在讀周期中由DDR SDRAM來產生,寫周期中由存儲器控制器來產生。該選通信號與數據相關,其作為類似于一個獨立的時鐘,因此也需要滿足相應的時序要求。讀周期中,DQS與數據是邊沿對齊的;寫周期中,DQS與數據是中心對齊的。存儲器輸入的數據在DQS的兩個沿都觸發,輸出的數據也是以DQS的兩個沿作為參考,同時還要以時鐘CLK的兩個沿作為參考。因此,由于接口在時鐘的兩個沿的觸發下工作。其數據寬度(n)是存儲器數據寬度(2n)的一半。圖2描述了DDR SDRAM的工作方式。

對DDR SDRAM的讀和寫操作是基于突發的:從一個選定的地址單元開始,連續存取設置好長度的地址單元。該長度就是所謂的突發長度。DDR SDRAM提供的可編程的讀或寫的突發長度為2,4或8。數據的存取以一個激活命令(ACTIVE command,RAS_n low)開始,接著便是讀(CAS_n low)或寫(CAS_n low and WE_n low)命令。與激活命令一起被觸發的地址位用來選擇將要存取的區(bank)和頁(或行);與讀或寫命令一起觸發的地址位用來選擇突發存取的起始列單元。使用控制器讀取DDR SDRAM的仿真波形示意圖如圖2所示。讀命令被觸發后,數據將在1.5-3個時鐘周圍之后出發在數據總線上。這個延遲就是所謂的CAS潛伏期(CAS latency),即從DRAM內核讀出數據到數據出現在數據總線上所需要的時間 。CAS潛伏期的到小與SDRAM的速度和存儲器的時鐘頻率有關。

當要存取一個不同行的地址單元時,需要通過一個預充電(PRECHARGE)操作關閉當前行。自動刷新(AUTO-REFRESH)命令用來周期性地刷新DDR SDRAM,以保持其內部的數據不丟失。

3 DDR SDRAM控制器的設計

DDR SDRAM控制器的功能就是初始化DDR SDRAM;將DDR SDRAM復雜的讀寫時序轉化為用戶方簡單的讀寫時序,以及將DDR SDRAM接口的雙時鐘沿數 據轉換為用戶方的單時鐘沿數據,使用戶像操作普通的RAM一樣控制DDR SDRAM;同時,控制器還要產生周期性的刷新命令來維持DDR SDRAM內的數據而不需要用戶的干預。

3.1 DDR SDRAM控制器的控制流程

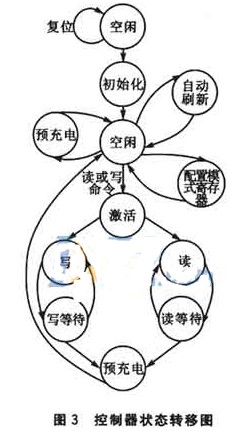

DDR SDRAM提供了多種命令,整個控制狀態機非常復雜。但很多應用場合中,并不需要用到所有的命令,因此為了簡化設計,但同時又兼顧盡可能多的應用場合,在控制器的設計中制定了如下幾種功能:DDR SDRAM的初始化、可變長度的突發讀寫,自動刷新功能,預充電以及模式寄存器的重置(reload)。圖3是控制器整個狀態轉移圖。

系統上電后,DDR SDRAM處于空閑狀態(Idle),在對存儲器進行讀寫操作之前,需要先對其進行初始化。初始化的過程中,將設置突發長度,突發類型,CAS潛伏期等參數。DDR SDRAM的初始化有一個固定的步驟,錯誤的操作將導致DDR SDRAM進入不確定狀態。在控制器中使用了一個專門的初始化狀態機來對DDR SDRAM進行初始化。

初始化完之后便可對DDR SDRAM進行讀、寫或其他操作。在執行讀(寫)命令之前,先要激活(Active)將要讀(寫)的行,之后便可對該行進行突發讀(寫),在控制器的設計中,所有的讀寫命令都是不帶預充電的,因此,某一行被激活之后將一直處于激活狀態,直到用戶發送突發終止命令,此時控制器將自動產生一個預充電命令來關閉當前行。這樣,某一行被激活之后用戶便可進行連續的突發讀(寫)操作,從而節省了每次突發讀寫所需要的激活時間,提高了系統的數據吞吐率。

控制器同時提供了一個自動刷新(auto refresh)計數器,每隔一定的時間間隔(即DDR SDRA的刷新周期,根據所使用的存儲器而定,可在控制器中設定),便會產生一個刷新請求,如果此時DDR SDRAM處于空閑狀態,控制器便會發生一個自動刷新命令來對DDR SDRAM進行刷新;如果此時DDR SDRAM正在進行讀(寫)操作,控制器將會等到當前的讀(寫)操作完全之后再發送新命令。在刷新過程中,用戶如果有讀(寫)請求,控制器將在當前的刷新周期完成之后再響應用戶的請求。

正常的操作過程中,當DDR SDRAM處于空閑狀態時,用戶還可以根據實際的需要來重置存儲器的控制寄存器,重新設定存儲器的突發長度、突發類型、CAS潛伏期等參數。

3.2 控制器數據通道的結構

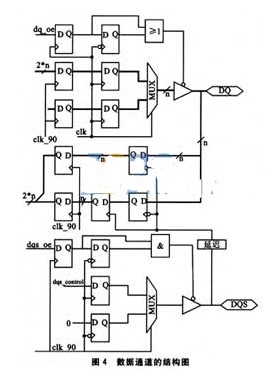

圖4是DDR SDRAM控制器數據通道的結構圖。圖4中完整的顯示了控制器讀和寫數據通道上DQ與DQS的結構關系。前面提到過,Cyclone系列FPGA沒有帶DDR觸發器的輸入輸出單元,但完全可以用靠近輸入輸出引腳處的邏輯資源來實現DDR觸發器,而且最后的結果表明,這種實現方式可以滿足時序要求。

從圖4中也可以看到,控制器內部有兩個時鐘,clk和clk_90,兩者之間的相位差為90°。圖中將面向存儲器的時鐘命名為clk。它是clk_90時鐘的90°相位延遲后的信號。clk_90作為系統時鐘來驅動整個FPGA,clk時鐘驅動存儲器接口路。

3.2.1 DQS相位延遲電路

在讀周期中,DDR SDRAM處輸出的DQ和DQS信號是邊沿對齊的。為了使用DQS作為選通信號來捕獲DQ,DQS信號需要在FPGA內部相對于DQ信號作90°的相位延遲。但是這個延遲不能使用鎖相環(PLL)來完成,因為DQS信號不具有時鐘的特性。因此,需要在DQS和數據時鐘之間加一個延遲鏈(delay clain),如圖4中所示。

前面提到過,Cyclone系列FPGA在其DQS輸入引腳上有一個專用的延遲單元,用來使DQS相對于DQ信號產生一個90°相移。因此,可 以使用該硬核資源來完成對DQS的相移,而不必通過內部的邏輯來搭建這樣一個延遲電路,從而可以獲得更好的時序性能。

3.2.2 再同步

讀周期中,從DDR SDRAM來的數據信號首先通過延遲后的DQS鎖存到DDR觸發器中。為了在FPGA內部能夠使用該數據,還要將其同步到FPGA內部的時鐘域上,這個過程稱為再同步(resynchronization)。如圖4所示,對于前一級DQS延遲后的信號鎖存的數據再通過clk_90同步之后才送到內部數據總線上。

在寫周期中,DQS與DQ必須是中心對齊的(center align)。我們用clk_90時鐘觸發的DDR觸發器產生DQS信號,因此,為了滿足時序要求,從內部來的數據通過clk_90時鐘鎖存后再由clk觸發的DDR觸發器將其輸出,從而保證DQS與DQ是中心對齊的。

4 控制器的實現

該控制器針對16位寬512Mb的DDR SDRAM設計,在Altera公司的Quartus Ⅱ4.2環境中采用Cyclone系列的FP1C6Q240C6來實現,總共使用了729個邏輯單元,占FPGA可編程邏輯資源的12%,此外還使用了1個鎖相環(PLL)。最后,在Modelsim 5.8中對整個工程進行布局-布線后仿真(Post-Place&Route Simulation),采用的模型為Micron公司的512Mb的DDR SDRAM MT46V32M16的仿真模型,時鐘為133MHz,圖2是控制器讀取DDR SDRAM的時序仿真波形。

5 結論

本文給出了一種通過FPGA控制將DDR SDRAM應用在嵌入式系統中的方法。設計中采用Altera公司性價比較高的Cyclone系列FPGA,并充分利用片內提供的鎖相環、DDR觸發器以及DQS延遲鏈等硬件資源,占用的邏輯資源少。該設計可以很容易地轉移到Altera公司其他系列的FPGA上,經過適當的修改還可以用來控制64位寬的DIMM型的DDR SDRAM,因此可以很好地應用在需求高速度、大容量存儲器的場合中。

-

控制器

+關注

關注

114文章

17136瀏覽量

184558 -

嵌入式

+關注

關注

5153文章

19708瀏覽量

318051 -

SDRAM

+關注

關注

7文章

443瀏覽量

56361 -

存儲器

+關注

關注

38文章

7653瀏覽量

167579

發布評論請先 登錄

嵌入式相變存儲器在汽車微控制器中有什么優點?

嵌入式存儲器的應用:sDRAM硬件連接方案以及軟件接口的實現

MCU的嵌入式系統設計,如何運行SDRAM?

DRAM、SDRAM及DDR SDRAM之間的概念詳解

如何使用FPGA實現高速圖像存儲系統中的SDRAM控制器

基于FPGA的DDR3SDRAM控制器設計及實現簡介

MCU的嵌入式系統設計,運行SDRAM(運行效率比較)

評論