引言

數據采集技術是一種流行且實用的電子技術。它廣泛應用于信號檢測、信號處理、儀器儀表等領域。近年來,隨著數字化技術的不斷發展,數據采集技術也呈現出速度更高、通道更多、數據量更大的發展趨勢。

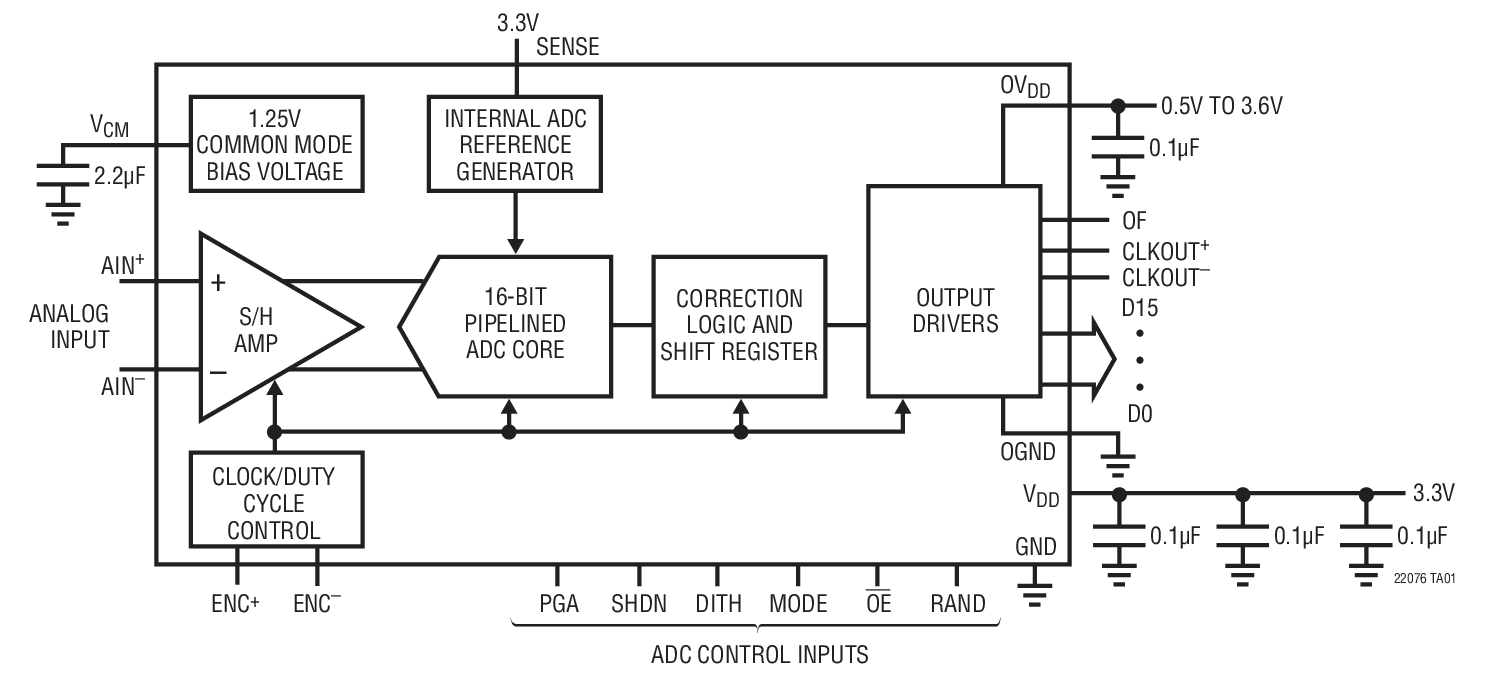

本設計中數據采集系統的核心器件是凌力爾特公司的A/D轉換芯片LTC2207.本文研究了在ARM核S3C2440芯片和FPGA的控制下對直流數據和正弦信號的采集應用,并進行了相關的仿真驗證。

1 LTC2207芯片介紹

1.1 LTC2207的功能特性

LTC2207是16位A/D轉換器,它的采樣速率為105Msps.LTC2207是針對輸入頻率為700 MHz的高頻、寬動態范圍信號進行數字化處理而設計的。它可以利用PGA前端(輸入范圍為1.5Vp-p或2.25Vp-p)對該ADC的輸入范圍進行優化。

LTC2207非常適合于要求苛刻的通信應用。它的AC性能包括78.2 dB噪聲層和100 dB無雜散動態范圍(SFDR);250 MHz時SFDR>83 dB(輸入范圍為1.5Vp-p時);80fSRMS的超低抖動實現了高輸入頻率的欠采樣和卓越的噪聲性能;最大DC規格包括整個溫度范圍內的±4LSB INL、±1LSB DNL(無漏失碼)。

LTC2207具有單一的3.3 V供電電源,單一的電源允許CMOS輸出擺幅為0.5~3.6 V.它同時具有700MHz全功率帶寬S/H(采樣及保持),可選的內部抖動和數據輸出(Randomizer)隨機函數發生器,功耗為900 mW.LTC2207可利用正弦波時鐘、PECL、LVDS、TTL或CMOS輸入對ENC+和ENC-輸入進行差分或單端驅動。可任選的時鐘占空比穩定器在全速和多種時鐘占空比條件下實現了高性能。

LTC2207的引腳說明略一一編者注。

1.2 LTC2207的時序說明

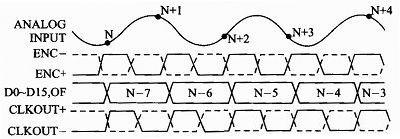

LTC2207時序圖如圖1所示。LTC2207是帶有前端PGA的CMOS多步轉換器。模擬輸入是差分信號以提高共模噪聲抑制,最大限度地利用輸入范圍。此外,差分輸入信號可以降低取樣保持電路的諧波。編碼輸入也比共模抑制輸入具有更強的抗干擾能力。

圖1 LTC2207時序圖

LTC2207的采集取決于ENC+/ENC-輸入引腳的狀態,由圖1可知LTC2207在ENC+引腳的上升沿時(ENC-引腳的下降沿時)采樣模擬輸入信號。它有5個流水線模數轉換階段,經過7個周期后,一個模擬采樣輸入就會轉換為一個數字值。數字輸出上/下溢出則由OF引腳上的邏輯高電平表示。

此A/D轉換器有一個延遲的編碼輸入作為數字輸出,提供了CLKOUT+和CLKOUT-兩信號;需要使用正弦時鐘編碼信號CLKOUT+/CLKOUT-將數據同步轉換到數字系統。數據在CLKOUT+的上升沿或CLKOUT-的下降沿鎖存,在CLKOUT+下降沿和CLKOUT-上升沿時更新。

2 硬件電路設計

信號采集部分主要完成對模擬信號的調理和A/D轉換芯片的采集。A/D轉換芯片的輸入信號是差分的,而被采集的信號是單端的,這就需要把單端信號轉換成差分信號。輸入的信號經過MAX4201緩沖后,由差分驅動器AD8131轉換成差分信號,驅動A/D轉換芯片LTC2207.

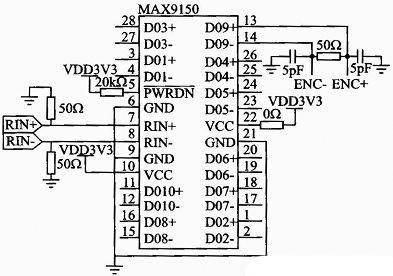

采用LVDS轉發器MAX9150轉換FPGA所給的時鐘信號,作為LTC2207的采集控制信號ENC.MAX9150的轉換電路如圖2所示。

圖2 MAX9150的轉換電路

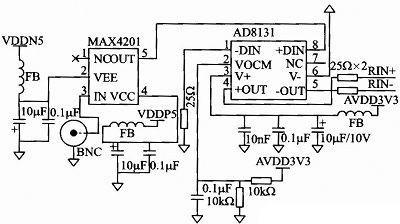

LTC2207的模擬差分信號輸入前端的調理芯片采用低噪聲、低功耗、超高速開環緩沖器MAX4201和高速差分驅動器AD8131.采集輸入信號的前端調理電路如圖3所示。圖中MAX4201采用±5 V供電,對地并聯的電容給電源濾波,為緩沖器提供無干擾的電源。緩沖后的信號,由MAX 4201的5引腳輸出,其輸出阻抗是50 Ω,再經過AD8131完成單端到差分的轉換。

圖3 采集輸入信號的前端調理電路

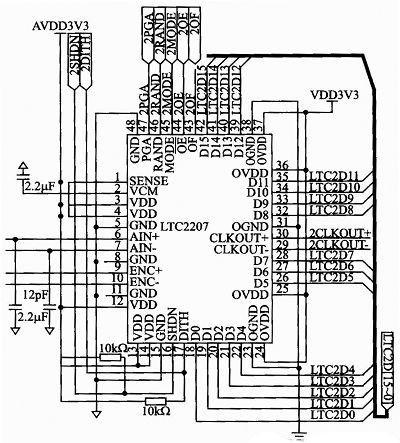

LTC2207的采集控制電路如圖4所示。其中,AIN+、AIN-為差分模擬輸入信號;ENC+、ENC-為采集芯片的時鐘控制信號;D0~D15為16位數據輸出信號;CLKOUT+、CLKOUT-為時鐘輸出信號。

圖4 LTC2207的采集控制電路

3 ARM與FPGA的編程控制

采用硬件描述語言Verilog HDL,對LTC2207相關引腳的使能以及FPGA如何讀取采集來的數據的程序如下:

S3C2440控制啟動FPGA開始采集的start程序如下:

4 仿真驗證

采用QuartusII軟件中的調試工具SignalTapII邏輯分析儀進行仿真驗證。當采集輸入為0.453 V直流量時,FPGA采集的數據仿真如圖5所示。

可以觀察數據3337h、3333h、332Bh、3337h等變化不大,僅在低5位有所變化。根據A/D采集原理,輸入電壓/參考電壓=采樣值/216.所給參考電壓是2.25 V,采樣值若取以上數據中的3 334h(在相對穩定的數據中任取一個),轉換成十進制為13 108,代入以上公式:13108×2.25/65536=0.45.得到FPGA讀到的數據計算的輸入電壓是0.45 V,而此時測得的實際輸入電壓是0.453 V.誤差很小,約為0.6%,基本由噪聲所致,采得的數據比較精確。

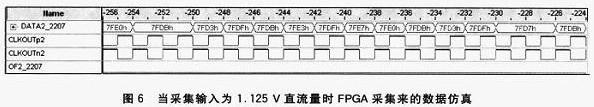

當采集輸入為1.125 V直流量時,FPGA采集來的數據仿真如圖6所示。同理若取其中的7FE0h,此時算得的誤差約為0.8‰。

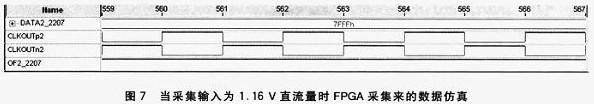

當采集輸入為1.16 V直流量時FPGA采集來的數據仿真如圖7所示。

從圖中可發現此輸入下數據已經達到滿值(輸入超過1.125 V),OF為高,說明數據有溢出。

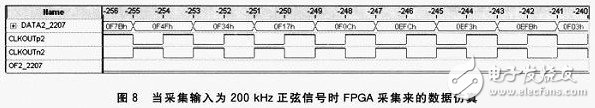

當采集輸入是由信號發生器給的200 kHz正弦信號時FPGA采集來的數據仿真如圖8所示。

由一個周期采樣點數公式N=Tsig/Tsam=fsam/fsig,知此輸入頻率下采樣點數為40 MHz/200 kHz=200,若看坐標-250處的OF17h,則找出一個周期后的那個數是不是和初始值相同。FPGA坐標為150時的數據仿真如圖9所示。它處在坐標150的位置為OF07h,和OF17h相差很小。取對應的多組數觀察都證明對模擬信號的數據采集亦是比較正確的。

結語

針對A/D轉換芯片LTC2207,詳細描述了以FPGA和ARM作為控制器的采樣設計。采用FPGA直接對A/D進行配置,避免了采用DSP、單片機等進行配置的傳統方式,因而設計靈活、簡單、通用性強。通過對采集來的數據進行仿真驗證,發現在ARM和FPGA的控制下16位A/D芯片LTC2207得到了很好的采集應用。

-

FPGA

+關注

關注

1630文章

21761瀏覽量

604411 -

芯片

+關注

關注

456文章

50967瀏覽量

424920 -

ARM

+關注

關注

134文章

9111瀏覽量

368066 -

控制器

+關注

關注

112文章

16404瀏覽量

178633

發布評論請先 登錄

相關推薦

怎么用串口進行數據采集

LTC2207IUK#PBF

如何更好地進行數據采集

LTC2207在S3C2440和EP3C25控制下的采集應用

如何使用FPGA進行數據采集系統電路設計?工作原理和設計過程詳細分析

LTC2207 16 位、105Msps ADC

LTC2207/LTC2206:16位、105Msps/80Msps ADC數據表

LTC2207芯片的功能特性、工作原理及進行數據采集應用分析

LTC2207芯片的功能特性、工作原理及進行數據采集應用分析

評論