引言

近年來,為了提高信息傳輸速率,增強通信抗干擾能力,飛行器測控通信系統已從統一載波體制向擴頻統一測控通信體制發展。但是,這種寬帶擴頻測控技術的應用使得同步設計成為系統實現的難點,尤其對于多頻率源系統,信號之間的嚴格同步更為困難。一般情況下,為了獲得多路DDS的同步,設計者往往會使用多種手段對參考時鐘、數據刷新、鎖相倍頻等步驟小心處理,這樣不但耗費了大量的精力物力,而且效果往往不盡如人意。

美國ADI公司推出的高性能4通道直接數字式頻率合成器AD9959,在單芯片上集成了4個獨立的DDS核,通過一個公用參考頻率內部同步4個DDS通道,避免了多個DDS同步過程中由于器件特性差異造成同步困難的問題,在降低同步設計難度的同時,還提供了靈活的控制能力。

AD9959

AD9959是美國ADI公司的多通道DDS器件,內部包含4個同步的10bit 500MHz DDS。每個DDS通道擁有獨立的32bit頻率分辨率控制、14bit相位偏移控制及10bit 輸出幅度控制,輸出經過10bit DAC轉化為標準正弦信號。采用這種獨立控制方式便于校正模擬濾波、放大或PCB布線引起的I/Q信號失配。AD9959擁有16級幅度、頻率或相位調制(ASK、FSK、PSK),支持線性掃頻、掃相、掃幅等功能,具有良好的寬帶、窄帶無雜散噪聲(SFDR)性能。高速串行I/O端口兼容早期ADI DDS產品的SPI串行通信方式,通過4個串行數據引腳SDIO[3..0]可方便對芯片進行編程操作,具有良好的多通道同步性能。亦可采用菊花鏈方式用一個主控芯片(DSP或FPGA)同步多個AD9959器件以獲得更多同步DDS通道。

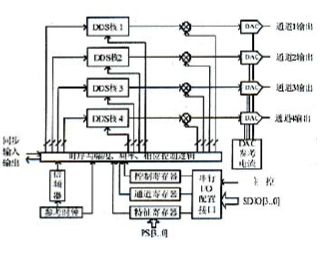

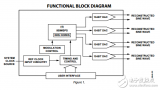

AD9959內部結構如圖1所示。

圖1 AD9959內部結構

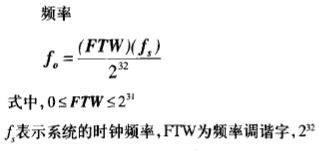

AD9959內部的每個DDS通道都擁有獨立的32bit相位累加器和相位-幅度轉換器。當相位累加開始計時并且相位增量(頻率調諧字FTW)大于0時,相位累加器的輸出數據作為波形存儲器的取樣地址,輸出數字化的正弦波形(梯形正弦波)。相位-幅度裝換器同時將相位信息通過運算轉化為幅度信息。每個通道的輸出頻率(fo)是相位累加器翻轉率的函數。頻率、相位及幅度關系由下面的公式表示:

AD9959具有多種工作模式:單頻(Single Tone)、調制(Modulation)和線掃(Linear Sweep)3種模式。

AD9959串行1/O提供多種配置工作方式,串口兼容ADI早期DDS采用的SPI串行方式。

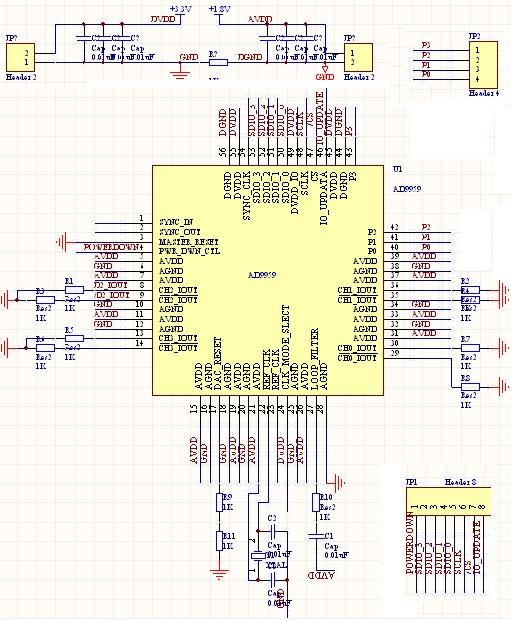

AD9959的運行是主控芯片(單片機、DSP或可編程邏輯)通過串行I/O改寫其內部寄存器值來實現的。因此,寄存器是AD9959的控制核心。控制寄存器主要完成通道選擇,多設備同步及相位累加器清零等功能;通道控制寄存器主要完成各通道功能的選擇,頻率、相位、幅度的設置。各寄存器的使用是通過不同地址的8位數據值來決定。

AD9959在測控通信系統中的應用

多進制正交擴頻信號產生

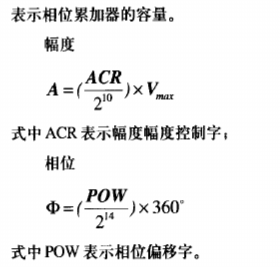

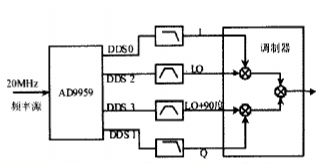

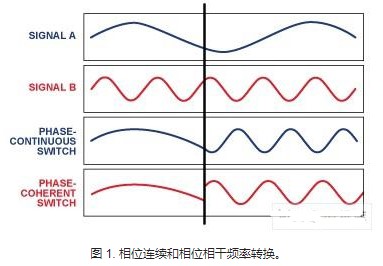

在測控通信系統的設計中系統的可靠性尤為重要,特別是同步不好輕則誤碼率高,重則系統無法正常工作。如圖2所示,在以往的設計中,要成功地同步各路DDS首先要將參考時鐘的相位差最小化,且時鐘邊沿要足夠的陡,以免增加時鐘的相位誤差。其次,數據刷新時鐘(I/O _Update)決定了DDS內部寄存器值的改變時間,多路DDS必須同步改變工作寄存器的值。再次,DDS所需頻率由頻率源經過倍頻鎖相后提供,但這樣會帶來倍頻鎖相后時間信號相位延遲等問題。此外,由于濾波器特性的不一致,也往往會造成已經同步的DDS輸出信號經過濾波平滑處理后進入調制器的信號卻發生失配。因此需要不斷地對FPGA中的控制時序做反復調整。但由于器件之間的差異性與溫度特定的不同,調整好的時序控制程序往往不適用于另一個同樣的電路。諸多因素為信號同步帶來很多麻煩。

圖2 原正交擴頻信號產生方案

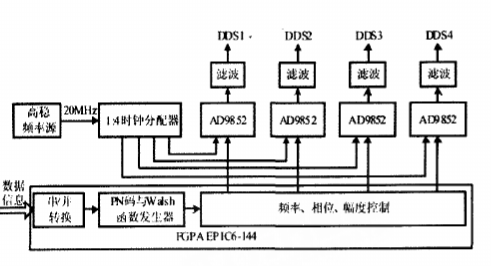

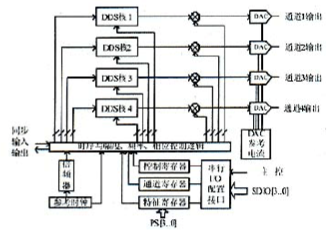

在新方案中,由于單片AD9959集成了4個DDS通道,無需4片AD9852及其外部電路,大大減小了PCB面積。單片AD9959由一組共享的參考時鐘頻率在內部同步4個獨立的DDS通道,在線可編程的通道控制信號隨時調整由外部路徑產生的不均衡性。I、Q數據流可實現良好的正交。即時正交關系和幅度匹配發生輕微的變化,由于其14bit的相位調整和32bit的幅度調整,誤差將保持在很小的可容許的范圍內。上電后FPGA從配置芯片中加載程序,完成發送時序及系統的控制,PN碼和Walsh函數的產生也是由FPGA實現。在FPGA的控制下,4路DDS輸出同步正交信號到專用調制芯片,可產生QPSK、16QAM等多種調制信號,各項指標滿足系統要求,性能穩定。

基于正交信號的上變頻

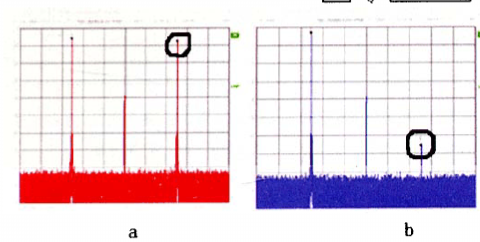

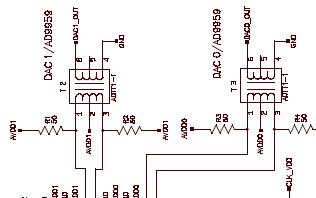

如圖3所示,雖然DDS具有良好的頻率特性和相位特定,但在測控通信系統中設備往往工作在VHF、UHF、L/S/C等頻率較高的頻段,而DDS無法直接滿足UHF頻段以上的頻率要求,必須進行上變頻。通常用鎖相環(PLL)反饋環路中的DDS進行上變頻,但受到PLL的鎖定時間及帶寬的影響,這種方式不適合頻率高速變化的場合。此時,采用AD9959,對兩個正交的DDS通道進行單邊帶上變頻,其中兩路DDS作為I/Q通路,另兩路DDS作為相位相差90度的本振信號源,這種方法非常適合快速跳頻系統,不但保證了本振與I/Q數據的同步而且有效地抑止了冗余邊帶的產生。由于冗余邊帶的顯著減小,濾波器設計難度也大大降低。圖4 比較了采用DDS正交上變頻方案與PLL上變頻的冗余邊帶抑制能力。

圖3 DDS單邊帶抑制載波上變頻

圖4 a 沒有采用正交上變頻的單音頻譜

b 采用DDS正交上變頻的單音頻譜

結語

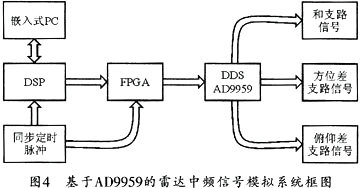

以4通道DDS芯片AD9959為核心的測控通信電路已應用于某無人機測控通信系統中,無論是正交擴頻中還是DDS上變頻都有出色的性能表現。4個DDS核天生同步的特性不僅降低了系統的成本,減小了PCB面積,而且大大簡化了系統同步設計的復雜度,縮短了研發周期。

責任編輯:gt

-

轉換器

+關注

關注

27文章

8741瀏覽量

147677 -

分辨率

+關注

關注

2文章

1071瀏覽量

41988 -

DDS

+關注

關注

21文章

636瀏覽量

152823

發布評論請先 登錄

相關推薦

AD9959控制時序問題

AD9959輸出通道外接電路連接,請問AD9959輸出端口外圍電路如何設計?

請問AD9959 SYNC_CLK能實現輸出信號同步嗎

AD9959調試的相關資料分享

AD9959,pdf datasheet (4-Channe

ad9959應用控制電路

基于AD9959的高精度多通道雷達信號源設計

4通道500MSPS DDS 10位數模轉換器AD9959數據表

利用AD9958/AD9959多通道DDS實現相位相干FSK調制器的設計

基于AD9959多通道DDS器件實現測控通信電路的設計及應用研究

基于AD9959多通道DDS器件實現測控通信電路的設計及應用研究

評論