PCI總線自3.0版本開始支持MSI-X機制,對MSI做出了一些升級和改進,以克服MSI機制的三個主要的缺陷:

1. 隨著系統的發展,對于特定的大型應用,32個中斷向量不夠用了(參考前一篇文章);

2. 只有一個目標地址使得多核CPU情況下的,靜態中斷分配變得困難。如果能夠使每個向量對應不同的唯一的地址,便會靈活很多;

3. 某些應用中的中斷優先級混亂問題。

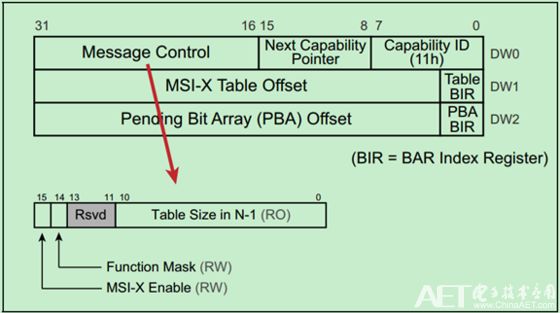

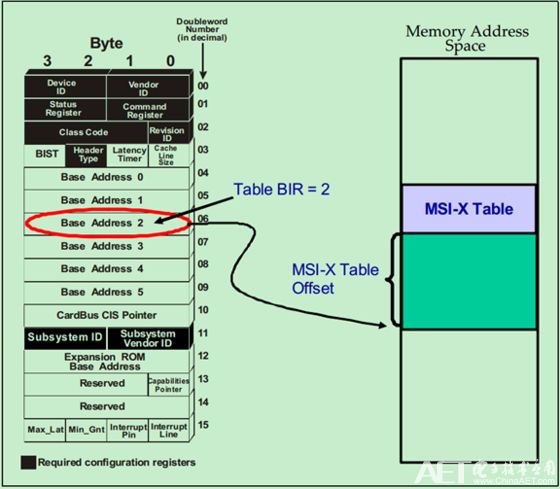

有趣的是,MSI只支持32個中斷向量,而MSI-X支持多達2048個中斷向量,但是MSI-X的相關寄存器在配置空間中占用的空間卻更小。這是因為中斷向量信息并不直接存儲在這里,而是在一款特殊的Memory(MIMO)中。并通過BIR(Base address Indicator Register, or BAR Index Register)來確定其在MIMO中的具體位置。如下圖所示:

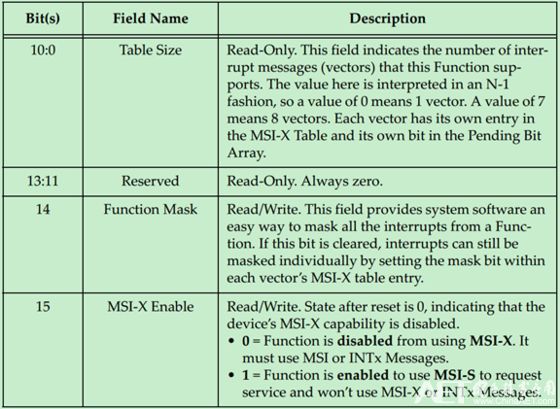

Message Control寄存器的具體描述如下:

MSI-X查找表的示意圖如下:

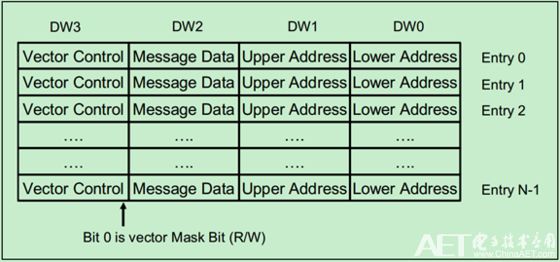

結構圖如下:

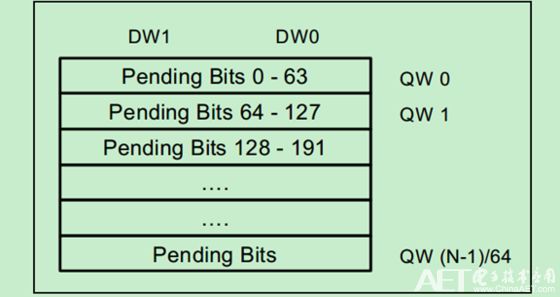

類似的,Pending Bits則位于另一個Memory中,其結構圖如下:

注:無論是MSI還是MSI-X,其本質上都是基于Memory Write 的,因此也可能會產生錯誤。比如PCIe中的ECRC錯誤等。

-

總線

+關注

關注

10文章

2891瀏覽量

88165 -

PCIe

+關注

關注

15文章

1243瀏覽量

82766 -

msi

+關注

關注

0文章

26瀏覽量

29880

原文標題:【博文連載】PCIe掃盲——中斷機制介紹(MSI-X)

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

電路板焊接缺陷的三個方面原因

功放三個技術指標如何測量?

電路板焊接缺陷的三個因素詳述

軟件架構設計的三個維度

PCIe中斷機制介紹(MSI)

醫療人工智能系統的三個關鍵要素和挑戰

PCB焊接缺陷的三個原因資料下載

克服MSI機制的三個主要的缺陷

克服MSI機制的三個主要的缺陷

評論