基于軟件無線電的某機載多模式導航接收機能較好地解決導航體制不兼容對飛行保障區域的限制,但由于各體制信號差異較大,各自實現其硬件將相當龐大,若對本系統中數字信號處理的核心FPGA芯片使用可重構的配置方法,將導航接收機的多種模式以時分復用的方式得以實現,可以重復利用FPGA的硬件資源,達到了縮小體積,減小功耗,增加靈活性和降低系統硬件復雜程度等目的。本系統中的核心器件是新一代高檔FPGA,適合于計算量大的數字信號處理,包含實現數字信號處理的DSP塊、數字鎖相環、硬件乘法器以及各種接口等多項技術,支持遠程更新,但其配置數據大,實現較為復雜。采用CPLD+FLASH方案,有效的解決了這一問題。

1 FPGA及其可重構技術簡介

現代高速度FPGA運行時需將其配置數據加載到內部SDRAM中,改變SDRAM里面的數據,可使FPGA實現不同的功能,即所謂的可重構技術。可重構技術包括靜態系統重構和動態系統重構。在FPGA處于工作狀態時對其部分配置數據進行更改稱為動態配置,否則稱為靜態配置。由于本系統在工作時需要改變整個FPGA功能,所以采用靜態配置。這種配置是完全的,它對整個FPGA的功能、參數完全更改,而且其引腳功能也被更改。

系統的關鍵部件為一片高檔密度FPGA EP2S30,其要求的一次配置數據達1.205MBytes,故其配置采用“Flash存儲器+CPLD主控器”的方案。

EP2S30支持5種配置方案,即AS(Active Serial)模式、PS(Passive Serial)模式、FPP(Fast Passive Parallel)模式、PPA(Passive parallel Asynchronous)模式和JTAG配置模式等。為縮短配置時間,本系統采用FPP模式,配置數據不壓縮,使各配置數據長度一致,以便于分配Flash存儲空間,且只需要同數據率相同的時鐘信號。

2 可重構系統硬件設計

2.1 芯片介紹

2.1.1 FPGA芯片

采用Altera公司StratixⅡ系列FPGA,具有多達33880個等價邏輯單元(LE)和13552個自適應邏輯單元(ALM),支持可編程片上系統(SOPC),有多達1369Kbits片上RAM,支持NIOS嵌入式處理器,片上有多達16個DSP塊和64個18位×18位硬件乘法器以及6個PLL模塊,支持遠程更新。其片內資源完全可以實現系統所需的數字下變頻(DDC)、幅度調制與解調、方位和距離脈沖形成以及控制信號的產生等。但其配置數據達1.205MBytes,要完成多模式可重構配置,其配置數據存儲器必須有足夠大的空間。

2.1.2 Flash芯片

為實現快速配置,綜合存儲容量、工作電壓以及等各方面的要求,Flash芯片選用AMD公司AM29LV065,其為8M×8bits Flash存儲器,內部被分為128個64Kbytes扇區,可以存儲6套配置方案數據。支持3.3V電壓讀寫和擦除,支持扇區擦除和整片擦除,這一特性有利于實現某一配置數據單獨更改。地址不變時能自動進入休眠狀態,將數據鎖存,從而減小功耗。

2.1.3 控制芯片

控制芯片采用Altera公司MAX7000AE系列CPLD EPM7064A,其具有ISP功能,為3.3V內核,IO口靈活方便,避免了采用單片機作為控制芯片時IO口不夠用的問題。

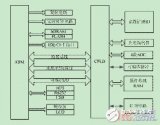

2.2 硬件連接

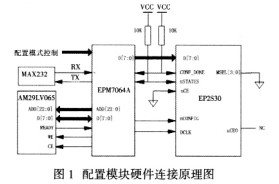

配置系統硬件連接如圖1所示。

配置系統中配置主控制器EPM7064A是整個配置系統的核心,它在數據加載過程中與PC機通訊,產生Flash命令控制字并將配置數據寫入Flash存儲器,同時對Flash存儲空間進行自動分配;在配置過程中根據系統的配置模式控制信號將Flash中的數據讀出并配置到FPGA中,同時完成FPGA配置所需的時序,并檢測FPGA的狀態,若配置成功進入休眠狀態以節省功耗,若配置不成功將對FPGA進行復位并重新配置。

為簡化CPLD的控制時序,便于對FPGA進行自動配置,將Flash的存儲空間按順序劃分為6個塊,分別存儲6個配置數據。每個塊包含20個扇區,1.25MBytes存儲空間。

3 CPLD控制部分軟件設計與實現

3.1 EPM7064A的Verilog HDL描述

EPM7064A是整個配置電路的核心,它完成Flash配置數據的加載和配置時序的產生。按照由上至下的進行設計,將其分成三個主要功能模塊,即數據加載過程中與PC機通訊的UART模塊、寫Flash時序產生模塊和配置時序產生模塊,分別由Verilog HDL硬件描述語言實現。

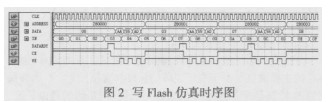

數據加載過程中,EPM7064A的UART模塊與PC機通訊,同時產生Flash編程控制字,將PC機送來的數據寫入指定的塊。其主要工作過程是串口模塊接收到一個字節數據后,其DATARDY有效,觸發Flash寫模塊先將三個控制字數據AA、55、A0寫入Flash,然后將接收到的數據寫入Flash。寫Flash仿真時序圖如圖2所示。

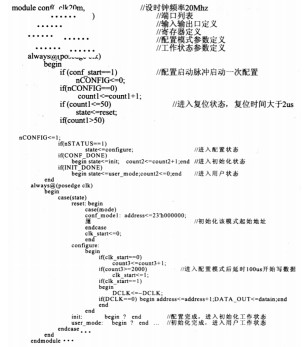

數據讀取和配置時序模塊的主要程序代碼如下:

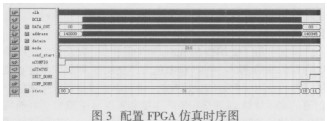

程序代碼在QUARTUSⅡ6.0下的仿真時序如圖3所示。其簡要工作過程是,外部conf_start信號啟動一次配置,EPM7064A將nCONFIG和nSTATUS信號拉低,FPGA進入復位狀態,根據mode取得相應的Flash初始地址,復位完成FPGA將nSTATUS釋放,延時大約100us后EPM7064開始給FPGA提供時鐘和數據,直到將配置數據全部寫入FPGA,配置完成后FPGA將CONF_DONE釋放,表明配置完成,FPGA進入初始化狀態,經過內部初始化后,INIT_DONE變高,表明FPGA進入工作狀態,各引腳將根據用戶定義的狀態工作。若配置過程中nSTATUS被FPGA拉低,則表明有配置錯誤,重新進行配置,在任何工作狀態下外部指令都可以再次啟動配置。

3.2 配置文件的獲取

在FPGA的工程設計編譯后產生的.pof和.sof文件只能直接用于在PS模式下對FPGA進行配置,要用Flash存儲配置數據,需要將配置數據轉換成.hexout或.hex格式,QUARTUSⅡ6.0提供兩種方法得到所需的文件,一是編譯時改變編譯選項自動生成所需文件,二是將已有配置文件轉換為所需文件格式。

4 結束語

將可重構配置方法成功應用于某導航接收機中,充分利用了硬件資源。這種可重構配置方法能根據指令自動更改FPGA配置程序,重構系統功能,實現了多模式導航體制融為一體,系統靈活性和可擴展性大大增強,以較低的成本實現復雜系統,具有一定的工程實用價值。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603013 -

無線電

+關注

關注

59文章

2139瀏覽量

116439 -

導航

+關注

關注

7文章

528瀏覽量

42405

發布評論請先 登錄

相關推薦

基于FPGA的可重構系統結構分析

有什么FPGA可重構方法可以對EPCS在線編程?

基于DSP+CPLD可重構數控系統的設計

基于DSP+CPLD可重構數控系統的設計

基于DSP和CPLD可重構數控系統的設計與仿真

使用CPLD和Flash實現FPGA的配置

基于CPLD的FPGA快速動態重構設計

采用ARM和CPLD結構的檢測系統可重構設計方法

采用CPLD+FLASH方案的可重構配置方法

采用CPLD+FLASH方案的可重構配置方法

評論