前言

隨著電子技術(shù)的飛速發(fā)展 ,計(jì)算機(jī)應(yīng)用的普及,計(jì)算機(jī)與計(jì)算機(jī),計(jì)算機(jī)與數(shù)據(jù)終端,以及數(shù)據(jù)終端與數(shù)據(jù)終端之間的數(shù)據(jù)傳輸與通信的應(yīng)用也日益廣泛。從工業(yè)控制,軍事應(yīng)用,到醫(yī)療儀器,家用電器,到處都涉及到數(shù)據(jù)通信和數(shù)據(jù)傳輸?shù)募夹g(shù)。目前這些數(shù)據(jù)傳輸主要有無線和有線這兩種方式。有線方式由于它的傳統(tǒng)性而在現(xiàn)代的數(shù)據(jù)傳輸領(lǐng)域占據(jù)著主要地位。而無線方式的出現(xiàn)彌補(bǔ)了有線傳輸?shù)牟糠秩毕荩缇€路的成本等。FPGA(FieldProgrammable Gate Array現(xiàn)場可編程門陣列)是一種高密度的可編程邏輯器件,其編程靈活,可在系統(tǒng)編程中通過寫入不同的配置數(shù)據(jù)即可實(shí)現(xiàn)不同的邏輯功能。基于 FPGA設(shè)計(jì)的產(chǎn)品集成度高、體積小、功耗低、開發(fā)周期短,現(xiàn)在很多應(yīng)用產(chǎn)品都是基于 FPGA的開發(fā)。對于應(yīng)用系統(tǒng)而言,只要拿出 FPAG其中的一部分區(qū)域完成特定的專項(xiàng)工作,并不影響其他部分的工作,模塊之間具有相互獨(dú)立性。

1 系統(tǒng)結(jié)構(gòu)

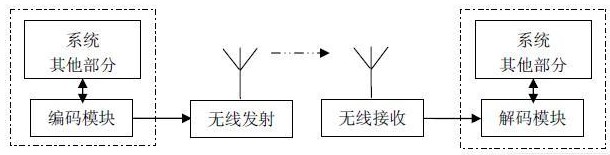

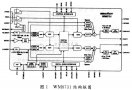

系統(tǒng)分為接收和發(fā)射兩部分,使用非編碼的無線發(fā)射模塊和接收模塊進(jìn)行無線數(shù)據(jù)的傳輸,發(fā)送和接收部分各自具有獨(dú)立的邏輯模塊進(jìn)行編碼或解碼,可以和系統(tǒng)其他部分進(jìn)行數(shù)據(jù)交互,如圖 1。

2.5數(shù)據(jù)接收過程

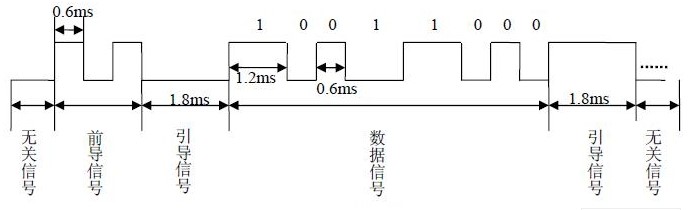

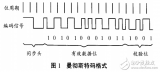

根據(jù)發(fā)送脈沖寬度,很容易判斷信號高低電平,接收采用檢測電平時(shí)間的方法來判斷0、1數(shù)據(jù),過程如下:

①接收到輸入信號變化,重置計(jì)數(shù)器計(jì)數(shù)以判斷前導(dǎo)信號,這里時(shí)間判斷需要有個(gè)裕度,本來是 0.6ms的信號,判斷在 0.3ms—0.9ms是正確的,其他的丟棄處理,如果是有兩個(gè)以上的前導(dǎo)信號就進(jìn)入引導(dǎo)信號的判斷;

②判斷引導(dǎo)信號是不是1.8ms,此處裕度判斷為1.5ms--2.1ms;如果此信號正確,進(jìn)入數(shù)據(jù)接收,否則返回空閑態(tài);

③數(shù)據(jù)接收:數(shù)據(jù)‘0’判斷 0.3ms—0.9ms是正確的,數(shù)據(jù)‘1’ 判斷 0.9ms—1.5ms 是正確的,并將判斷所得數(shù)據(jù)暫放臨時(shí)變量對應(yīng)的位空間,過程中如果出現(xiàn)錯(cuò)誤則作丟棄整個(gè)數(shù)據(jù)處理,返回空閑態(tài);

④數(shù)據(jù)接收完成后,接收引導(dǎo)信號,該信號如果判斷為 1.8ms即以 1.5ms--2.1ms為準(zhǔn)則,則完成數(shù)據(jù)的接收,將暫存數(shù)據(jù)輸出,否則,整個(gè)數(shù)據(jù)丟棄處理,返回空閑態(tài)。

3 實(shí)例仿真

非編碼無線模塊硬件連接只需要電源、地、信號(發(fā)射模塊對應(yīng)輸出,接收模塊對應(yīng)輸入)三根線的電氣連接,使用非常方便。其中要注意的問題就是電源的濾波,因?yàn)闊o線模塊極易受到干擾,也容易干擾外界,所以對模塊的供電要經(jīng)過一定的處理,一般的方法是通過LC網(wǎng)絡(luò)(電感電容網(wǎng)絡(luò))對系統(tǒng)電源進(jìn)行濾波后再對無線模塊供電。試驗(yàn)表明濾波電路的有無對數(shù)據(jù)傳輸?shù)目煽啃杂斜容^大的影響。

對 FPGA的程序可以使用 VHDL語言,Verilog語言,AHDL語言以及圖形等方法進(jìn)行設(shè)計(jì),而在用 VHDL語言的設(shè)計(jì)中,有限狀態(tài)機(jī)的使用使設(shè)計(jì)控制的靈活性和高速運(yùn)算性能大大提高,而且程序的結(jié)構(gòu)清晰明了。

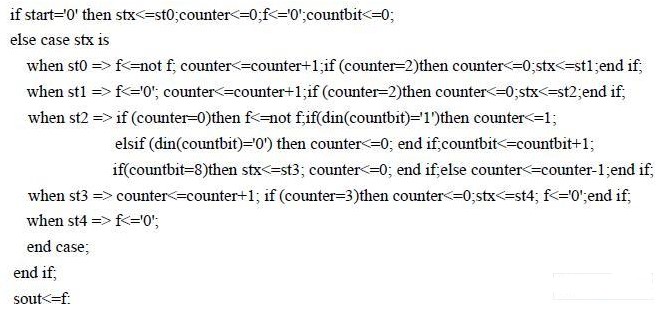

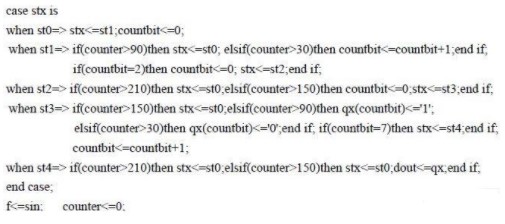

根據(jù)無線模塊的編碼原則與算法,使用 VHDL語言實(shí)現(xiàn)狀態(tài)機(jī),完成無線發(fā)射模塊數(shù)據(jù)編碼發(fā)送的主體程序如下:

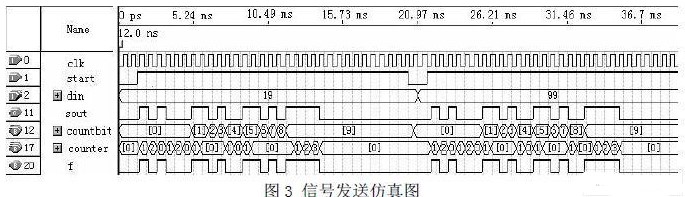

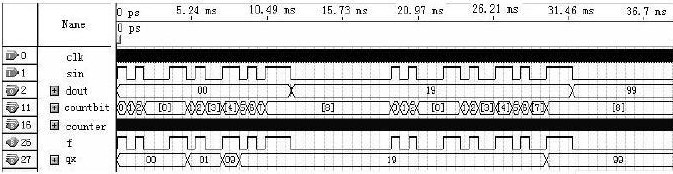

圖 3為數(shù)據(jù)編碼發(fā)送時(shí)序仿真圖形,所發(fā)送的數(shù)據(jù)為十六進(jìn)制的 19H和99H。

根據(jù)無線模塊數(shù)據(jù)接收的解碼方法,使用 VHDL語言實(shí)現(xiàn)狀態(tài)機(jī),完成無線接收模塊數(shù)據(jù)解碼的主體程序如下:

圖 4為數(shù)據(jù)接收解碼時(shí)序仿真圖形,接收數(shù)據(jù)為十六進(jìn)制的 19H和99H。如果在接收數(shù)據(jù)人為加入干擾,這種方式可以有效地將干擾濾除。

4結(jié)論

實(shí)驗(yàn)表明,數(shù)據(jù)可以通過無線模塊使用此編解碼方式進(jìn)行正確傳輸,減少了零電平干擾的影響,而且,此種編解碼方法實(shí)現(xiàn)靈活簡單,占用資源少,具有獨(dú)立性,電路簡潔。設(shè)計(jì)是 8位數(shù)據(jù)的編碼發(fā)送與接收的系統(tǒng)模塊,也適合于單片機(jī)等 8位處理器接口,當(dāng)然這種設(shè)計(jì)可以很方便的擴(kuò)展為 16位或32位等,并增加校驗(yàn)位,提高數(shù)據(jù)的吞吐速度以及數(shù)據(jù)傳輸?shù)目煽啃裕部梢栽黾拥刂返木幋a,實(shí)現(xiàn)單一的點(diǎn)對點(diǎn)通信。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21967瀏覽量

614208 -

無線

+關(guān)注

關(guān)注

31文章

5534瀏覽量

175417 -

計(jì)算機(jī)

+關(guān)注

關(guān)注

19文章

7632瀏覽量

90204

發(fā)布評論請先 登錄

FPGA進(jìn)行視頻編解碼

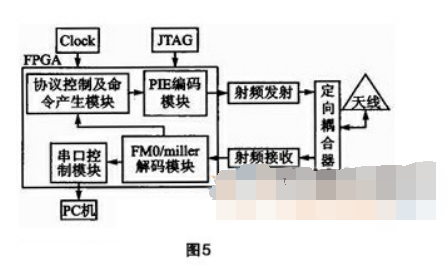

一種基于FPGA的UHF RFID讀寫器編解碼模塊設(shè)計(jì)

基于FPGA的非編碼無線模塊的應(yīng)用設(shè)計(jì)

基于FPGA的非編碼無線模塊的應(yīng)用設(shè)計(jì)

基于FPGA的8B/10B編解碼設(shè)計(jì)

音頻編解碼芯片接口的FPGA應(yīng)用

G.7xx語音編解碼模塊及在AD218X上的實(shí)現(xiàn)

13曼徹斯特碼編解碼的FPGA設(shè)計(jì)與實(shí)現(xiàn)-9

RS編解碼的FPGA實(shí)現(xiàn)-說明

基于FPGA的JPEG實(shí)時(shí)圖像編解碼系統(tǒng)

單片機(jī)實(shí)現(xiàn)無線通信中數(shù)據(jù)的編解碼

如何使用UHF RFID讀寫器編解碼模塊實(shí)現(xiàn)FPGA

RF433和RF315無線模塊的軟件編解碼遙控程序免費(fèi)下載

密勒調(diào)制副載波編解碼器的FPGA實(shí)現(xiàn)

評論