1 、理解Thumb-2

首先,讓我們從一個(gè)看起來并不明顯的起點(diǎn)開始討論節(jié)能技術(shù)—指令集。所有Cortex-M CPU都使用Thumb-2指令集,它融合了32位ARM指令集和16位Thumb指令集,并且為原始性能和整體代碼大小提供了靈活的解決方案。在Cortex-M內(nèi)核上一個(gè)典型的Thumb-2應(yīng)用程序與完全采用ARM指令完成的相同功能應(yīng)用程序相比,代碼大小減小到25%之內(nèi),而執(zhí)行效率達(dá)到90%(當(dāng)針對運(yùn)行時(shí)間進(jìn)行優(yōu)化后)。

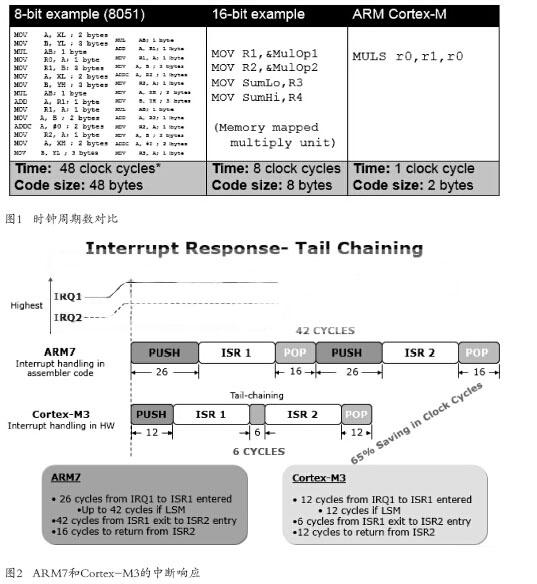

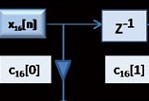

Thumb-2中包含了許多功能強(qiáng)大的指令,能夠有效減少基礎(chǔ)運(yùn)算所需的時(shí)鐘周期數(shù)。減少時(shí)鐘周期數(shù)意味著現(xiàn)在你能夠以更少的CPU功耗完成手頭的工作。例如,假設(shè)要完成一個(gè)16位乘法運(yùn)算(如圖1所示)。在一個(gè)8位8051內(nèi)核的MCU上執(zhí)行這個(gè)運(yùn)算將需要48個(gè)時(shí)鐘周期,并占用48字節(jié)的Flash存儲空間。使用一個(gè)16位內(nèi)核的MCU(例如C166)執(zhí)行相同的運(yùn)算需要8個(gè)時(shí)鐘周期,并占用8字節(jié)的Flash存儲空間。相比之下,在使用Thumb-2指令集的Cortex-M3內(nèi)核中完成相同運(yùn)算僅僅需要1個(gè)時(shí)鐘周期,并占用2字節(jié)的Flash存儲空間。Cortex-M3內(nèi)核能夠通過使用更少時(shí)鐘周期完成相同任務(wù),節(jié)省了能耗;同時(shí)也能夠通過占用極少的Flash存儲空間,減少Flash存儲器訪問次數(shù),實(shí)現(xiàn)最終能耗節(jié)省的目標(biāo)(除此之外,更小的應(yīng)用代碼也使得系統(tǒng)可以選擇更小的Flash存儲器,進(jìn)一步降低整體系統(tǒng)功耗)。

2 、中斷控制器節(jié)能技術(shù)

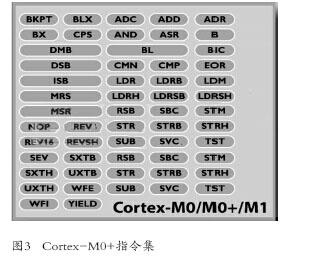

Cortex-M架構(gòu)中的中斷控制器(Nested Vectored Interrupt Controller or NVIC)在降低CPU功耗方面也起著關(guān)鍵作用。以前的ARM7-TDMI需要“多達(dá)”42個(gè)時(shí)鐘周期,Cortex-M3 NVIC從中斷請求發(fā)生到執(zhí)行中斷處理代碼僅需要12個(gè)時(shí)鐘周期的轉(zhuǎn)換時(shí)間,這顯然提高了CPU執(zhí)行效率,降低了CPU時(shí)間浪費(fèi)。除了更快進(jìn)入中斷處理程序之外,NVIC也使得中斷之間切換更加高效。

在ARM7-TDMI內(nèi)核實(shí)現(xiàn)中,需要先花費(fèi)數(shù)個(gè)時(shí)鐘周期從中斷處理程序返回主程序,然后再進(jìn)入到下一個(gè)中斷處理程序中,中斷服務(wù)程序之間的“入棧和出棧(push-and-pop)”操作就要消耗多達(dá)42個(gè)時(shí)鐘周期。而Cortex-M NVIC采用更有效的方法實(shí)現(xiàn)相同任務(wù),被稱為“末尾連鎖(tail-chaining)”。這種方法使用僅需6個(gè)時(shí)鐘周期處理就能得到允許,進(jìn)入下一個(gè)中斷服務(wù)程序的所需信息。采用末尾連鎖,不需要進(jìn)行完整的入棧和出棧循環(huán),這使得管理中斷過程所需的時(shí)鐘周期數(shù)減少65%(如圖2所示)。

3 、存儲器節(jié)能注意事項(xiàng)

存儲器接口和存儲器加速器能夠明顯影響CPU功耗。代碼中的分支和跳轉(zhuǎn)可能會對為CPU提供指令的流水線產(chǎn)生刷新影響,在這種情況下CPU需要延遲幾個(gè)時(shí)鐘周期以等待流水線重新完成填充。在Cortex-M3或Cortex-M4內(nèi)核中,CPU配備了一條3級流水線。刷新整條流水線將導(dǎo)致CPU延遲3個(gè)時(shí)鐘周期,如果有Flash存儲器等待狀態(tài)發(fā)生,時(shí)間會更長,以便完成重新填充過程。這些延遲完全浪費(fèi)功耗,沒有任何功用。為了幫助減少延遲,Cortex-M3和M4內(nèi)核包括一個(gè)被稱為推測取指(Speculative Fetch)的功能,即它在流水線中對分支進(jìn)行取指的同時(shí)也取指可能的分支目標(biāo)。如果可能的分支目標(biāo)命中,那么推測取指能夠把延遲降低到1個(gè)時(shí)鐘周期。雖然這個(gè)特性是有用的,但顯然不夠,許多Cortex-M產(chǎn)品供應(yīng)商都增加了自己的IP以增強(qiáng)這個(gè)能力。

舉個(gè)例子,即使在廣受歡迎的ARM Cortex-M類的MCU中指令緩沖的運(yùn)行方法也有不同。采用簡單指令緩沖的MCU,例如來自Silicon Labs的EFM32產(chǎn)品,可以存儲128x32(512 bytes)的目前大多數(shù)當(dāng)前執(zhí)行指令(通過邏輯判斷請求的指令地址是否在緩沖中)。EFM32參考手冊指出典型應(yīng)用在這個(gè)緩沖中將有超過70%的命中率,這意味著極少的Flash存取、更快的代碼執(zhí)行速度和更低的整體功耗。相比之下,采用64x128位分支緩沖器的ARM MCU能夠存儲最初的幾條指令(取決于16位或32位指令混合,每個(gè)分支最多為8條指令,最少為4條指令)。因此,分支緩沖實(shí)現(xiàn)能夠在1個(gè)時(shí)鐘周期內(nèi)為命中緩沖的任何分支或跳轉(zhuǎn)填充流水線,從而消除了任何CPU時(shí)鐘周期延遲或浪費(fèi)。兩種緩沖技術(shù)與同類型沒有緩沖特性的CPU相比,都提供了相當(dāng)大的性能改善和功耗減少。

4 、M0+內(nèi)核探究

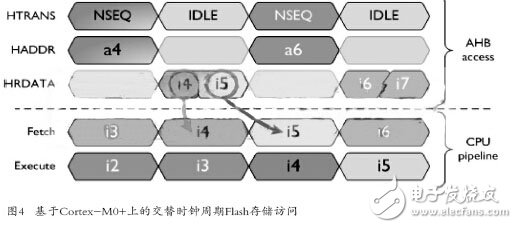

對功耗敏感型應(yīng)用來說每個(gè)nano-watt都很重要,Cortex-M0+內(nèi)核是一個(gè)極好的選擇。M0+基于Von-Neumann架構(gòu)(而Cortex-M3和Cortex-M4內(nèi)核是Harvard結(jié)構(gòu)),這意味著它具有更少的門電路數(shù)量實(shí)現(xiàn)更低的整體功耗,并且僅僅損失極小的性能(Cortex-M0+的0.93DMIPS/MHz對比Cortex-M3/M4的1.25DMIPS/MHz)。它也使用Thumb-2指令集的更小子集(如圖3所示)。幾乎所有的指令都有16位的操作碼(52x16位操作碼和7x32位操作碼;數(shù)據(jù)操作都是32位的),這使得它可以實(shí)現(xiàn)一些令人感興趣的功能選項(xiàng)以降低CPU功耗。

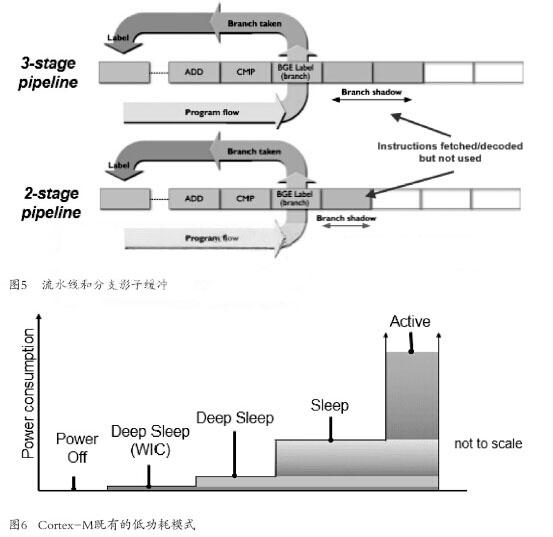

節(jié)能性功能選項(xiàng)首要措施就是減少Flash存儲訪問次數(shù)。一個(gè)主要的16位指令集意味著你可以交替時(shí)鐘周期訪問Flash存儲器(如圖4所示),并且可以在每一次Flash存儲訪問中為流水線獲取兩條指令。假設(shè)你在存儲器中有兩條指令并對齊成一個(gè)32位字;在指令沒有對齊的情況下,Cortex-M0+將禁止剩余的一半總線以節(jié)省每一點(diǎn)能耗。

此外,Cortex-M0+內(nèi)核也可以通過減少到兩級流水線而降低功耗。在通常的流水線處理器中,下一條指令在CPU執(zhí)行當(dāng)前指令時(shí)被取出。如果程序產(chǎn)生分支,并且不能使用下一條取出的指令,那么被用于取指(分支影子緩沖器)的功耗就被浪費(fèi)了。在兩級流水線中,這個(gè)分支影子緩沖器縮小了,因此能耗得以節(jié)省(雖然僅有少量),這也意味著在發(fā)生流水線刷新時(shí),僅需要不到一個(gè)時(shí)鐘周期就能重新填充流水線(如圖5所示)。

5 、利用GPIO端口節(jié)能

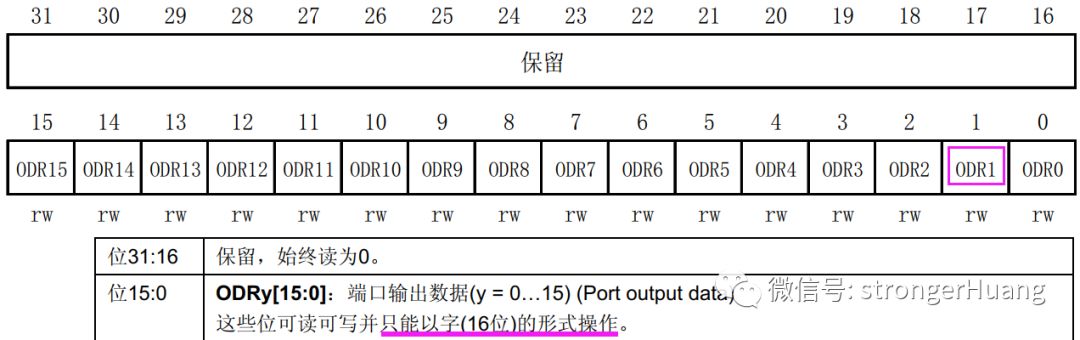

Cortex-M0+內(nèi)核提供節(jié)能特性的另一個(gè)地方是它的高速GPIO端口。在Cortex-M3和Cortex-M4內(nèi)核中,反轉(zhuǎn)一位或GPIO端口的過程是“讀-修改-寫”一個(gè)32位寄存器。雖然Cortex-M0+也可以使用這個(gè)方法,但是它有一個(gè)專用的32位寬I/O端口,可以采用單時(shí)鐘周期訪問GPIO,使得它能夠高效的反位/引腳反轉(zhuǎn)。注意:在Cortex-M0+上,這是一個(gè)可選的特性,并不是所有供應(yīng)商都具備了這個(gè)有用的GPIO特性。

6 、CPU的休眠模式

減少CPU功耗的最有效方法之一是關(guān)閉CPU自身。在Cortex-M架構(gòu)中有多種不同的休眠模式,每一種都在功耗和再次執(zhí)行代碼的啟動(dòng)時(shí)間之間進(jìn)行了折中考慮(如圖6所示)。它也能夠讓CPU在完成中斷服務(wù)后自動(dòng)進(jìn)入某個(gè)休眠模式,而不需要執(zhí)行任何代碼去完成這個(gè)工作。這種方法可以為那些常見于超低功耗應(yīng)用中的任務(wù)節(jié)省CPU時(shí)鐘周期。

在深度睡眠模式下,也可以使用喚醒中斷控制器(WIC)來減輕NVIC負(fù)擔(dān)。在使用WIC時(shí),為實(shí)現(xiàn)低功耗模式下外部中斷喚醒CPU,無需為NVIC提供時(shí)鐘。

7、 自主型外設(shè)可減輕CPU負(fù)荷

自主型片上外設(shè)具有降低功耗的優(yōu)點(diǎn)。大多數(shù)MCU供應(yīng)商已經(jīng)在本身產(chǎn)品架構(gòu)中實(shí)現(xiàn)了外設(shè)之間的自主型交互,例如Silicon Labs的EFM32 MCU使用的外設(shè)反射系統(tǒng)(PRS)。自主型外設(shè)能夠?qū)崿F(xiàn)十分復(fù)雜的外設(shè)動(dòng)作鏈(觸發(fā)而不是資料傳輸),同時(shí)保持CPU處于休眠狀態(tài)。例如使用EFM32 MCU上的PRS功能,應(yīng)用能夠被配置為在CPU休眠的低功耗模式下,當(dāng)片上比較器檢測電壓值超過了其預(yù)設(shè)的門限值,則觸發(fā)一個(gè)定時(shí)器去開始減數(shù)。當(dāng)定時(shí)器到達(dá)0時(shí),觸發(fā)DAC去開始輸出 — 所有事件發(fā)生過程中CPU可以一直保持休眠狀態(tài)。

自動(dòng)進(jìn)行如此復(fù)雜的交互,這使得外設(shè)之間能夠完成大量工作而無需CPU參與。此外,帶有內(nèi)建智能的外設(shè)(例如傳感器接口或脈沖計(jì)數(shù)器)能夠通過預(yù)設(shè)的條件用于中斷喚醒CPU,例如在累積10個(gè)脈沖時(shí)中斷喚醒CPU。在這個(gè)例子中,當(dāng)CPU被特定中斷喚醒時(shí),它明確知道需要做什么,而不需要檢查計(jì)數(shù)器或寄存器以判別發(fā)生了什么,因此可以節(jié)省相當(dāng)多的時(shí)鐘周期,更好的完成其他重要任務(wù)。

我們已經(jīng)介紹了多種易于實(shí)現(xiàn)的減輕Cortex-M設(shè)備上CPU功耗的方法。當(dāng)然,還有其他因素影響功耗,例如用于加工設(shè)備的處理工藝或者用于存儲應(yīng)用代碼的存儲器技術(shù)。工藝和存儲技術(shù)能夠顯著影響運(yùn)行時(shí)功耗和低功耗模式下的漏電,因此也應(yīng)當(dāng)納入嵌入式開發(fā)人員的整體功耗設(shè)計(jì)考慮之中。

-

控制器

+關(guān)注

關(guān)注

112文章

16416瀏覽量

178784 -

存儲器

+關(guān)注

關(guān)注

38文章

7521瀏覽量

164089 -

cpu

+關(guān)注

關(guān)注

68文章

10890瀏覽量

212407

發(fā)布評論請先 登錄

相關(guān)推薦

ARM Cortex-M的音頻性能解析

為什么說Cortex-M是低功耗應(yīng)用的首選

如何使用Ozone分析Cortex-M異常

你總得知道你為什么要用Cortex-M

基于Cortex-M處理器的高精度關(guān)鍵詞識別實(shí)現(xiàn)

如何在Cortex-M處理器上實(shí)現(xiàn)高精度關(guān)鍵詞的識別

介紹Cortex-A和Cortex-M的TrustZone之間的差異

介紹易于使用的Arm Cortex-M處理器上的信號處理功能

Azure RTOS是否可用于STM32MP1設(shè)備的Cortex-M呢?

降低ARM Cortex-M CPU功耗的技巧分析

米爾科技Cortex-M Prototyping System +介紹

Cortex-M中斷向量表原理及其重定向方法~

分享一下Cortex-M裸機(jī)環(huán)境下臨界區(qū)保護(hù)的幾種實(shí)現(xiàn)方法

實(shí)現(xiàn)減輕Cortex-M設(shè)備上CPU功耗的方法和技巧

實(shí)現(xiàn)減輕Cortex-M設(shè)備上CPU功耗的方法和技巧

評論