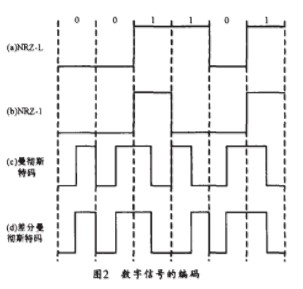

圖1所示是數據通信系統的基本構成。在計算機通信中,通信雙方傳遞的信息必須進行量化并以某種形式進行編碼后才能進行傳輸。機內信號不論采用哪一種編碼方法,它們的基本信號都是脈沖信號,為了減少信號在傳輸媒質上的通信帶寬限制,以及噪音、衰減、時延等影響,也由于同步技術的需要,操作時都需要對簡單的脈沖信號進行一些不同的變換,以適合傳輸的需要。這樣就會產生許多不同的代碼,通常有不歸零電平(NRZ-L)碼,逢“1”反轉(NRZ-1)碼,曼徹斯特碼和差分曼徹斯特等。圖2所示是部分編碼方式的波形圖。

由圖2可知,不歸零碼的制碼原理是用負電平表示“0”,正電平表示“1”,其缺點是難以分辨一位的結束和另一位的開始;發送方和接收方必須有時鐘同步;若信號中“0”或“1”連續出現,信號直流分量將累加。這樣就容易產生傳播錯誤。曼徹斯特碼(Manchester)的原理是每一位中間都有一個跳變,從低跳到高表示“0”,從高跳到低表示“1”。這種編碼方式克服了NRZ碼的不足。每位中間的跳變即可作為數據,又可作為時鐘,因而能夠自同步。曼徹斯特編碼特點是每傳輸一位數據都對應一次跳變,因而利于同步信號的提取,而且直流分量恒定不變。缺點是數據編碼后,脈沖頻率為數據傳輸速度的2倍。差分曼徹斯特碼(Differential Manchester)的原理是每一位中間都有一個跳變,每位開始時有跳變表示“0”,無跳變表示“1”。位中間跳變表示時鐘,位前跳變表示數據。這種方式的優點是時鐘、數據分離,便于提取。

2 曼徹斯特編解碼器的設計

可編程邏輯器件的出現為數字系統的設計帶來了很大的靈活性.而VHDL (VHSIC HardwareDescription Language)是一種功能強大的硬件設計語言,可用簡潔的代碼來進行復雜控制邏輯的設計。為此,本文采用VHDL語言來對曼徹斯特編解碼器進行描述,并用Active-HDL進行編譯,最后用Synplify進行綜合。

2.1 解碼

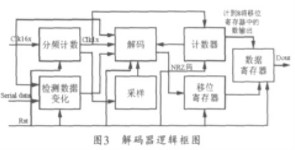

根據曼徹斯特碼的特點,可將該碼的解碼過程分成三部分:一是啟動解碼時鐘,即通過檢測一個數據跳變沿來使能時鐘。二是對曼徹斯特碼形式的數據進行解碼。三是將串行數據轉換成并行數據。解碼器的邏輯框圖如圖3所示。

該邏輯可南進程實現。輸人的時鐘為clkl6x的時鐘,串行的曼徹斯特碼的數據與單倍的時鐘相對應。首先,串行的曼碼由clk16x的時鐘采樣,之后再將采樣到的數據先后存放在兩個寄存器中,當兩個寄存器中的值不一致時,即開始解碼過程,從而完成檢測數據變化的進程。分頻計數進程用來產生clklx,并用分頻計數的結果來實現1/4和3/4點的采樣。根據曼徹斯特碼的性質,對1/4和3/4點采樣可以準確的恢復成NRZ碼。此后在clklx的驅動下,控制字計數器開始計數,直到8個clklx之后,計數器歸零。解碼進程則在clkl6x的驅動下,對1/4和3/4采樣點的數據進行解碼,從而得到曼碼相對應的NRZ碼。緊接著將解碼得到的每一位NRZ碼移入8位的移位寄存器,當控制字寄存器計到8時(即8位移位寄存器溢出的時候),再將8位NRZ碼一起輸出到數據寄存器,最后輸出數據寄存器中被解碼好的NRZ碼。

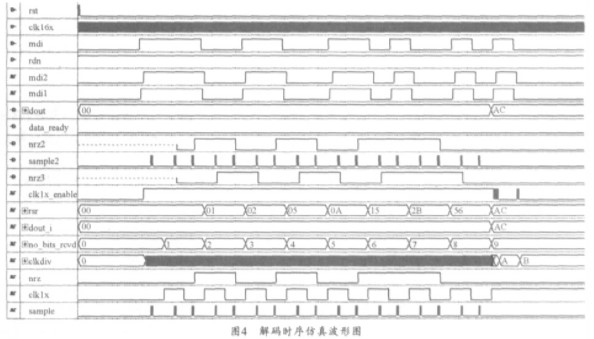

圖4所示是采用該設計的曼徹斯特碼的時序仿真波形,clkl6x采用16 MHz的時鐘,mdi為輸入的曼碼(10101100)。最后輸出dout為十六進制AC,這說明該解碼過程是正確的。

2.2 編碼

編碼是解碼的逆過程。編碼的過程也可以分為兩部分:一是檢測編碼周期是否開始,以決定產生正跳變沿;二是對串行的數據進行編碼,之后編碼周期結束。編碼器的輸入時鐘(clk2x)為2MHz。當寫信號(wr)為高電平時,開始產生正跳變沿,并使clklx-enable為高電平,這樣,正跳變沿產生完成即開始編碼過程。將clk2x進行二分頻可得到clklx,這樣可使歸零制的數據(nrz)與clklx相對應。此后再在clklx_enable高電平和clk2x正跳變的情況下,將歸零制碼(nrz)轉換成相應的曼徹斯特碼(meo)。最后,當寫信號(wr)為低電平時,以使clklx_enable為低電平,結束編碼過程。

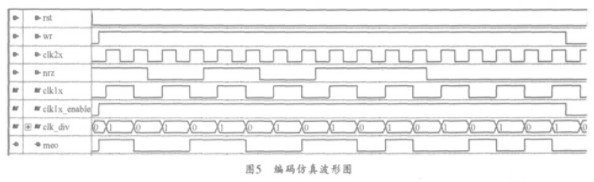

圖5所示其編碼時序仿真波形圖,圖中,clk2x采用2MHz的時鐘,nrz為串行輸入的歸零制碼(10101100),meo為串行輸出的曼徹斯特碼。由圖可見,從剛開始的跳變沿之后,輸出meo也為10101100,證明編碼過程正確。

3 基于CPLD的曼徹斯特碼實現

為了確保設計的可行性,操作時必須對設計進行時序仿真。為了提高CPLD芯片的性能及資源利用率,應采用專門的綜合軟件來對設計進行優化和綜合。本設計采用Synplify7.3進行綜合,并采用Active-HDL6.1進行時序仿真。在Synplify中使用有效的代碼可以優化組合邏輯、減少邏輯延時,從而提高整體性能。此外,本設計還進行了多個文件的分塊設計,然后將這些文件映射到頂層文件進行綜合,并運用VHDL對單個文件進行編寫、仿真和優化。在用到組合邏輯時,Syn-plify會盡量避免鎖存器的出現,節省邏輯單元。Synplify和其它綜合軟件一樣,編譯后所生成的電子設計交換格式文件(EDIF)可以在Active-HDL中進行編譯、仿真、分配引腳和其它優化處理。因此,采用Active-HDL6.1和Synplify7.3相結合對CPLD進行設計、優化、綜合,可以提高系統性能和

芯片資源的利用率。

CPLD(Complex Programmable Logic Device復雜可編程邏輯器件)的內部結構為“與或陣列”。該結構來自于典型的PAL、GAL器件結構。由于任意一個組合邏輯都可以用“與一或”表達式來描述,所以該“與或陣列”結構能實現大量的組合邏輯功能。CPLD和FPGA的主要區別如下:

(1) 布線能力

CPLD內連率高,不需要人工布局布線來優化速度和面積,較FPGA更適合于EDA芯片設計的可編程驗證;

(2) 延遲可預測能力

CPLD連續式布線結構決定了時序延時是均勻的和可預測的,而FPGA的分段式布線結構則決定了其不可預測時間延遲;

(3) 集成度的不同

CPLD的集成度一般在500~50000門。而FP-GA的集成度一般在1K~10M門;

(4) 應用范圍的不同

CPLD邏輯能力強而寄存器少,適用于控制密集型系統,而FPGA邏輯能力較弱但寄存器多,適于數據密集型系統。

CPLD和FPGA的共同優點一是規模越來越大,實現功能越來越強,同時可以實現系統集成。二是研制開發費用低,不承擔投片風險,使用方便。三是通過開發工具在計算機上完成設計,電路設計周期短,同時不需要設計人員了解很深的IC知識,EDA軟件易學易用。此外通過FPGA和CPLD開發的系統成熟后,還可以進行A-SIC設計,以形成批量生產。

事實上,本設計在Xilinx公司的XC9500系列CPLD(xc95108pq100-7)芯片上進行了實現。并針對其特點對設計進行了最后的優化。該編解碼器共占用了149個邏輯單元,占總邏輯資源的8%,因此,十分有利于今后對其進行完善和功能的添加。

4 結束語

本設計具有一定的通用性,它的邏輯大部分只涉及到編、解碼器本身;而它與外部的接口十分簡單,只要對其讀、寫并對跳變沿信號進行有效控制,就能使其正常工作。本設計十分獨立,由于選用器件資源比較豐富,故對其進行功能添加也十分方便,只需添加電路設計而不必對原有電路進行修改。

-

芯片

+關注

關注

455文章

50756瀏覽量

423341 -

解碼器

+關注

關注

9文章

1143瀏覽量

40725 -

cpld

+關注

關注

32文章

1248瀏覽量

169343

發布評論請先 登錄

相關推薦

采用復雜控制邏輯器件和VHDL語言實現曼徹斯特編解碼器的設計

CPLD XC9500是否有任何序列?

XC9500系列CPLD遙控編程該怎么設計?

編解碼器的工作原理是什么?

基于CPLD的卷積碼編解碼器的設計

EDA卷積碼編解碼器實現技術

用FPGA實現1553B總線接口中的曼碼編解碼器

基于FPGA的曼徹斯特編解碼器設計

在XC9500系列CPLD芯片上實現曼徹斯特碼編解碼器的設計

在XC9500系列CPLD芯片上實現曼徹斯特碼編解碼器的設計

評論