一、 引言

DSP芯片,也稱數字信號處理器,是一種特別適合于進行數字信號處理的微處理器。我們在進行產品的開發過程中,往往需要對信號進行實時處理,就是指系統必須在有限的時間內對外部輸入的信號完成指定的處理功能,也就是說信號處理速度應大于信號更新的速度,而DSP芯片的處理器結構、指令系統和數據流程方式,使其很容易滿足實時信號處理的要求。DSP的應用幾乎已遍及電子與信息的每一個領域,本文沒有必要對其應用一一羅列,也不打算再花不必要的篇幅來介紹DSP的結構和原理,因為這方面的書籍和資料也較多。本文結合作者基于TI公司C5510系列DSP負責完成的某國防科研項目的基帶信號處理的一點感悟,談談C55x系列DSP在基帶信號處理中的應用和實現,因為目前介紹C54x系列DSP的資料已不少,而介紹C55x系列DSP的書籍和資料卻相對太少。雖然C55x和C54x都屬于TI的C5000系列的產品,很多書籍往往僅以“C54x與C55x在軟件上完全兼容”來一筆代過。但對于一個DSP開發者來說,卻不是這么簡單的事,我們考慮的不僅僅是其功能的實現,也好考慮如何去優化和利用資源。所以有必要研究一下C55x在C54x基礎上的改進功能,探討一下C55x的應用問題。

二、 C55x與C54x比較

C54x系列是針對低功耗、高性能的高速實時信號處理而專門設計的定點DSP,廣泛應用于無線通信系統中,它的CPU具有下列特征:

⑴ 采用改進的哈佛結構,一條程序總線(PB)、三條數據總線(CB、DB、EB)和四條地址總線(PAB、CAB、DAB、EAB);

⑵ 40bit的算術邏輯單元(ALU)以及一個40bit的移位器和兩個40bit的累加器(A、B),支持32bit或雙16bit的運算。

⑶ 17bit×17bit的硬件乘法器和一個40bit專用加法器的組合(MAC)可以在一個周期內完成乘加運算;

⑷ 比較、選擇和存儲等單元能夠加速維特比譯碼的執行。

⑸ 專用的指數編碼器(EXP encoder)能夠在一個周期內完成累加器中40bit數值的指數運算。

⑹單獨的數據地址產生單元(DAGEN)和程序地址(PAGEN)產生單元,能夠同時進行三個讀操作和一個些操作。

C55x通過增加功能單元,與C54x相比,其綜合性能提高了5倍,而功耗僅為C54x的1/6。C55x采用變長指令以提高代碼效率,增強并行機制以提高循環效率,不僅僅增加了硬件資源,也優化了資源的管理,所以性能得到了大大的提高,其處理能力可達400~800MIPS。C55x在CPU的功能單元方面作了如下擴展:

⑴ 總線增加了兩條,一條讀操作線(BB),一條寫操作線(FB);

⑵ 乘加單元(MAC)增加了一個;

⑶ 增加了一個16bit的ALU;

⑷ 將累加器增至4個,即AC0、AC1、AC2和AC3;

⑸ 臨時寄存器增至4個,即T0、T2、T2和T3;

由于結構上的變化,我們在系統設計中必須注意C55x和C54x寄存器的變化關系,尤其是當我們在C55x設計中采用與C54x的兼容模式,而不是增強模式,這更為重要。下表為C54x和C55x的寄存器對應關系。

C55x雖然也能兼容C54x,在C55x DSP上也能運行C54x的指令,但C55x與C54x又是不同的,C55x在指令上作了較大的簡化。比如,相對C54x的裝載(LD)與存儲(ST),C55x用更加靈活易用的MOVE操作指令來實現裝載和存儲,將MOVE操作的范圍擴大到數據交換、堆棧操作等。另外,在兼容模式中,我們要注意XC、SACCD和ARx+0等情況的使用。

三、 C5510 在基帶信號處理中的應用

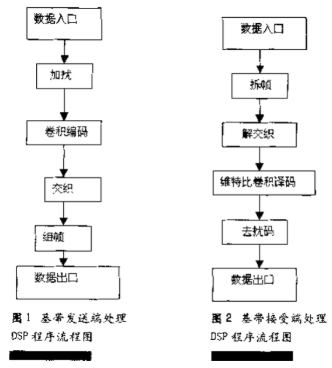

下面結合作者參加的某國防項目具體談談C5510在通信系統的基帶信號處理中的應用和實現,由于篇幅所限,僅給出程序流程圖,源代碼略。

1.基帶信號處理中DSP的任務

本系統基帶信號的處理中,DSP主要完成對數據進行加擾和解擾、卷積編碼和VITERBI譯碼、交織和解交織、成幀(或子幀)和拆幀等處理。首先,針對主傳數據進行隨機化加擾(采用外同步預置式,使用n=17級的m序列),再進行(2,1,7)卷積編碼,約束長度K=7的卷積碼,生成多項式為(用8進制表示):1+D+D^2+D^3+D^6=(171),八進制g1=171,G1=1+D^2+D^3+D^5+D^6=(133),八進制,g2=133,故每次編碼前需加尾比特K-1=6位。編碼后一子幀內的比特數為50(考慮了在一個大幀范圍內對控制信息比特所占傳輸速率的補償)。再加上每個子幀的控制信息比特(如子幀數據類型比特)后,一個子幀的有效比特數為56,然后經過7×8的分組塊交織,加上8比特同步保護碼,最終成為一個64bit的子幀,經緩存等處理后送給調制器。

2.基于C5510基帶信號處理實現

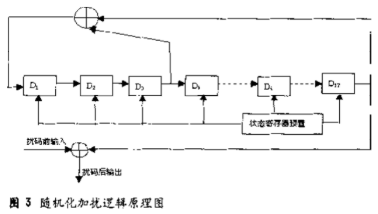

A.數據加擾與解擾

加擾使用n=17級的m序列來實現,其生成多項式的8進制表示為g=400011,多項式f(x)=x17+x3+1,有三個反饋抽頭。并采用外同步預置式,減少誤碼擴散。每傳送一個大幀(含20個子幀),觸發預置式脈沖一次,脈沖預置可用軟件方式實現。加擾、解擾邏輯原理如圖3所示,加擾和去擾只需循環使用C55x的XOR src,dst就可以解決,因而不需詳說。

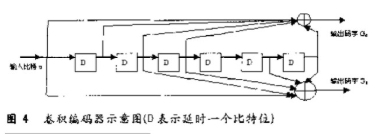

B.卷積編解碼

采用了性能相對比分組碼好的卷積碼(2,1,7),其限制長度K=7,生成多項式(8進制表示)G0=171,G1=133,自由距離df=10,漸近編碼增益Gh=3.98dB。卷積碼編碼器的原理示意圖如下圖所示。

卷積編碼器的輸出序列是G0 G1 G0 G1 G0 G1.。..。.,在DSP C5510編程中,可以采用指令BFXPA來完成輸出序列的排列這樣就可以在程序中多次調用這個宏文件,從而簡化和縮短源程序,具體實現時可以定義一個宏:

merge .macro src1,src2,temp,dst ;宏定義

BFXPA #5555h,src1,temp ;抽取src1偶數位置的比特位

BFXPA #0AAAAh,src2,temp ;抽取src2奇數位置的比特位

XOR temp,dst ;兩者取異或運算

SFTL src1,#-8,src1 ;src1右移8位

SFTL src2,#-8,src2 ;src2也右移8位

.endm

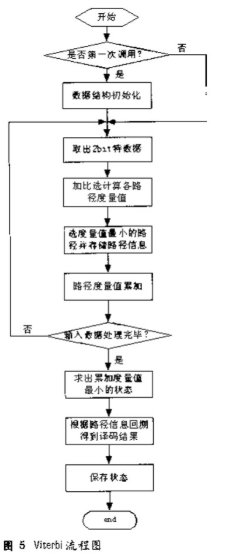

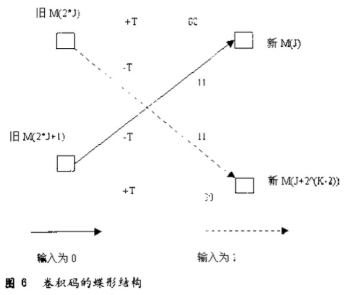

卷積碼譯碼采用最大似然譯碼器—維特比譯碼。其流程如圖5所示。

其算法思想是:

① 從時間單位j=m開始,計算進入每一狀態的單個路徑的部分量度并存貯量度的路徑及其量度。這樣的路徑稱為幸存路徑。

② j增加1,將進入某一狀態部分分量度與前一時間單元有關的幸存路徑的量度相加。計算進入該狀態所有路徑的部分量度。對每一狀態存貯具有最大量度的路徑,即幸存路徑及其量度,刪去所有其他的路徑。

③ 若j《(L+m),重復步驟②,否則就停止。此處L為碼字長,m=6。

對分支度量值得計算采用軟判決,也即歐氏距離,對于編碼速率為1/2的卷積碼,它的分支度量值為:

T=SD0 G0 (j)+ SD1 G1 (j)

為了計算的簡便,Gn (j)用雙極性表示,0用+1表示、1用-1表示,或相反,這樣分支度量值的計算就可以簡化為數據的加和減。在DSP實現過程中就可以分別用寄存器來表示:

T0: + SD0 + SD1

T1: + SD0 -SD1

在C55x中可以用特殊應用指令ADDSUB、SUBADD和MAXDIFF來完成各個狀態路徑度量值的累加、比較和選擇,而且可以充分運用C55x的流水線處理優勢。為了方便調用,可以將利用流水線處理的維特比蝶形運算定義為一個宏。

C.交織與解交織

一般的糾錯編碼是針對隨機性錯誤的,但在無線信道中產生的錯誤多屬于突發性差錯,因此我們使用了交織技術,將突發性差錯離散成隨機差錯,實際上是一種隱分集技術,可獲得抗深度衰落的效果。但交織對系統會帶來時延上的影響,綜合考慮系統的糾錯性能與復雜性,采用了一個子幀中56bit進行分組塊交織的方式。如用矩陣形式處理,即在發端以行寫入,收端以列讀出。當然也可發端以列寫入,收端以行讀出。

在C55x中實現交織時,可以用AR0指向待交織數據的輸入緩沖地址,AR1指向交織表,AR2指向完成交織的數據的地址。AR1每次加1,對應于AR2所指交織數據字的比特位置也加1,指向的內容是輸入緩沖區的地址偏移量,此偏移量指向的比特就是需要交織到AR2指向字的比特位置。程序的重要結構相當于有兩層循環,在外層循環中指針AR2每次加1,對應內層循環執行16次。去交織是交織的逆過程,需要使用相同的的交織表,程序結構也和交織大致相同,但比特搬移方向相反,因而在編程實現過程中,只需將交織程序稍加修改就可以。

四、 總結

隨著DSP技術的迅猛發展,芯片集成度的提高也使DSP芯片成本降低,這使DSP的需求上升和應用領域的擴展,DSP已從軍用轉向民用,在整個電子信息領域得到了廣泛的應用,越來越多的人開始或從事DSP的設計和研發。我們知道,現代通信系統中的數字化、寬帶化、智能化和多媒體化要求都對信號的處理提出了很高的要求,一片DSP往往只能進行物理層處理,而不能完成處理控制和高層信令,因此DSP有必要與另外的處理器相結合。TI 公司將C55x DSP核與控制性能強的ARM9微處理器結合起來,推出了開放式多媒體應用平臺(OMAP)。可以預計,DSP與其它微處理器的結合是DSP未來的發展方向。

責任編輯:gt

-

dsp

+關注

關注

553文章

8030瀏覽量

349319 -

芯片

+關注

關注

456文章

50936瀏覽量

424681 -

編碼器

+關注

關注

45文章

3649瀏覽量

134745

發布評論請先 登錄

相關推薦

基于DSP的圖像處理系統的應用研究

TMS320C55x DSP是什么?有什么應用?

基帶信號處理子系統

TDRSS基帶信號處理系統的FPGA實現

DSP+FPGA實現語音基帶處理系統

TMS320C55x DSP并行處理技術分析

TMS320VC55X的DSP的多通道緩沖串口(MCBSP)的詳細資料概述

TMS320C55x EMIF號和DSP與各種類型的必要信號連接SDRAM的討論

定點DSP C55x音頻專用處理器嵌入式教學

基于C55x DSP核芯片實現基帶信號處理系統的設計

基于C55x DSP核芯片實現基帶信號處理系統的設計

評論