引 言

為了保證機載電臺的設計性能和通信質量,并且各種電臺都有各自詳細的技術指標要求,需要使用很多臺單一功能的儀器或綜合檢測儀來測試。目前,產生穩定可靠、符合要求的跳頻信號已成為進行跳頻關鍵技術驗證、通信設備開發預研,綜合測試系統研制的瓶頸。本設計正是某機載電臺綜合檢測儀的一部分,為其提供一個高穩定度的跳頻信號源。

由于FPGA 器件速度快、密度高、功耗低、可配置性強, 現已在許多領域得到了廣泛的應用。硬件描述語言的出現使FPGA 的設計更加方便、快捷。DDS 技術具有頻率轉換速度快、分辨率高及相位噪聲特性好等優點,但組合干擾信號多,難以控制,無法適應跳頻通信的要求。而PLL 技術具有控制靈活、體積小、電路簡單、雜散抑制度高及頻譜純度高等一系列優點,是當今戰術電臺的主流技術方案,但面臨高速的技術要求,鎖相環路的固有慣性已成為嚴重的障礙。因此,本設計以FPGA(EP1C12)為核心進行跳頻控制,采用DDS(AD9850)與PLL(MC145152)相結合,由DDS 提供快速跳頻的小步進間隔,PLL 工作在大步進間隔,增大環路帶寬,縮小跳頻時間,而且完成對雜散的抑制。在此硬件平臺上加載相應的程序,可以產生所需的跳頻信號,具有轉換速率快、電路簡潔、系統控制簡易靈活等優點。

1. 信號發生器的硬件設計

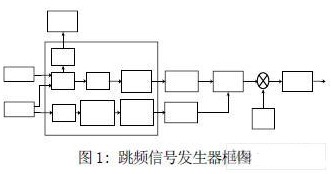

圖1 所示是跳頻信號發生器組成框圖。整個硬件系統分為基帶子系統、中頻子系統和射頻子系統三部分:

1)基帶子系統包括FPGA 和其外部所需的D/A 轉換器(包括其所需的波形成型濾波器)、按鍵開關、數碼管電路以及撥碼開關。

該子系統主要以FPGA 為核心,,首先FPGA 從撥碼開關和鍵盤電路采集信息數據并通過顯示電路顯示,然后對這些獲取的信息數據進行BFSK 調制,產生BFSK 波形的樣點值,經D/A 轉換器和成型低通濾波器產生BFSK 的基帶模擬波形,同時,FPGA 還產生跳頻碼序列,通過預設的跳頻圖案表,最后獲得產生該頻率信號所對應的DDS 控制字,并將該控制字寫入DDS 之中和對DDS 發出頻率切換的指令。FPGA 以1000 次/秒的頻率來更新DDS 輸出的頻率,這樣,在DDS 就能產生了1000 跳/秒的跳變中頻載波信號。

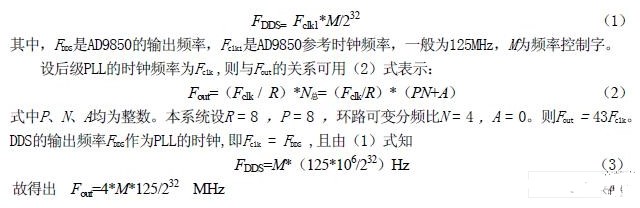

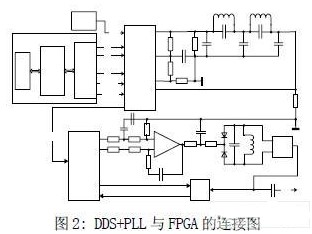

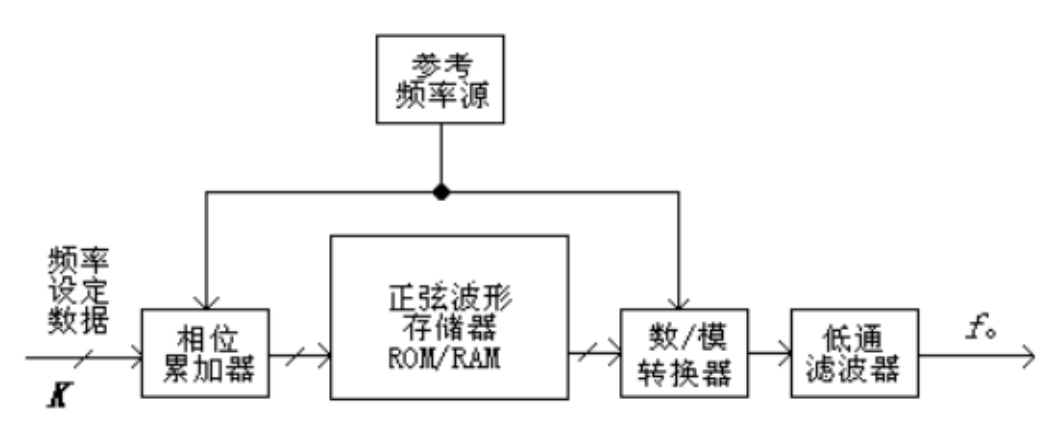

2)中頻子系統包括DDS+PLL、混頻器、中頻濾波器。在跳頻信號產生過程中頻率合成器是其中的關鍵技術之一,在本設計中,DDS選用的是AD公司的AD9850,在125MHz時鐘信號的驅動下,可以產生分辨率為4.492Hz的信號。雖然DDS優點突出,但是它的輸出頻率不高,不能滿足設計所需的44.625~90.125MHz跳頻范圍,因此必須通過PLL倍頻。具體實現電路是AD9850的輸出經低通濾波后作為時鐘驅動鎖相環MC145152。如圖2所示為FPGA采用并行輸入方式與DDS+PLL的連接圖。對于PLL,其換頻時間Ts1與鑒相頻率有關,工程上近似為Ts1 = 25/ Fr = 25R/ Fclk,其中Fclk就是DDS的輸出頻率。在本系統中,R= 8,FDDS的范圍是20. 5MHz ~22. 5MHz。所以Ts1的量級是十幾μs量級,即Ts的量級也是十幾μs量級,因此完全能滿足1000跳/秒的指標。根據AD9850的相關特性可知,其輸入和輸出頻率的關系為:

其中M 為頻率控制字。從(4)式也可知該頻率合成器的分辨率為4*3*125/ 232MHz=1.164Hz。由此可知,完全能夠滿足本設計對頻率合成器的要求。

BFSK 基帶信號與DDS 產生跳變的載波信號在混頻器中混頻后再產生跳變的中頻信號(44.625~90.125MHz)經濾波后送入射頻電路。

3)射頻子系統有頻率合成器、混頻器、濾波器等構成,其中頻率合成器采用的是有固定頻率輸出的由鎖相環路構成的頻率合成器,以產生200MHz 的輸出頻率作為本振頻率。中頻寬帶信號(44.625~90.125MHz)與本振頻率在混頻器中混頻后,經過帶通濾波器取上邊帶,得到(109.875~155.375MHz)的跳頻信號。

2. 信號發生器的軟件實現

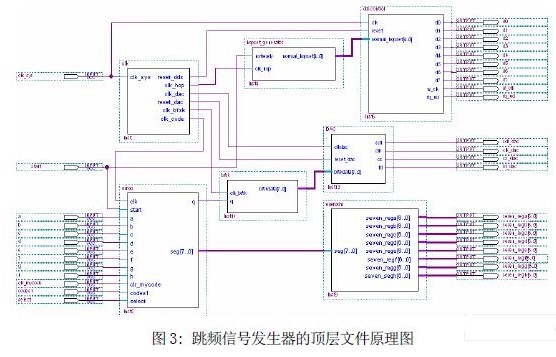

在本系統的軟件設計實現中,采用了VHDL 硬件描述語言進行設計,并在Altera 公司的QuartusⅡ7.0 軟件中完成基帶子系統程序編寫、語言編譯和調試及硬件下載工作。本系統的軟件結構框圖主要有時鐘分頻模塊、跳頻圖案產生模塊、信息碼輸入模塊、BFSK 調制模塊及DAC 和DDS 的接口控制模塊組成,具體框圖如圖3。

2.1 時鐘分頻模塊

完成一次DDS 轉換需要10 個時鐘信號,因此選擇系統時鐘clk_sys 頻率為50MHz,周期為0.02us。以系統時鐘為基準,14 個狀態為一個循環產生各種時鐘信號。每個狀態循環的第0 個狀態的1 個周期產生跳頻圖案產生模塊的時鐘信號,第0 和第1 個狀態的2 個周期產生AD9850 控制代碼的復位信號。當AD9850 控制代碼的復位信號變為低電平后,在系統時鐘的作用下,AD9850開始裝入控制信號。

2.2 跳頻圖案產生模塊

本系統的跳頻圖案發生器是由31 級m 序列構成,把該序列相鄰的5 個碼元對應的值模20 作為頻率控制碼,系統中不同的信道在同一時鐘控制下進行全同步跳頻,跳頻圖案為同一序列的不同偏移,這樣就保證了各信道的頻率各不相同,不會產生頻率交疊。系統的中頻頻段為44.625~90.125MHz,跳頻帶寬為45.5MHz,分了20 個頻率點,跳頻最小間隔為2.275MHz。采用以上介紹的DDS+PLL 的頻率合成法,根據電路可推算出輸出頻率Fout與頻率控制字M 的關系為

(一般FDDS=125MHz),由此關系式產生相應的頻率。

2.3 信息碼輸入模塊

信息碼輸入模塊包括外部輸入模塊、序列信號產生模塊、2 通道數據選擇模塊。外部輸入模塊是將輸入的8 位用戶自定義的信息碼在按鍵開關信號codes1 和clr 的控制下循環移位輸出,輸出信號為q。當循環移位鍵按下即codesl=‘0’時,從撥碼開關并行讀入8 位信息碼;當codesl=‘1’時,8 位信息碼循環移位,最后一位碼作為待發送的碼元。當清除鍵按下即clr=‘0’時,8 位信息碼全部置‘0’。序列信號產生模塊在分頻器輸出的時鐘信號的作用下能夠循環產生一組或多組序列信號,在開始初始化按鍵按下即clr=‘0’時,初始化為“10110101”。通道數據選擇模塊通過按鍵信息方式選擇開關來選擇采用用戶自定義的信息或由序列信號產生模塊生成的信息進行處理。

2.4 BFSK 調制模塊

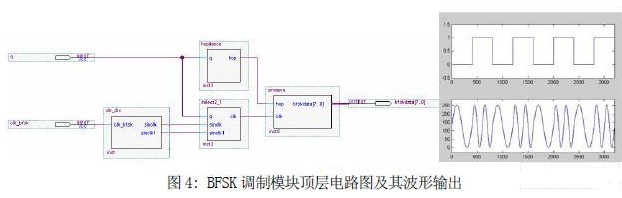

該模塊的功能是在系統時鐘控制模塊輸入的時鐘clk_bfsk 的控制下,由通過數據選擇模塊輸入的序列q 的信息比特決定發送分頻器輸出的2 個頻率中的哪一個來進行BFSK 調制,輸出為BFSK 波形的各點采樣幅值,幅值的精度為8 位二進制,該8 位信號經過D/A 轉換后,即得到實際的BFSK 信號。如圖4 所示,該調制模塊共分為分頻器、跳變檢測、2:1 數據選擇器、正弦波信號產生器等5 部分。

正弦波信號產生器中每個采樣點采用8 位量化編碼,即8 位分辨率。用包含100 個狀態的狀態機來實現,同時設計一個異步復位端,保證當每個‘1’或‘0’到來時其調制信號正好位于坐標原點sin0 處。狀態機共有8 位輸出,經DAC 變換為模擬信號輸出。

由于仿真結果并非直觀的波形,所以將BFSK 模塊在Quartus 中的波形仿真結果bfsk.vwf 另存為列表文件bfsk.tbl。把該文件放置在Matlab 程序的當前工作文件夾內,使用編寫的Matlab程序讀取該文件,并提取其中的數值作圖,可以得到圖7 所示直觀的BFSK 波形,這樣可以看到頻率隨著輸入信息的變化而變化,驗證設計的正確性。

2.5 DAC 和DDS 的接口控制模塊

利用狀態機模型實現DAC 和DDS 的控制時序。利用組合邏輯電路產生輸出信號容易出現毛刺現象,單一進程的狀態機的程序可讀性不好,因此我們采用時序邏輯電路產生輸出信號的格式進行控制程序的編寫。

3. 結束語

本文提出一種基于FPGA和DDS+PLL 技術的跳頻信號源的實現方案。在FPGA中利用VHDL語言來實現基帶子系統,通過修改程序中的相關內容便可產生多種形式的跳頻信號,具有很大的靈活性,并且電路易于實現同步。實驗證明,通過FPGA和DDS+PLL相結合,該跳頻信號源設計原理正確,輸出的跳頻信號穩定、頻率分辨率高、頻率切換速度快、輸出頻率高,可在45.5MHz范圍內實現全頻段跳頻。

-

FPGA

+關注

關注

1646文章

22059瀏覽量

619164 -

DDS

+關注

關注

22文章

672瀏覽量

154522 -

信號產生器

+關注

關注

0文章

15瀏覽量

10464

發布評論請先 登錄

怎么設計基于FPGA和虛擬儀器的DDS信號發生器?

基于FPGA 的新的DDS+PLL時鐘發生器

基于FPGA短波差分跳頻信號發生器的設計

DDS多波信號發生器的實現

基于FPGA的DDS信號發生器設計方案解析

評論