定標器在大學實驗中有很廣泛的應用,其中近代物理實驗中的核物理實驗里就有2個實驗(G-M計數管和β吸收)要用到高壓電源和定標器,

而目前現有的設備一般使用的是分立元器件,已嚴重老化,高壓極不穩定,維護也較為困難;另一方面在許多常用功能上明顯欠缺,使得學生的實驗課難以維持。為此我們提出了一種新的設計方案:采用EDA進行結構設計,充分發揮FPGA(Field Programmable Gate Array)技術的集成特性,拋棄原電路中眾多晶體管,成功地對系統中的大量處理電路進行了簡化和集約,提高了儀器的可靠性和穩定性,有利于電路的測試和檢修。改進方案后的定標器不僅完善了原有的功能,還增加了數據存儲、RS232接口等功能,可以方便地與PC機接口通信,進行數據處理、圖像顯示和打印等。

1 G-M計數器原理

G-M計數管是一種低壓氣體放電管,

作用是將入射粒子(射線)轉換成電壓脈沖輸出。原子核心物理實驗中常用它作為計數裝置的“探頭”探測射線及射線強度。G-M計數管有2種:用于探測β射線的鐘罩型和主要用于探測γ射線的長圓柱型。其中鐘罩型β計數管的工作電壓為千V(伏)左右,圓柱型工作電壓接近千V(伏)。

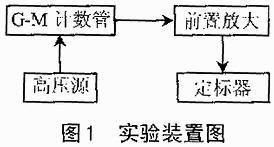

射線粒子在計數管中引起氣體“雪崩”放電,使得計數管導通;電流通過負載電阻R形成一個負脈沖,此脈沖信號通過電容C,經前置放大器送至定標器計數,如圖1所示。由于計數管在放電終止后會形成連續放電現象,此現對計數管極其有害,故一發現計數突然增加時,就應立即降低高壓。改進后的定標器會自動控制高壓源,將其電壓降低。這些改進。即可避免以前實驗中出現的計數管損壞問題。

2 定標系統原理及硬件實現

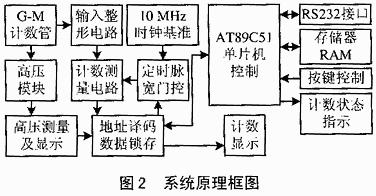

定標器系統由電源部分、輸入電路部分和脈沖計數顯示部分3個模塊組成,原理框圖如圖2所示。

G-M計數管產生的負脈沖經過輸入整形電路,進行整形、放大處理,產生標準TTL信號,再由計數測量電路進行計數。定時脈寬門控電路控制計數的脈寬,分6個檔:×10 -3、×10 -2、×10 -1、×10 0、×10 1、×10 2。時間倍乘檔有4種選擇:×1、×2、×4、×8。這樣進行的一組測量數據即可以用來描述射線粒子產生的規律。

圖2中,顯示部分采用的是動態顯示的方法,

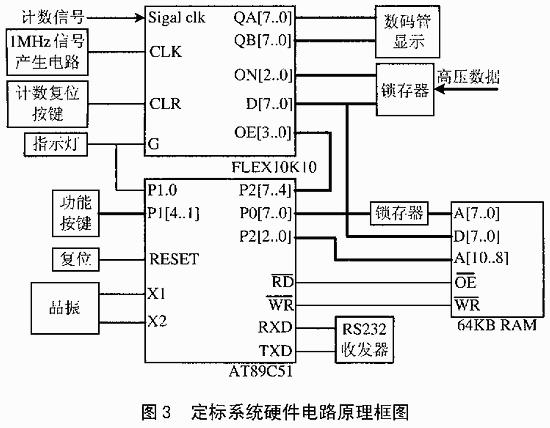

利用單片機AT89C51來進行即時的控制和相應的顯示數據。同時根據需要,選擇部分測量數據(包括此次計數數據及對應的高壓值)存儲到RAM中,然后將所選取的RAM中的數據通過RS232串行端口發送到PC機上,經過相應的處理軟件進行描圖,以及相應的實驗數據處理。為了使系統更加集成化,特定時脈寬門控、計數測量電路、地址譯碼及數據鎖存、總線的驅動等電路集成到1片FLEX10K的FPGA中。圖3為系統詳細電路原理框圖。

3 FPGA芯片設計

3.1 FPGA邏輯功能結構及其總體設計

為了簡化設計,實現系統大量邏輯電路的集成,在設計中使用了現場可編程邏輯門陣列器件(FPGA)。FPGA主要實現以下邏輯功能:定時脈寬門控、計數測量、地址鎖存、譯碼、總線的驅動和擴展以及數碼顯示的控制等功能。其邏輯功能頂層結構如圖4所示。FPGA器件選擇Altera公司FLEX10K10系列的EPF10K10LC84-4芯片。該芯片集成有1萬個等效邏輯門,含有572個邏輯單元(LEs)、72個邏輯陣列塊(LABs)、3個嵌入式陣列塊(EAB s),并具有720個片內寄存器,可以在不占用內部資源的條件下實現6144 bit的片內存儲器;內部模塊間采用高速、延時可預測的快速通道連接;邏輯單元間具有高速、高扇出的級聯鏈和快速進位鏈;片內還有三態網絡和6個全局時鐘、4個全局清零信號以及豐富的I/O資源;每個I/O引腳可以選擇為三態控制或集電極開路輸出,可以通過編程控制每個I/O引腳的速度以及I/O寄存器的使用。

FPGA使用的開發軟件為MAX+PLUS II。該軟件是一個集設計輸入、編譯、仿真和編程為一體的超級集成環境;提供了自動邏輯綜合工具,可以在多個邏輯層次上對高級設計描述進行綜合、優化,大大縮短了編譯時間,加速了FPGA設計開發進程。MAX+PLUS II支持各種HDL輸入選項,包括VHDL、Verilog HDL和ALTERA的硬件描述語言AHDL;提供豐富的庫單元供設計者調用,其中包括74個系列的全部器件和多種特殊的邏輯宏單元(macrofunction),以及新型的參數化的巨單元(magafunction)。FPGA設計經過4個基本階段:設計輸入、設計編譯、設計驗證和器件編程。首先,根據系統的邏輯功能生成頂層結構圖,如圖4所示。然后,分成幾個小模塊進行下一級設計。由此由上而下分析其邏輯功能,從底層進行設計編譯,每一級都進行波形驗證。當最后頂層模塊的邏輯功能在波形仿真中滿足系統時序要求時,才可進行器件編程。

由于FLEX10K在工作期間,將配置數據保存在SRAM中,而SRAM數據是易丟失的。SRAM單元必須在器件加電后裝入配置數據,且配置完成后,它的存儲器和I/O引腳必須被初化。初始化后,器件進入用戶模式,開始系統運行。對于FLEX10K系列器件,Altera公司提供了4種配置方案:EPC1(或EPC1441)EPPOM方式配置法、被動串行法、被動并行同步法、被動并行異步法。對器件進行配置時,我們先用被動串行法(passive serial)。這種方式是通過下載電纜對器件進行配置的,適合于調試階段。當整個系統設計完成后,利用EPPOM方式對器件進行配置。這樣固化在EPROM中的數據將在系統上電時對FPGA芯片配置,其中EPROM芯片選用EPC1441。

3.2 FPGA單元模塊設計

FPGA單元主由脈沖計數模塊,定時控制模塊,地址鎖存、譯碼、總線驅動、擴展模塊這3大模塊組成。其中脈沖計數模塊和定時控制模塊用來實現對輸入脈沖的計數次數的測量;地址鎖存、譯碼、總線驅動和擴展這部分模塊,主要實現各數據在總線上的分時傳輸。總線上的數據包括脈沖計數數據和電源模塊的高壓數據,以及來自單片機的數據總線D0~D7的數碼顯示用數據。此模塊中的地址譯碼部分,提供鎖存單元片選信號。圖5所示為FPGA頂層電路圖。

在具體設計時,考慮到計數脈沖寬度為0.1~100μs,最高計數率為2MHz,即計數位數達7位,所以設計中的脈沖良數模塊就相當于1個7位的BCD加計數器;而定時控制模塊相當于1個7位的BCD減計數器。減計數器的預置初始值由定時選擇開關控制,從而控制數的時間。CLR信號為“計數鍵”產生的一脈沖信號,標志計數開始,而減計數器減到0時加計數器即停止計數。這部分設計通過調用MAX+PLUS II提供的庫函數用AHDL語言結合圖形輸入完成。地址譯碼、鎖存、總線驅動模塊主要由D觸發器和I/O接口設計而成。由于數據傳輸中用的是雙向輸入/輸出端口,但是Altera芯片的引腳端口并不可以直接使用,需要加1個三態的邏輯門,因此,總線接口部分采用這2種函數原形(三態門和雙向端口)進行組合設計。

3.3 FPGA功能模塊仿真時序

在整個FPGA設計中,各單元模塊都是經過嚴格的設計驗證之后才繼續上一層設計的。這里主要使用MAX PLUS II的TIMER進行波形仿真,來驗證各子模塊的功能,判斷其時序是否滿足要求。若時序稍有不對,甚至僅是小毛刺,也要立即更改輸入設計。這樣,設計的精度才高,系統工作才穩定。當每個模塊最終都在時序上滿足邏輯功能需求時,設計才能完成。圖6為FPGA在MAX PLUS II環境下綜合設計后的時序仿真波形圖。

4 單片機軟件設計

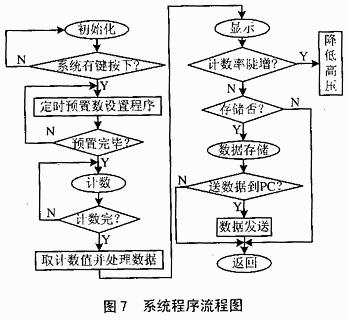

軟件部分主要是單片機AT89C51對系統進行控制及相應的數據處理,整個控制流程如圖7所示。

結束語

本文給出了一種用于核物理實驗中的G-M計數裝置定標器的新設計方案。此方案在傳統的實驗原理下,對舊儀器在電路和功能上做了較大程度的改進。在設計中采用EDA設計思想,以AT89C51單片機作為數據傳輸的控制核心,用Altera現場可編程邏輯器件(FLEX10K系列的FPGA)對核心計數部分電路進行效而靈活的集成,并在此基礎上,擴展了數據的存儲功能,增加了與PC機通信的RS232串行接口,從而更加智能化。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603050 -

芯片

+關注

關注

455文章

50732瀏覽量

423275 -

單片機

+關注

關注

6035文章

44553瀏覽量

634766 -

eda

+關注

關注

71文章

2755瀏覽量

173219

發布評論請先 登錄

相關推薦

利用FPGA與EDA技術實現核物理實驗常用儀器定標器的設計

利用FPGA與EDA技術實現核物理實驗常用儀器定標器的設計

評論