1.引言

Kicker電源是“九五”國家重大科學工程之一蘭州重離子加速器冷卻儲存環(HIRFL-CSR)的注入引出系統中一個重要組成部分 ,電源系統共包括六個分電源,它們需從共同的信號源接收信號,由于要求它們接收到的信號為同步信號而又因為地理位置致使其接收的信號是不可能完全同步的,為使其接收到同步信號需要在各分電源前端各配置一高速脈沖數字延遲線,對輸入信號進行調節使經過數字延遲線后所有信號達到同步的效果。數字延遲線要求其延遲時間可調,時間范圍為:5ns~300ns。延遲線是用于將電信號延遲一段時間的元件或器件,其廣泛使用在雷達、電子計算機、彩色電視系統、通信系統,以及測量儀器中。

隨著EDA技術的廣泛應用,CPLD已成為現代數字系統設計的主要手段, CPLD的時鐘延遲可達到ns級,結合其并行工作方式,在超高速、實時測控方面有非常廣闊的應用前景;并且CPLD具有高集成度、高可靠性,幾乎可將整個設計系統下載于同一芯片中,實現所謂片上系統,從而大大縮小其體積。CPLD目前正朝著更高速、更高集成度、更強功能和更靈活的方向發展[2]。采用CPLD來實現數字延遲線系統,不但大大節省電路開發費用,而且能提高設計效率,同時還能有效實現電路的數字化與微型化。

2.數字延遲線工作原理

數字延遲線是將邏輯信號延遲一段時間的元件或器件。通常數字延遲線的設計思路是通過兩個參數完全相同的延遲模塊分別對脈沖的上升沿和下降沿進行延遲來達到脈沖信號整體延遲一段時間的效果。而由于實際上不可能存在參數完全相同的延遲模塊使得脈沖前后沿的延遲時間不可能完全相同,所以這種設計的數字延遲線的延遲精度不可能很高。如果僅用一個延遲模塊就能同時完成脈沖前后沿的延遲,這樣就即節省了電路制作成本又提高了延遲線的延遲精度。本文正是基于這一思想并使用CPLD芯片來實現數字延遲線的設計的。

本數字延遲線整體思想是:延遲模塊在觸發信號上升沿到來時開始工作,邏輯控制電路控制其輸出為輸入脈沖同相信號或輸入脈沖反相信號,邏輯控制電路輸出用于觸發延遲模塊,在延遲線輸入脈沖上升沿到來時,邏輯控制電路輸出為與輸入脈沖同相信號,進而觸發延遲模塊,在延遲線輸入脈沖下降沿到來時,邏輯控制電路輸出為與輸入脈沖反相信號,該信號剛好為上升沿,進而觸發延遲模塊進行延遲。同時該數字延遲線設計采用了反饋網絡結構,結構更緊湊,更穩定。

延遲線輸入信號A,其反相信號 ,兩信號通過邏輯控制模塊其輸出信號O1與其中一路信號同相,該信號接入可逆計數器模塊置位端,當O1信號上升沿到來時觸發可逆計數器開始計數,計數器計數結束后輸出信號CK觸發T觸發器使T觸發器輸出態Q和 反相,輸出端Q為該數字延遲線的輸出端,其相對輸入信號A有可逆計數器計數時間T的相對延遲,同時T觸發器的輸出端Q和 又作為邏輯控制模塊的選擇控制信號對信號A和 進行選擇。初試狀態下延遲線輸入信號為低電平,T觸發器輸出端即延遲線輸出端Q也為低電平,此時邏輯控制模塊選擇輸入信號A使其輸出信號O1和信號A同相,信號O1輸入至計數器置位端,計數器置位端低電平有效,所以O1使可逆計數器處于置位狀態,使計數器輸出端狀態恒處于預置位狀態,計數器輸出信號不發生改變,即而T觸發器輸出Q不發生改變,當信號A上升沿到來時,信號O1上升沿同時到來使其變為高電平,高電平觸發計數器開始減計數,當計數器計數至0時,計數器輸出端經或非門輸出的信號CK由低電平變為高電平,該上升沿觸發T觸發器使其輸出端Q反相,由低電平變為高電平,同時T觸發器的輸出端Q和 作為邏輯控制模塊的選擇控制信號使其輸出信號O1變為與 同相,而此時 為低電平,所以O1信號使計數器處于置數狀態輸出為預置數,使得CK有變為低電平,T觸發器不翻轉,所有信號維持此狀態不變。當輸入信號A出現下降沿,既由高電平變為低電平時,信號 出現上升沿使得O1有低電平變為高電平,O1觸發計數器減計數,減計數至0時,使得CK信號由低電平變為高電平,該上升沿觸發T觸發器使器輸出反相,一方面使得邏輯控制模塊輸出信號變為與A信號同相,處于低電平使計數器處于預置數狀態,使得電路狀態又恢復到初始狀態,當輸入信號A又有脈沖到來時,數字延遲線將會重復以上動作;另一方面使得輸出端Q出現下降沿,又高電平變為低電平,與輸入信號A同相。整個過程來看T觸發器輸出Q相對輸入信號A剛好有一個計數器計數時間Δt的延遲。數字延遲線電路工作原理的時序圖如圖1所示。由圖1還可看出,同時T觸發器的輸出端 也是數字延遲線輸入信號 的延遲信號。所以該數字延遲線即可以延遲高電平脈沖,也可以延遲低電平脈沖。

該數字延遲線電路特點總結如下:1、電路結構相對簡單,造價低廉。而一般延遲線電路都需要兩個完全相同的電路分別完成對輸入信號的上升沿和下降沿的等時間延遲以實現數字延遲線的功能[3],而且也不可能做到兩電路參數完全相同。2、邏輯功能強,該延遲線可同時完成高、低脈沖電平的延遲。3、電路為時鐘脈沖定時的延遲線,特別適用于數字通信、數字儀表及使用計算機的設備中。電路延時精度僅取決于時鐘脈沖CP的周期,受環境溫度、電源波動等因素的影響甚微,所以延遲時間非常穩定、精確,最大誤差只是1個字的計數誤差,時鐘頻率越大,延遲精度越高。4、電路可編程端即計數器預置數端DCBA可以由程序控制,DCBA端輸入不同的BCD碼得到不同的延遲時間的延遲線。延遲時間Δt=n×1/f,其中,f為時鐘脈沖CP的頻率,n為DCBA輸入端的BCD碼對應的十進制數。5、該數字延遲線的局限是它只能處理比其延遲時間長的脈沖信號,這也是現今數字延遲線的局限[4],但是該電路并不局限于只能處理占空比接近50%的脈沖信號,而是不受脈沖信號占空比的限制。

3.系統實現

高速可程控數字延遲線系統的整體結構圖如圖所示。Kicker電源需要接收三路信號:主閘流管脈沖信號(MS)、從閘流管脈沖信號(DS)和高壓脈沖信號(HV),故需要完成對這三路脈沖信號的可編程延遲。系統采用CPLD完成對三路信號的高速可程控延遲,CPLD外圍電路包括晶體振蕩器、系統復位電路及DCBA編程。延遲時間Δt由晶體振蕩器輸出時鐘頻率f和DCBA編程值共同確定,調節范圍為(1 ~ 24-1)/f。DCBA編程值設置值為0000 ~ 1111,當時鐘頻率f=200MHz時,延遲時間調節范圍為5ns ~ 75ns,時間調節精度為5ns。

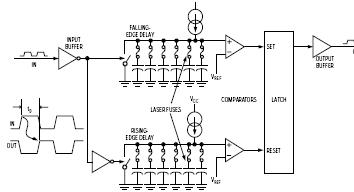

CPLD芯片包括三路數字延遲線模塊,單模塊的數字延遲線原理圖如圖3所示,包括MUX模塊、COUNTER_CDL模塊、MYCH模塊、MYTFF模塊和MYSEL模塊。數字延遲線模塊采用VHDL語言進行編程,程序碼較長,限于篇幅,不再給出其VHDL源程序碼[。

MUX模塊為邏輯控制模塊,輸出Q由控制端SEL電平高低選擇輸出與輸入D0同相或反相。COUNTER_CDL為可逆計數器模塊,根據DCBA編程設定值對信號進行延遲,MYCH模塊將總線信號轉換為單路信號,使輸出信號僅在總線信號值為“0000”時輸出信號為低電平。MYCH模塊輸出信號上升沿可觸發MYTFF模塊輸出反相,MYTFF模塊為T觸發器,其輸出即為數字延遲線信號,該信號同時作為MUX模塊的控制輸入端控制MUX模塊的輸出。當DCBA編程設定值為“0000”時,MYTFF輸出信號并不是數字延遲線輸入信號,即以上設計不能完成零延時,MYSEL模塊為信號選擇輸出模塊,在DCBA編程碼為“0000”時,輸出為延遲線輸入信號,否則,輸出為編程延遲信號。

4.仿真及波形

本系統采用的CPLD芯片為ALTERA公司的EPM3032ALC44-4芯片,其最高運行頻率為227.3MHz。采用MAX+PLUSⅡ10.0軟件工具開發。設計輸入完成后,進行整體的編譯和邏輯仿真,然后進行轉換、延時仿真生成配置文件,最后下載至CPLD器件,完成結構功能配置,實現其硬件功能。CPLD芯片EPM3032ALC44-4的各管腳布局如圖4所示。其中clk時鐘端口采用了芯片的全局時鐘端,管腳號為43,輸入信號為ms、ds和hv,輸出為mso、dso和hvo。各管腳序號見圖4所示。

數字延遲線模塊編譯后進行仿真,所得仿真波形圖如圖5所示。DCBA編程十進制值為4,延遲線輸出信號Sigout相對輸入信號Signal剛好由4個時鐘周期的延遲。Clk時鐘頻率設定為f=100MHz,即周期T=10ns,所以延遲時間Δt=4×10=40ns. 延遲線最大延遲誤差只是1個字的計數誤差,所以時鐘脈沖頻率越高,誤差越小,由于采用的CPLD芯片的最高運行頻率為227.3MHz,所以最小延遲誤差約為4.5ns。如果采用工作頻率更高的CPLD芯片,可進一步提高延遲誤差的精度。由定時分析,輸入信號到輸出信號傳播延遲為4.5ns,由時鐘信號clk到輸出信號的傳播延遲時間為9.1ns.

5.結論

摒棄了傳統的采用兩個參數完全相同的延遲模塊來實現數字延遲線的設計方法,設計了一種由單一模塊可同時對脈沖上升沿和下降沿進行延遲的數字延遲線,并采用了CPLD用以實現高速可程控數字延遲線系統的設計。另外,該數字延遲線系統可通過提高晶振頻率,采用速度更高的CPLD芯片來進一步降低延遲誤差。本文所述系統已完成調試工作并已開始應用于蘭州重離子加速器冷卻儲存環(HIRFL-CSR)的Kicker電源系統中。

-

電源

+關注

關注

184文章

17745瀏覽量

250574 -

eda

+關注

關注

71文章

2764瀏覽量

173362 -

計數器

+關注

關注

32文章

2256瀏覽量

94668

發布評論請先 登錄

相關推薦

數字延遲線工作原理及如何設計

數字延遲線工作原理及如何設計

評論