1 引言

CPLD是一種用戶可以根據自行需要而自己能夠設計構造其邏輯功能的數字集成電路系統,實現了硬件設計的軟件化。CPLD具有豐富的可編程I/O引腳,具有在系統可編程( In System programmability)、使用方便靈活的的特點;近年來, CPLD器件成本不斷下降,集成密度、速度和性能大幅度提高,一個芯片就可以實現一個復雜的數字電路系統;再加上使用方便的開發工具,使用CPLD器件可以極大地縮短產品開發周期,給設計、修改帶來很大方便。CPLD成為一種可優化硬件電路設計且具競爭力的產品。

ALTERA 公司不僅提供大規模的CPLD 和FPGA 器件, 同時也提供一套十分有特色的綜合工具MAXPLU S- II, 設計者既可以使用原理圖輸入, 也可以使用文本輸入方式, 更可以二者混合輸入。從編譯、綜合、布線到仿真、下載一氣呵成, 十分方便。

TMS320C6713是TI公司在TMS320C6711的基礎上推出的新一代浮點DSP芯片,它可以在255MHz的時鐘頻率下實現1800MIPS/1350MFLOPS的定點和浮點運算,極大程度上滿足了高速數據采集與實時控制系統對信號處理速度的要求。作為下位機使用時,它可通過主機口HPI與各種不同類型的上位機連接。

本文將給出如何使用ALTERA 公司的CPLD 器件EPM7128AE-144實現DSP的HPI口和背板的VME總線之間的連接方法。

2 TMS320C6713的HPI

2.1 TMS320C6713HPI口的接口信號

TMS320C6713的HPI口是一個16位寬的并行端口。上位機掌管該端口的主控權,可通過HPI直接訪問TMS320C6713的存儲空間和外圍設備。表1總結了TMS320C6713HPI的接口信號的基本特征。

下面對它們的具體工作方式進行說明。

(1)HD[15-0]可以看作數據地址的共用總線,通過HD[15-0]傳送的數據包括控制積存器的設置值、初始化的訪問地址以及要傳輸的數據。

(2)HCNTL[1-0]信號控制當前訪問的是HPI的哪一個寄存器,還提供了一個對HPI數據寄存器(HPID)進行自增的訪問方式。表2給出了HCNTL[1-0]控制信號功能。

(3)HHWIL的作用是表明區分HD[15-0]上傳輸的是32位數據中的高16位還是低16位。

(4)#HAS信號用于復用地址數據總線的主機。

(5)#HCS、#HDS1和#HDS2信號在片內組合為一個低有效的#HSTROBE信號,它的作用是:讀取時#HSTROBE信號的下降沿鎖存輸入HPI的控制信號,寫入時其下降沿和讀取時作用相同,上升沿則鎖存寫入的數據。

(6)#HRDY信號表明HPI是否已準備好傳輸數據,作用是在接口時序上插入等待狀態。

TMS320C6713HPI中用三個寄存器來完成主設備和CPU的通信,他們是HPI數據寄存器(HPID)、HPI地址寄存器(HPIA)、HPI控制寄存器(HPIC)。HPID中存放的是主機從TMS320C6713存儲空間中寫入的數據。HPIA中存放的是主機訪問TMS320C6713存儲空間的地址。HPIC中存放的是TMS320C6713的控制信息,其高16位和低16位內容相同。

3 設計實現

實際上, 整個CPLD 設計的主要任務也是圍繞這幾個信號的設計展開的。

用VHDL實現CPLD的內部邏輯實現,VHDL 是用來描述從抽象到具體硬件級別的工業標準語言, 并已成為一種通用的硬件設計交換媒介。。VHDL硬件描述語言設計方法其靈活性、可移植性都是非常好的,在對設計的仿真方面同圖形化硬件描述方法一樣都是非常優秀的,設計效率在大規模設計中將明顯高于原理圖設計。

部分VHDL程序如下:

has 《=‘1’;

hrw 《=crw;

hcntl0 《=ca2;

hcntl1 《=ca3;

hds1 《=‘1’;

hds2 《=cis and hrdy;

cirq1《=hint;

ca_l 《=ca16&ca15&ca14;

ca_m 《= ca5&ca4;

p1:process (ca_l,ca_m)

begin

case ca_m is

when “00”=》ec《=“1110”;

when “01”=》ec《=“1101”;

when “10”=》ec《=“1011”;

when “11”=》ec《=“0111”;

when others =》ec《=“1111”;

end case;

hcs 《=ec(0);

end process p1;

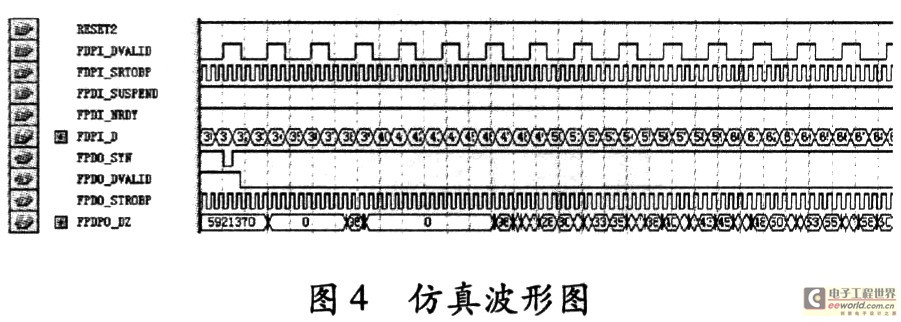

具體的設計思路如下:本設計中,因為還有其他板內部件需要選擇,所以采用地址的4和5譯碼來控制HCS,當為“00”時HCS有效。設計時將HDS1 固定接高電平, 并由IS和HRDY信號產生邏輯來控制HDS2 信號。當HRDY處于無效狀態(即HPI 端口未準備就緒) 時, HDS2 信號不變,不采樣任何信號;而當HRDY有效時, HDS2 信號同IS 信號保持一致, 并在IS 的下降沿采樣控制信號,在上升沿采樣數據信號。在一次傳輸開始之前和結束之后, HDS2 都要保持為高電平。可用HDS2 作為時鐘輸入的兩分頻電路來產生HHWIL ; HCNTL[ 0 : 1] 接兩根地址線,以便由上層驅動程序來控制對HPI 口內部不同寄存器的訪問, 并由CR/W來產生HR/ W信號。

4 結束語

VHDL程序仿真成功后后,通過PC并口下載到ALTERA公司的芯片EPM7128AE-144,先進的EDA工具可以減少設計周期和開發費用,通過功能和時序仿真,可以降低設計風險。同時,CPLD的在線可編程特性使得修改設計相當容易。本設計應用于蘭州重離子加速器冷卻儲存環的控制系統中。

-

dsp

+關注

關注

553文章

8011瀏覽量

349134 -

芯片

+關注

關注

456文章

50886瀏覽量

424185 -

集成電路

+關注

關注

5388文章

11561瀏覽量

362002

發布評論請先 登錄

相關推薦

基于FPGA的高速LVDS數據傳輸

用FPGA實現多DSP局部總線與VME總線接口設計

可以通過微網格設計實現高速數據傳輸嗎?

PCI總線高速數據傳輸系統設計

基于FPDP的高速數據傳輸系統設計

基于FPGA的VME總線和CAN總線之間的傳輸轉換方案設計

怎樣使用CPLD實現DSP芯片與背板VME總線之間的高速數據傳輸連接

怎樣使用CPLD實現DSP芯片與背板VME總線之間的高速數據傳輸連接

評論