引言

超聲檢測在各種工程上有著非常廣泛的應用,而且聲束聚焦對于超聲診斷也愈來愈重要,因為人們總是希望看到更小、更細微的組織結構,這不僅要求提高工作頻率、而且要求聲束聚焦。聲束的聚焦類似于光束通過透鏡的原理,最簡單的方法是將換能器直接作成凹面陣實現聚焦。但此時其焦點是固定的,而在超聲聚焦應用中都常需要調整焦點(改變焦距和聚焦的方向),如用機械方法調焦很不方便,速度也慢。超聲相控陣的方法是用電子技術調整焦點位置和聚焦的方向,它的基本思想是控制超聲探頭中不同單元之間的觸發延時時序,在精確的延時時序控制下,不同單元發出的超聲波在空間發生干涉,產生所需要的合成波束(見圖1)。相控超聲波的這種特性非常適合于無損檢測。首先可以通過電子切換選用不同的單元,實現波束的快速移動(即電子掃查),明顯提高缺陷的檢測效率,比單個單元的常規探頭檢測速度快一個數量級。其次相控超聲波束很容易實現波束偏轉,不用移動探頭就可以實現動態“扇掃”。當然這也要歸功于現代集成電路技術發展,因為發射與接收的延時控制在納秒級,而且信號的采樣與處理需要很高的吞吐量,針對上述特點,采用FPGA技術研制一套數字式多通道信號發射與接收設備已成為可能。

FPGA在系統中的應用

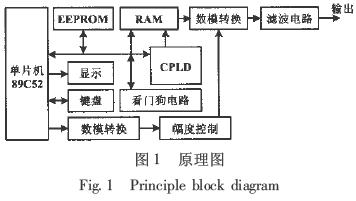

由于該系統涉及到許多控制信號的時序配合和大容量數據的緩沖問題,采用FPGA可以很好的滿足系統要求。比如Altera的Cyclone系列的EP1C3具有的單元數、RAM以及I/O管腳等非常適合本文描述的系統。圍繞FPGA的系統設計示意圖見圖2。該相控陣系統采用2個64單元的探頭,通過四選一開關切換電路實現波束的快速移動。由于發射與接收的延時控制在納秒級,即使FPGA的時鐘為100MHz,延時控制精度也只能做到10ns。如果通過提高FPGA的時鐘頻率來實現更高的延時控制精度,將給電路設計帶來困難,并且成本也加大,故采用精度為2ns的延時線實現10ns以內的延時要求,此時FPGA只需要3根I/O線用來控制選通延時線就可以實現10ns以內的延時要求。

利用FPGA內部的大容量RAM對接收的超聲信號進行緩存與合成延時控制。這種延時控制可以通過圖3進行解釋。在FPGA中為每一路參與合成的超聲波束開辟一個相同容量的buffer(比如2kbytes)。當信號到達時,buffer的寫允許,采集一定數據量后,如果還有波束未到達就延時等待,直到參與合成的所有波束到達并采集后,所有buffer的讀同時允許,通過D/A和模擬加法電路就可以實現超聲波束的合成了。當然,利用FPGA的buffer實現的延時精度只有10ns,所以D/A后面仍然需要延時線配合。表1.列出了上位機需要寫給FPGA的控制參數,這些參數通過ISA總線,以word(16bits)的形式寫入,其中包括發射延時、發射選通允許、發射四選一開關、發射脈寬、Buffer的大小、接收選通允許、A/D轉換開始時間、接收四選一開關以及接收延時等待。

發射延時控制:10ns級延時,13bits

2ns級延時,3bits

選通

發開關

空,保留

發射脈寬(10ns級),8bits

超聲波Buffer的大小,16bits

選通

A/D轉換開始時間(也就是Buffer寫允許相對于同步脈沖延時),10ns級,15bits

收開關

接收延時等待,10ns級,11bits

2ns級延時,3bits

精確延時控制驗證方法

利用FPGA與延時線的方法實現精度為2ns的延時控制,對于發射來說,調試與驗證比較容易,只需要一個多通道500MHz的示波器就可以了。從FPGA發射一個方波同步脈沖和一個方波激勵脈沖,一級一級的往后測試,直至相控陣探頭。通過示波器可以觀察從FPGA到探頭整個電路的系統延時以及激勵脈沖相對于同步脈沖的延時間隔,該間隔由FPGA內部參數決定,并且可以修改。

對于接收延時控制是否準確的驗證稍微困難一些。因為接收的不是方波脈沖,而是7.5MHz(探頭單元固有頻率)的近似正弦超聲信號。為了驗證延時控制是否正確,需要在超聲波接收電路之前加上一個不連續的,只有若干周期的7.5MHz的正弦信號,一般的信號發生器沒有這種功能。利用系統上的FPGA配合100MHz D/A比較容易產生這種特殊信號。采用VerilogHDL設計的FPGA程序如下:

reg [3:0] da_cnt; //正弦表指針

reg [15:0] da_encnt; //D/A允許計數器

reg daen; // D/A允許

assign AD_DATA_OUT = AD_test; //D/A數據總線

always @ (posedge CLK) //D/A允許控制da_encnt

begin

if(SYN_PULSE)da_encnt 《= 16‘b0;

else da_encnt 《= da_encnt + 1;

end

always @ (posedge CLK) //daen

begin

if(da_encnt 》 65) daen 《= 1’b0; //一共輸出5個周期

else daen 《= 1‘b1;

end

always @ (posedge CLK) //正弦表指針da_cnt修改

begin

if( (SYN_PULSE)||(da_cnt 》= 12) ) da_cnt 《= 4’b0;

else

begin

if(daen) da_cnt 《= da_cnt + 1;

else da_cnt 《= 4‘b0;

end

end

always @ (posedge CLK) //通過D/A輸出正弦表

begin

case(da_cnt[3:0])

4’b0000: AD_test 《= 128; //0

4‘b0001: AD_test 《= 187;

4’b0010: AD_test 《= 233;

4‘b0011: AD_test 《= 255;

4’b0100: AD_test 《= 248;

4‘b0101: AD_test 《= 213;

4’b0110: AD_test 《= 159;

4‘b0111: AD_test 《= 97;

4’b1000: AD_test 《= 43;

4‘b1001: AD_test 《= 8;

4’b1010: AD_test 《= 1;

4‘b1011: AD_test 《= 23;

4’b1100: AD_test 《= 69; //12

default: AD_test 《= 128; //13

endcase

end

通過上述方法可以產生出比較好的接近7.5MHz的若干周期的正弦波形,將該波形加到其它電路板超聲波接收電路之前,可以驗證接收延時控制是否準確。實驗證明,FPGA加上延時線完全可以實現精度為2ns的超聲波發射與接收延時控制的要求。

責任編輯:gt

-

FPGA

+關注

關注

1629文章

21754瀏覽量

604203 -

RAM

+關注

關注

8文章

1369瀏覽量

114764 -

脈沖

+關注

關注

20文章

892瀏覽量

95668

發布評論請先 登錄

相關推薦

多通道數字式儀表

多通道ARINC429總線數據接收和發送的實現

求一種基于FPGA的A型數字式超聲系統的構成方式

基于MCU和FPGA的數字式相位測量儀的設計

數字式聲發射檢測儀的設計

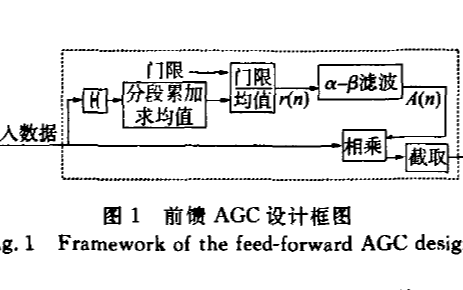

如何使用FPGA實現全數字式前饋AGC的設計

基于FPGA技術實現數字式多通道信號發射與接收系統的設計

基于FPGA技術實現數字式多通道信號發射與接收系統的設計

評論