設(shè)計(jì)結(jié)束了專用電路板試驗(yàn)臺(tái)測(cè)試結(jié)果表明功能完全正常設(shè)計(jì)小組的工作人員不約而同地長(zhǎng)舒了一口氣每個(gè)人都認(rèn)為最艱苦的階段已經(jīng)過去了專用系統(tǒng)板的最終集成開始進(jìn)行性能可靠的線性試驗(yàn)臺(tái)電源很快將被高效的開關(guān)電源所取代試驗(yàn)室基準(zhǔn)時(shí)鐘現(xiàn)已被低成本解決方案取而代之在最初的專用電路板測(cè)試結(jié)果顯示有望獲得極佳性能的同時(shí)無法預(yù)知的邏輯器件失效正在系統(tǒng)中悄然滋生在無計(jì)可施的情況下只好在背板上插拔電路板人們發(fā)現(xiàn)只有某些插槽組合能夠正常工作這純粹是一個(gè)邏輯問題嗎系統(tǒng)電源上的負(fù)載是否包含在計(jì)算公式中電路板彼此靠近有沒有產(chǎn)生問題時(shí)鐘抖動(dòng)是否關(guān)閉了定時(shí)容限窗口如何才能對(duì)問題實(shí)施隔離以便開始試驗(yàn)的正確設(shè)計(jì)這些問題均難以回答但是在系統(tǒng)設(shè)計(jì)的整個(gè)過程中我們當(dāng)中的大多數(shù)人都將會(huì)至少一次向這些問題妥協(xié)擺脫這種無奈困境的方法是求助于工程SWAT小組這是由一些具有多年豐富維修經(jīng)驗(yàn)的優(yōu)秀工程師所組成的團(tuán)隊(duì)來解決問題SWAT小組帶著一連串的問題深入到試驗(yàn)室中進(jìn)行調(diào)查至關(guān)重要的每個(gè)人都必需嘗試回答一個(gè)根本題試驗(yàn)臺(tái)與系統(tǒng)設(shè)置之間的區(qū)別是什么

當(dāng)處理復(fù)雜問題時(shí)時(shí)常回過頭去對(duì)子系統(tǒng)之間的依存性重新進(jìn)行分析和思考往往能夠得出令人驚訝的結(jié)果這樣做的道理在于在某種場(chǎng)合起作用的東西未必會(huì)在其他場(chǎng)合自動(dòng)生效當(dāng)遇到系統(tǒng)依存性問題時(shí)系統(tǒng)時(shí)鐘通常成為人們的重點(diǎn)懷疑對(duì)象將系統(tǒng)故障歸咎于時(shí)鐘固然不難但根本原因何在時(shí)鐘究竟是引發(fā)故障的罪魁禍?zhǔn)走€是周圍環(huán)境的替罪羊雖然本文并不能夠針對(duì)系統(tǒng)細(xì)節(jié)專門作答但的確對(duì)存在有噪基準(zhǔn)時(shí)鐘脈沖源時(shí)的抖動(dòng)衰減方法進(jìn)行了研究這并不是尋求最小衰減的另一種嘗試而是要弄清楚顯著衰減會(huì)產(chǎn)生什么樣的后果此項(xiàng)工作在很大程度上來說就是眾所周知的FailSafeTM時(shí)鐘架構(gòu)的一個(gè)特殊研究分支在時(shí)鐘冗余系統(tǒng)中FailSafeTM的作用是在基準(zhǔn)時(shí)鐘脈沖源消失的情況下簡(jiǎn)化開關(guān)操作并維持時(shí)鐘的存在試驗(yàn)室分析表明FailSafe架構(gòu)能夠在原有應(yīng)用范圍的基礎(chǔ)上自然地?cái)U(kuò)展到用于對(duì)付嚴(yán)重的時(shí)鐘修整問題保持同步自然是必需的而FailSafe也能夠做到這一點(diǎn)

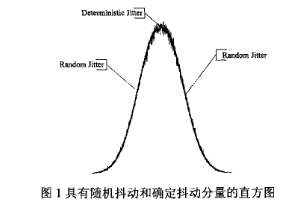

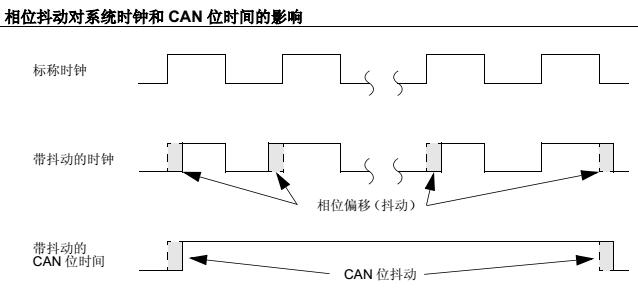

抖動(dòng)有多重含義而對(duì)時(shí)鐘抖動(dòng)的要求與系統(tǒng)規(guī)范具有很大的相關(guān)性為完成這項(xiàng)工作需要關(guān)注三個(gè)主要的測(cè)量條件包括周期至周期抖動(dòng)有時(shí)稱為周期抖動(dòng)以及1s和10s時(shí)間間隔內(nèi)的累積抖動(dòng)抖動(dòng)信息的統(tǒng)計(jì)累積隨后以隨機(jī)抖動(dòng)RJ和確定抖動(dòng)DJ給出通常用直方圖來表示

隨機(jī)抖動(dòng)和確定抖動(dòng)一種不受歡迎的組合

雖然系統(tǒng)中的自然高斯噪聲發(fā)生元件始終會(huì)引發(fā)抖動(dòng)但如果存在DJ則清楚地表明一個(gè)調(diào)制信號(hào)源正在向定時(shí)系統(tǒng)注入能量從直方圖的角度來看DJ充斥于中間部分從而擴(kuò)展了直方圖左側(cè)和右側(cè)的自然高斯響應(yīng)圖1示出了該原理由于數(shù)字系統(tǒng)是有限系統(tǒng)就是說不應(yīng)存在調(diào)幅信息而是在恰好正確的時(shí)刻獲得一個(gè)0或1因此邊緣布局信息的收集和分析過程正是抖動(dòng)分析的切入點(diǎn)因?yàn)橹狈綀D是邊緣的統(tǒng)計(jì)集合所以良好的測(cè)量需要大量的采樣信息組合來獲得必要的+/-6統(tǒng)計(jì)數(shù)據(jù)抽取這樣做是有道理的由此可實(shí)現(xiàn)最高的測(cè)量精度

噪聲條件下的時(shí)鐘信號(hào)修整

系統(tǒng)中的噪聲能量的影響似乎總會(huì)不可思議地侵入時(shí)鐘脈沖源時(shí)鐘脈沖源遭受傳導(dǎo)噪聲或輻射噪聲影響的可能性大致相同雖然大多數(shù)工程師在工作實(shí)踐中均采用容性旁路技術(shù)來對(duì)付傳導(dǎo)噪聲但輻射噪聲卻往往更加難以定位和矯正串?dāng)_即屬此類這是因?yàn)?a target="_blank">電氣孔隙通常足以成為代人受過的時(shí)鐘脈沖源至吸收輻射能量的軌跡其他一些常常被忽略的因素是由磁感應(yīng)所耦合的能量捕獲到一個(gè)與電源開關(guān)速率奇跡般地保持同步的時(shí)鐘調(diào)制頻率的情況并不鮮見

減少時(shí)鐘走線孔隙有利于吸收輻射能量由于互易定律有效因此能夠容易地吸收輻射能量的時(shí)鐘線同樣也會(huì)容易地輻射能量這將在進(jìn)行EMI輻射測(cè)試時(shí)產(chǎn)生不良影響隨著近期ZDB即零延遲緩沖器的普及定時(shí)分配正在變得更加局部化了這是一件好事除了時(shí)鐘緩沖機(jī)制外ZDB還能夠利用PLL技術(shù)來提供零延遲甚至負(fù)延遲以克服時(shí)鐘傳播雖然能夠進(jìn)行一些抖動(dòng)衰減但總的說來ZDB器件并不提供使一個(gè)器件能夠完成很大的抖動(dòng)衰減所需的編程參數(shù)

利用模擬技術(shù)來進(jìn)行信號(hào)修整

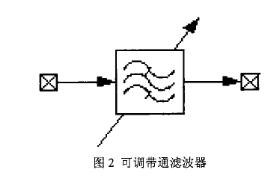

由于抖動(dòng)對(duì)載頻或以最佳單位間隔UI運(yùn)行的純時(shí)鐘基頻進(jìn)行調(diào)制因此從理論上說布設(shè)一個(gè)頻帶極窄的帶通濾波器應(yīng)該有助于衰減調(diào)制分量由于尖銳響應(yīng)具有高Q值所以必須小心地將帶通濾波器置于載波的中心以確保基頻不被衰減否則載頻隨著時(shí)間的長(zhǎng)期推移而發(fā)生的自然漂移將導(dǎo)致顯著衰減理想的情況是濾波器應(yīng)跟蹤載波的變化在我們所舉的簡(jiǎn)單示例中需要進(jìn)行時(shí)鐘信號(hào)的再整形以重新生成一個(gè)方波信號(hào)原因是帶通濾波器有可能除去諧波分量雖然以這種方式來減輕抖動(dòng)是合理的但是要想以較低的成本和較小的占用空間來實(shí)現(xiàn)具有所需Q值的有效解決方案則很困難

采用PLL來減輕抖動(dòng)的技術(shù)

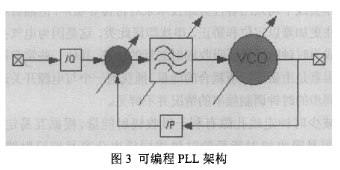

由于PLL在時(shí)鐘發(fā)生和分配中所起的作用持續(xù)增長(zhǎng)因此將PLL轉(zhuǎn)移函數(shù)用作減輕抖動(dòng)的方法是值得考慮的這種采用PLL來減輕抖動(dòng)的處理過程要求對(duì)其實(shí)現(xiàn)方法假定有一個(gè)可提供滿足設(shè)計(jì)目標(biāo)的足夠編程選項(xiàng)的器件有一個(gè)全面深入的了解

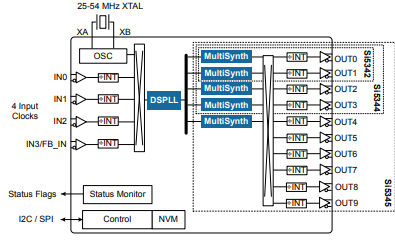

PLL具有可為上述采用帶通濾波器來減輕抖動(dòng)的方法提供跟蹤功能的優(yōu)點(diǎn)環(huán)路內(nèi)部的增益和環(huán)路帶寬組合通過改變響應(yīng)來改變轉(zhuǎn)移函數(shù)在處理高集成度的低成本PLL解決方案時(shí)通常會(huì)犧牲編程方面的靈活性包括更改常常是集成化的環(huán)路濾波器圖3描繪了一種理想的PLL編程方案在該方案中電荷泵環(huán)路濾波器和VCO增益均可在一個(gè)擴(kuò)展范圍內(nèi)進(jìn)行修改然而如果沒有仔細(xì)的分析以及準(zhǔn)確的實(shí)驗(yàn)室結(jié)果則PLL實(shí)際上有可能造成系統(tǒng)的噪聲增加這首先就從本質(zhì)上使采用PLL的做法變得毫無意義

所需要的東西等效于一個(gè)頻帶非常窄的跟蹤濾波器該濾波器接受一個(gè)具有RJ和DJ的輸入且最終輸出只產(chǎn)生盡可能低的本征RJ為此人們發(fā)現(xiàn)FailSafe架構(gòu)具有那些飽受系統(tǒng)DJ困擾的系統(tǒng)所追尋的特性雖然RJ始終存在但減輕RJ被證明同樣是值得考慮的FailSafeTM還根據(jù)高抖動(dòng)衰減提出了大時(shí)鐘倍頻比的概念而這在采用標(biāo)準(zhǔn)PLL器件時(shí)是非常難以實(shí)現(xiàn)的由于我們正在處理的是如何減輕抖動(dòng)因而此類應(yīng)用完全有理由使用一個(gè)更加合適的名稱在下文中所討論的器件被稱為帶寬可調(diào)抖動(dòng)衰減器或BAJA芯片

BAJA架構(gòu)概述

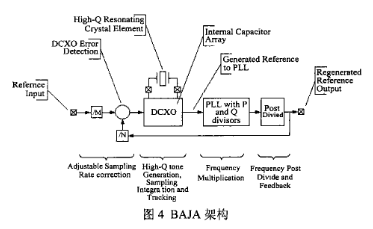

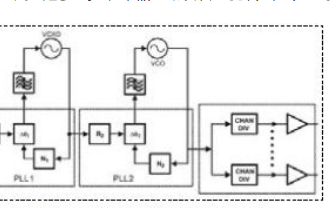

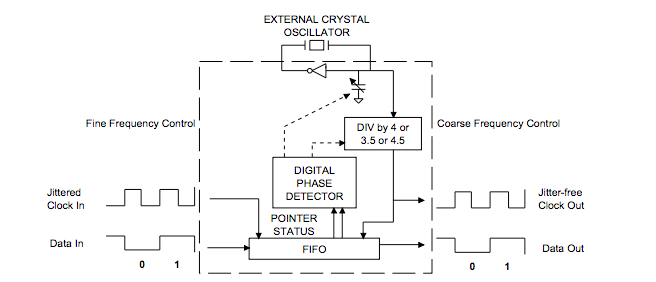

BAJA包括兩個(gè)通過前饋和反饋通路進(jìn)行通信的獨(dú)立本征功能電路第一項(xiàng)主要功能是對(duì)只能被緩沖或以這樣或那樣的方式校正至可用電容器所允許的最大偏移量的時(shí)鐘發(fā)生提供支持即VCXO作用校正需要一個(gè)基準(zhǔn)輸入以及來自BAJA輸出的反饋信號(hào)然而在沒有基準(zhǔn)輸入的情況下操作將繼續(xù)進(jìn)行這就是最初采用FailSafe架構(gòu)的主要原因之一采用時(shí)鐘發(fā)生這一稱謂是準(zhǔn)確的因?yàn)樗⒉簧婕昂铣梢粋€(gè)晶體用于生成被用來滿足同步要求的基準(zhǔn)頻率該功能被稱為DCXO因?yàn)樗鹬鴶?shù)字受控晶體振蕩器的作用由于采用了內(nèi)部晶體容性陣列設(shè)計(jì)因此晶體的推挽操作原理與模-數(shù)轉(zhuǎn)換器相似由于高頻顫動(dòng)具有提高編解碼器的信噪比SNR的作用所以存在于基準(zhǔn)輸入上的噪聲也會(huì)使DCXO響應(yīng)產(chǎn)生高頻顫動(dòng)

DCXO的作用是產(chǎn)生一個(gè)相位噪聲非常低的振蕩器高Q值該振蕩器能夠通過反饋來在一個(gè)有限的頻偏范圍內(nèi)對(duì)輸入進(jìn)行跟蹤從本質(zhì)上說這仿效的是跟蹤濾波器的原理應(yīng)當(dāng)了解的是基準(zhǔn)時(shí)鐘與晶體頻率之間不必有任何的共同之處這就為基準(zhǔn)頻率走低至8kHz以控制BAJA并在具有極低抖動(dòng)的器件中生成一個(gè)頻率達(dá)數(shù)百赫茲的輸出創(chuàng)造了條件這種做法與能夠進(jìn)行倍頻但抖動(dòng)往往會(huì)因PLL環(huán)路更新速率較低而有所增加的傳統(tǒng)PLL設(shè)計(jì)存在著很大的差異在BAJA架構(gòu)中倍頻比可以達(dá)到幾個(gè)數(shù)量級(jí)而不會(huì)使抖動(dòng)響應(yīng)發(fā)生劣化

在DCXO輸出之后是采用傳統(tǒng)PLL技術(shù)的時(shí)鐘合成及倍頻現(xiàn)在提供給PLL的是一個(gè)抖動(dòng)較低與原始基準(zhǔn)無關(guān)而與跟蹤DXCO密切相關(guān)的高基準(zhǔn)頻率高PLL基準(zhǔn)頻率會(huì)轉(zhuǎn)化為用于前饋和反饋除法器的高校正速率BAJA的編程涉及到頻率比的選擇圖4示出了BAJA架構(gòu)輸入定時(shí)脈沖源基準(zhǔn)信號(hào)通過M分頻器之后可與通過N除法器的器件輸出進(jìn)行比較產(chǎn)生于M和N除法器之間差異的校正信息指示DCXO改變晶體頻率通過一個(gè)內(nèi)部PLL所進(jìn)行的倍頻操作的作用是提供一個(gè)可編程輸出頻率和一個(gè)直接取自晶體信號(hào)源的基準(zhǔn)后置分頻和通過N除法器所進(jìn)行的反饋的目的在于使器件與基準(zhǔn)輸入相同步

旨在實(shí)現(xiàn)最佳抖動(dòng)衰減的BAJA調(diào)整

雖然尚有大量的實(shí)驗(yàn)室分析工作有待完成但早期的經(jīng)驗(yàn)數(shù)據(jù)表明輸出DJ在存在輸入DJ的情況下會(huì)發(fā)生顯著的衰減為獲得最佳響應(yīng)而對(duì)BAJA所進(jìn)行的編程將需要做一些實(shí)驗(yàn)這是由于每個(gè)系統(tǒng)都會(huì)因其配置的不同而呈現(xiàn)出一組或多組獨(dú)特的噪聲分布一般而言人們首選的做法是維持PLL部分中的高校正速率即通過保持盡可能小的P和Q除數(shù)值來使PLL以盡可能高的速率運(yùn)行并讓后置分頻器提供正確的輸出頻率M和N的最佳設(shè)置在滿足能夠最大限度地減少輸入DJ分量的DCXO采樣頻率的條件下進(jìn)行由于至BAJA輸入的PLL輸出是相關(guān)的如果需要實(shí)現(xiàn)同步的話所以之后需要對(duì)設(shè)置比進(jìn)行增減以達(dá)到上述目的實(shí)驗(yàn)室分析在采用了能夠精確測(cè)量抖動(dòng)分布信息的儀表的情況下開始進(jìn)行

其他一些具有次要影響但迄今為止幾乎未引起人們關(guān)注的因素存在于晶體部分與我們的窄帶濾波器非常相似晶體的Q值開始成為藉以生成一個(gè)無噪聲的基準(zhǔn)時(shí)鐘脈沖源并在DCXO高頻顫動(dòng)時(shí)設(shè)定頻率變換速率的方法就我們目前業(yè)已完成的有限工作臺(tái)試驗(yàn)而言采用的是Q值略高于100K的晶體做出這種選擇純粹是基于這樣的考慮即當(dāng)與該器件一道工作時(shí)最高的晶體Q值可能并不是唯一的目標(biāo)對(duì)BAJA轉(zhuǎn)移函數(shù)進(jìn)行整形可能需要關(guān)注一些Q值較低的器件比如陶瓷諧振器以提供一種不同的響應(yīng)分布這種概念也許會(huì)被用于降低EMI的擴(kuò)頻系統(tǒng)所接受在這種系統(tǒng)中允許BAJA對(duì)響應(yīng)曲線進(jìn)行整形以便讓特定的DJ信息通過

BAJA架構(gòu)還支持一項(xiàng)額外功能該功能允許在器件中設(shè)置16種不同的抖動(dòng)衰減模式模式的選擇是通過外部引腳配置來完成的對(duì)于動(dòng)態(tài)可重構(gòu)系統(tǒng)來說這種方法被證明是極為有用的當(dāng)在系統(tǒng)上進(jìn)行電路板的插拔操作時(shí)噪聲分布會(huì)發(fā)生改變BAJA的作用是為現(xiàn)有的特定電路板配置提供優(yōu)化的抖動(dòng)衰減可對(duì)一個(gè)FailSafe輸出系統(tǒng)鎖定進(jìn)行邏輯監(jiān)控以確保獲得完全的器件同步

實(shí)驗(yàn)的設(shè)計(jì)

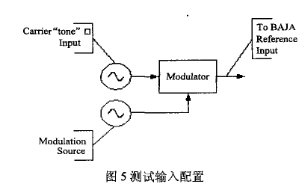

最為困難的工作之一是如何定義一組能夠滿足某些常見系統(tǒng)表示法的噪聲條件選擇了兩種受控噪聲注入分布該過程包括增加平均高斯白噪聲我們的RJ影響以及通過對(duì)一個(gè)方波進(jìn)行微分處理以抽取邊緣速率信息的方法來進(jìn)行脈沖調(diào)制后者的目的是在信號(hào)上生成一個(gè)DJ分量載波音輸入由一個(gè)噪聲層特性遠(yuǎn)遠(yuǎn)低于噪聲調(diào)制分布的無干擾型音頻發(fā)生器提供的該載頻的漂移也非常低于是長(zhǎng)期抖動(dòng)特性保持穩(wěn)定載頻和調(diào)制信號(hào)源輸入均被饋入調(diào)制器而調(diào)制器的輸出則被傳遞給至BAJA器件的基準(zhǔn)輸入

由于噪聲測(cè)量從很大程度上來說是一種統(tǒng)計(jì)特性測(cè)量因此我們的實(shí)驗(yàn)設(shè)計(jì)要求采用歸一化常數(shù)來獲得一個(gè)基準(zhǔn)點(diǎn)在這種場(chǎng)合調(diào)制指數(shù)將被增加直到一個(gè)1ns峰-峰測(cè)量結(jié)果能夠在10s的最大時(shí)間窗口間隔上保持一致為止從統(tǒng)計(jì)的立場(chǎng)出發(fā)我們的分析捕獲了至少6的采樣內(nèi)容

我們所做的第一個(gè)試驗(yàn)是采用一個(gè)具有良好工作性能的白高斯噪聲信號(hào)源來對(duì)一個(gè)音調(diào)進(jìn)行調(diào)制對(duì)于脈沖系統(tǒng)必須規(guī)定重復(fù)頻率和占空比的選擇依據(jù)對(duì)于脈沖頻率研究了100kHz和33kHz兩種設(shè)計(jì)依據(jù)其中100kHz用于模擬一個(gè)開關(guān)模式電源而33kHz則用于受EMI影響的系統(tǒng)和擴(kuò)頻定時(shí)解決方案中的典型調(diào)制頻率當(dāng)占空比被選為50%時(shí)脈沖頻率即被選定為33kHz調(diào)制信號(hào)源的頻率被增加直至觀測(cè)到一個(gè)1ns的峰-峰輸出調(diào)制幅度為止

試驗(yàn)結(jié)果

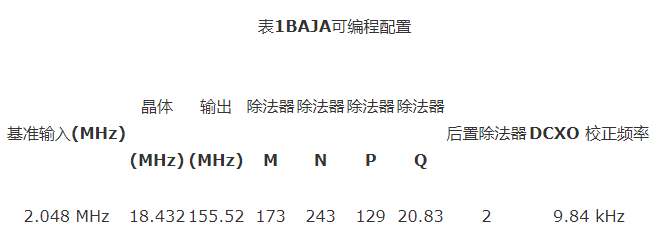

表1羅列了針對(duì)BAJA配置的編程參數(shù)設(shè)置由于BAJA是可編程的故可以選用多種系統(tǒng)專用頻率本次試驗(yàn)的目的在于將一個(gè)分別滿足2.048MHz和155.52MHz的輸入和輸出標(biāo)準(zhǔn)的晶體用作通用通信頻率并未嘗試針對(duì)輸入DJ來優(yōu)化校正速率

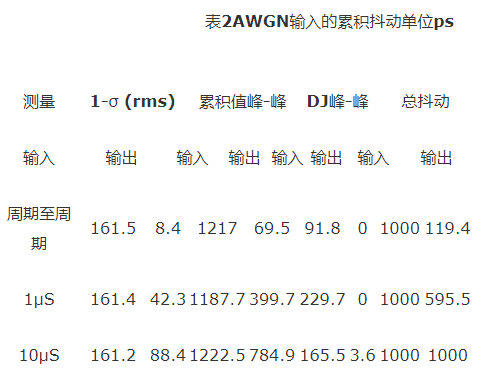

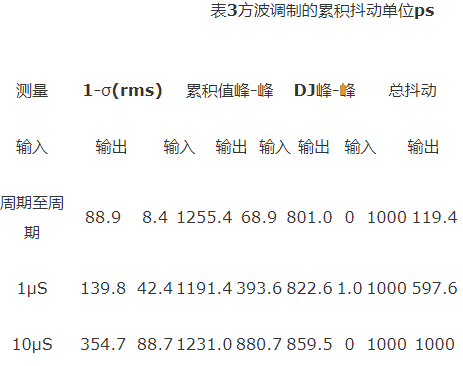

表2至表4 匯總了實(shí)驗(yàn)室數(shù)據(jù)結(jié)果針對(duì)AWGN輸入條件進(jìn)行了三項(xiàng)測(cè)量并采用脈沖注入對(duì)DJ進(jìn)行了相同項(xiàng)目的測(cè)量每組測(cè)量均包括周期至周期以及1s和10s間隔這三個(gè)項(xiàng)目對(duì)各個(gè)BAJA輸入至輸出做了比較表4包括了本征測(cè)量以便于對(duì)實(shí)驗(yàn)室設(shè)置的噪聲層有一個(gè)更好的認(rèn)識(shí)雖然本征噪聲層看上去并不令人滿意今后還需在某些方面加以改進(jìn)但毋庸置疑的是BAJA在未調(diào)制條件下將繼續(xù)展現(xiàn)優(yōu)良的工作性能

從以上的表格可見在最小抖動(dòng)注入為42psRMS的情況下實(shí)現(xiàn)了8.4psRMS的BAJA噪聲層在標(biāo)準(zhǔn)的實(shí)驗(yàn)室試驗(yàn)條件下周期至周期抖動(dòng)至少降低了4倍而且長(zhǎng)期測(cè)量結(jié)果顯示時(shí)間間隔為1s時(shí)抖動(dòng)至少衰減4倍而在時(shí)間間隔為10s的極端條件下的抖動(dòng)衰減倍數(shù)為2不包括表4

表中還列出了相同設(shè)置條件下的峰-峰累積抖動(dòng)和DJ令人驚訝的是BAJA的運(yùn)用使得DJ顯著下降達(dá)到了儀表的分辨率水平當(dāng)我發(fā)現(xiàn)DJ幾乎為零時(shí)一度感到難以相信但最終還是接受了事實(shí)是當(dāng)下一次您的系統(tǒng)中充斥了DJ時(shí)不管在什么情況下BAJA都會(huì)為您提供一個(gè)值得認(rèn)真研究的衰減DJ響應(yīng)

總結(jié)

對(duì)于需要考慮DJ的系統(tǒng)BAJA可以提供幫助雖然從本質(zhì)上說噪聲是任何系統(tǒng)的一部分但是如果您想大幅度地減少重新設(shè)計(jì)的工作量則噪聲衰減機(jī)制或許就是至關(guān)重要的一環(huán)就DCXO校正速率在優(yōu)化抖動(dòng)衰減以及晶體Q值的選擇依據(jù)方面所起的作用而言BAJA還有許多工作要做然而根據(jù)最新的實(shí)驗(yàn)室信息以及所提供的一致性數(shù)值當(dāng)下一次時(shí)鐘脈沖源上需要進(jìn)行嚴(yán)格的信號(hào)修整時(shí)BAJA或許就是能夠滿足您要求的解決方案

責(zé)任編輯:gt

-

噪聲

+關(guān)注

關(guān)注

13文章

1121瀏覽量

47402 -

pll

+關(guān)注

關(guān)注

6文章

776瀏覽量

135141 -

測(cè)量

+關(guān)注

關(guān)注

10文章

4854瀏覽量

111250

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

請(qǐng)問時(shí)鐘抖動(dòng)或結(jié)束時(shí)鐘抖動(dòng)的最佳方法是什么?

采用片內(nèi)PLL實(shí)現(xiàn)實(shí)速掃描測(cè)試的方案

評(píng)估低抖動(dòng)PLL時(shí)鐘發(fā)生器的電源噪聲抑制性能

MAX3625B 抖動(dòng)僅為0.36ps的PLL時(shí)鐘發(fā)生器

可再配置PLL的最佳配置

PLL抖動(dòng)及其對(duì)ECAN?技術(shù)通信的影響

Si5345和SI5344及SI5342系列抖動(dòng)衰減時(shí)鐘倍增器的數(shù)據(jù)手冊(cè)免費(fèi)下載

級(jí)聯(lián)式PLL時(shí)鐘抖動(dòng)濾除技術(shù)實(shí)現(xiàn)的設(shè)計(jì)說明

基于CS61575和CS61574A的抖動(dòng)衰減設(shè)計(jì)

抖動(dòng)衰減時(shí)鐘設(shè)計(jì)與應(yīng)用技巧資料下載

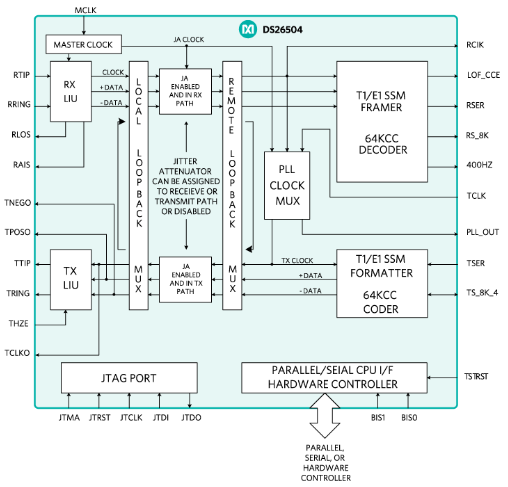

使用DS26504抖動(dòng)衰減器的設(shè)計(jì)考慮

評(píng)估低抖動(dòng)PLL時(shí)鐘發(fā)生器的電源噪聲抑制

使用外部 PLL 改善 FPGA 通信接口時(shí)鐘抖動(dòng)

PLL抖動(dòng)對(duì)GSPS ADC SNR及性能優(yōu)化的影響

采用PLL技術(shù)實(shí)現(xiàn)最佳抖動(dòng)衰減的BAJA調(diào)整

采用PLL技術(shù)實(shí)現(xiàn)最佳抖動(dòng)衰減的BAJA調(diào)整

評(píng)論