引言

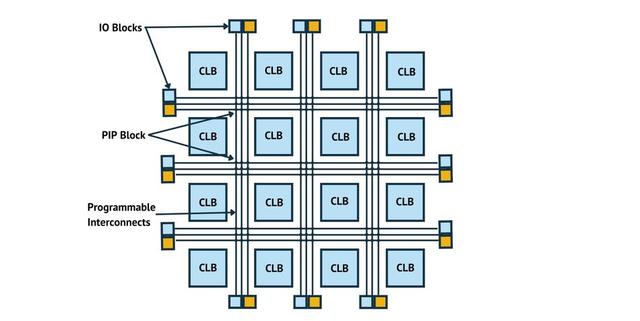

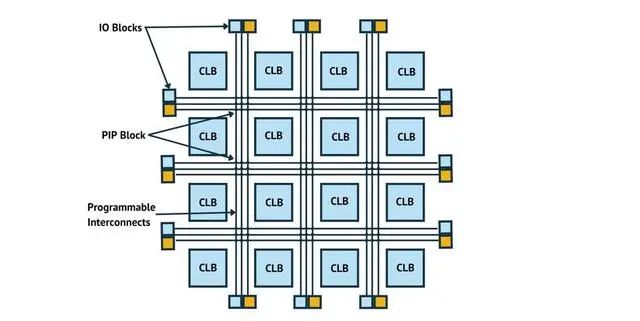

利用硬件描述語言結(jié)合可編程邏輯器件(PLD)可以極大地方便數(shù)字集成電路的設(shè)計(jì),本文介紹一種利用VHDL硬件描述語言結(jié)合現(xiàn)場(chǎng)可編程門陣列(FPGA)設(shè)計(jì)的數(shù)控延時(shí)器,延時(shí)器在時(shí)鐘clk的作用下,從8位數(shù)據(jù)線輸入延時(shí)量,到LATCH高電平時(shí)鎖存數(shù)據(jù),可以實(shí)現(xiàn)對(duì)觸發(fā)脈沖TRIG的任意量的延時(shí)。由于延時(shí)范圍不同,設(shè)計(jì)所用到的FPGA的資源也不同,本文詳細(xì)介紹最大延時(shí)量小于觸發(fā)脈沖周期的情況。該延時(shí)器的軟件編程和調(diào)試均在MuxplusⅡ環(huán)境下完成,系統(tǒng)設(shè)計(jì)選用Altera公司的EPFl0K30AQC208-3,EPCI44l型專用電路,與DSP相結(jié)合,應(yīng)用于雷達(dá)目標(biāo)模擬器的控制部分,實(shí)現(xiàn)對(duì)目標(biāo)距離的模擬。

2 設(shè)計(jì)原理

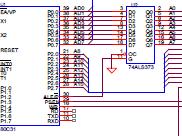

設(shè)計(jì)的數(shù)控延時(shí)器采用3個(gè)串聯(lián)計(jì)數(shù)器來實(shí)現(xiàn)。由于在觸發(fā)脈沖TRIG的上升沿開始延時(shí),使用時(shí)鐘的上升沿計(jì)數(shù),考慮到VHDL對(duì)時(shí)鐘描述的限制,設(shè)計(jì)采用計(jì)數(shù)器l產(chǎn)生同步脈沖SYNC,寬度為Tclk,利用SYNC的高電平觸發(fā)cflag,并在延時(shí)結(jié)束后cflag清零;計(jì)數(shù)器2計(jì)算延時(shí)的長度;計(jì)數(shù)器3計(jì)算所要產(chǎn)生的輸出脈沖OUTPUT的脈寬,并在計(jì)數(shù)結(jié)束時(shí)對(duì)計(jì)數(shù)器2和計(jì)數(shù)器3清零。延時(shí)器的外部接口電路如圖1所示,原理框圖如圖2所示。整個(gè)電路的設(shè)計(jì)采用同步時(shí)鐘計(jì)數(shù)以盡量減少因局部時(shí)鐘不穩(wěn)定所產(chǎn)生的毛刺和競(jìng)爭(zhēng)冒險(xiǎn)。

該數(shù)控延時(shí)器低電平時(shí)鎖存數(shù)據(jù),高電平時(shí)改變內(nèi)部寄存器的數(shù)值(與AD9501型數(shù)控延時(shí)器的數(shù)據(jù)鎖存端電平相反)。一般情況下,觸發(fā)脈沖與時(shí)鐘的上升沿是一致的,如果輸入的觸發(fā)脈沖與時(shí)鐘不一致,則整個(gè)電路的延時(shí)將產(chǎn)生一定的誤差。時(shí)序仿真如圖3所示,延時(shí)量由dlyLH為高電平時(shí)數(shù)據(jù)總線data8上的數(shù)據(jù)決定。

該數(shù)控延時(shí)器的VHDL硬件描述語言程序如下:

在該程序中,cntl為延時(shí)量,cnt2為輸出脈沖的寬度,cflag為開始計(jì)數(shù)的標(biāo)志,該段程序在觸發(fā)脈沖的周期大于256xTclk時(shí),最大延時(shí)量為256×Tclk,如果觸發(fā)脈沖周期小于256xTclk,則最大延時(shí)量為Tclk-Toutput(Toutput為輸出脈沖的寬度)。

事實(shí)上,在實(shí)際應(yīng)用中,延時(shí)后的輸出脈沖與輸入的觸發(fā)脈沖的頻率并不相同,譬如在設(shè)計(jì)雷達(dá)目標(biāo)模擬器時(shí)要求延時(shí)后產(chǎn)生一連串的7分頻時(shí)鐘,時(shí)序如圖4所示(延時(shí)后產(chǎn)生11個(gè)7分頻的脈沖,占空比為2:5)。

要產(chǎn)生上述觸發(fā)脈沖,只需改變計(jì)數(shù)器2的長度,并在程序中加入case判斷語句即可。

3 延時(shí)范圍討論

3.1 延時(shí)范圍小于觸發(fā)脈沖周期

這種情況只需增加數(shù)據(jù)輸入端的位數(shù),不過一般情況下,數(shù)據(jù)輸入端位數(shù)是固定的,這時(shí)可以在FPGA的內(nèi)部定義多位的數(shù)據(jù)寄存器。以延時(shí)范圍為224xTclk為例,在FPGA內(nèi)部定義24位的數(shù)據(jù)寄存器,并定義3條地址線dlyLHl、dlyLH2和dlyLH3,通過8位數(shù)據(jù)總線分3次向數(shù)據(jù)寄存器送數(shù),送數(shù)時(shí)間應(yīng)在前一脈沖延時(shí)結(jié)束之后與下一脈沖到來之前。數(shù)據(jù)送入寄存器的程序如下:

3.2 延時(shí)范圍大于觸發(fā)脈沖周期

這種情況在實(shí)際應(yīng)用中比較廣泛,譬如在雷達(dá)模擬器的設(shè)計(jì)中,所模擬的目標(biāo)的距離范圍一般都很大,因而輸出延時(shí)脈沖的延時(shí)量將大于1個(gè)觸發(fā)脈沖周期,這時(shí)在考慮到FPGA資源的前提下,可以采用多路延時(shí)合并的處理方法。以延時(shí)范圍小于4個(gè)周期為例,具體時(shí)序如圖5所示。

利用SYNC信號(hào)4分頻并產(chǎn)生4路分頻后的信號(hào)。在FPGA內(nèi)部設(shè)計(jì)4個(gè)延時(shí)電路,SYNCl、SYNC2、SYNC3、SYNCA分別作為4個(gè)延時(shí)電路的觸發(fā)信號(hào),每個(gè)延時(shí)電路仿照第一種延時(shí)范圍的設(shè)計(jì)方法,輸出觸發(fā)脈沖通過4個(gè)或門送到輸出端OUTPUT。值得注意的是每個(gè)延時(shí)電路內(nèi)部都要定義1個(gè)與DATAREG位數(shù)相同的數(shù)據(jù)寄存器,延時(shí)數(shù)據(jù)在延時(shí)開始時(shí)送入內(nèi)部寄存器。使用多路延時(shí)合并方法最關(guān)鍵的是要產(chǎn)生準(zhǔn)確的分頻脈沖,如果產(chǎn)生的脈沖有毛刺,或者電路在設(shè)計(jì)的時(shí)候存在冒險(xiǎn),整個(gè)延時(shí)系統(tǒng)有可能都不能正常工作。

4 延時(shí)誤差分析

以延時(shí)范圍小于觸發(fā)脈沖周期為例,分析固定延時(shí)及延時(shí)誤差。

該延時(shí)器在Muxplus Ⅱ環(huán)境下從輸入時(shí)鐘Tclk到dlytrig的延時(shí)為8.2 ns;產(chǎn)生SYNC的寬度為Tclk。因此在觸發(fā)脈沖上升沿與時(shí)鐘信號(hào)上升沿對(duì)時(shí),該延時(shí)電路的固有延時(shí)為8.2 ns+2Tclk。但一般情況下,觸發(fā)脈沖的上升沿與時(shí)鐘的上升沿并不是一致的,根據(jù)二者之間的關(guān)系可知,最大延時(shí)誤差T滿足:O

由于該數(shù)控延時(shí)器使用時(shí)鐘來計(jì)數(shù),因此延時(shí)量只能為Tclk的整數(shù)倍。如果設(shè)計(jì)者希望有更精確的延時(shí),可以在設(shè)計(jì)的基礎(chǔ)上外加一片AD9501,該器件的延時(shí)可以精確到(Ttotal+Td)×1/28,其中Ttotal是AD9501的總延時(shí),Td是AD9501的固有延時(shí)。

5 結(jié)束語

本文詳細(xì)介紹了利用VHDL硬件描述語言結(jié)合FPGA設(shè)計(jì)一種數(shù)控延時(shí)器的方法,討論了延時(shí)范圍,分析了延時(shí)誤差,該延時(shí)器的設(shè)計(jì)旨在和DSP相結(jié)合實(shí)現(xiàn)對(duì)延時(shí)信號(hào)的處理。隨著EDA技術(shù)的飛速發(fā)展,使用硬件描述語言設(shè)計(jì)FPGA是電子設(shè)計(jì)人員應(yīng)該掌握的一門技術(shù)。同時(shí),將DSP和FPGA技術(shù)相結(jié)合是進(jìn)行數(shù)字信號(hào)處理的一種趨勢(shì)。

-

集成電路

+關(guān)注

關(guān)注

5403文章

11698瀏覽量

364688 -

可編程

+關(guān)注

關(guān)注

2文章

892瀏覽量

40116 -

延時(shí)器

+關(guān)注

關(guān)注

1文章

36瀏覽量

15283

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

現(xiàn)場(chǎng)可編程門陣列

現(xiàn)場(chǎng)可編程門陣列有哪些應(yīng)用?

XC7K325T-2FFG900I現(xiàn)場(chǎng)可編程門陣列

XA6SLX25-3CSG324Q現(xiàn)場(chǎng)可編程門陣列

XC5VLX85-1FF676C現(xiàn)場(chǎng)可編程門陣列

XC7A200T-2FFV1156I現(xiàn)場(chǎng)可編程門陣列

FPGA-現(xiàn)場(chǎng)可編程門陣列

利用PSD8XXF的特性實(shí)現(xiàn)現(xiàn)場(chǎng)可編程門陣列的配置

現(xiàn)場(chǎng)可編程門陣列的結(jié)構(gòu)與設(shè)計(jì)

現(xiàn)場(chǎng)可編程門陣列的供電原理及應(yīng)用

現(xiàn)場(chǎng)可編程邏輯門陣列器件 FPGA原理及應(yīng)用設(shè)計(jì)

什么是FPGA?FPGA現(xiàn)場(chǎng)可編程門陣列的綜合指南

FPGA現(xiàn)場(chǎng)可編程門陣列的綜合指南

如何使用可編程門陣列實(shí)現(xiàn)可控延時(shí)器的設(shè)計(jì)

如何使用可編程門陣列實(shí)現(xiàn)可控延時(shí)器的設(shè)計(jì)

評(píng)論