1 引言

隨著人類對(duì)空間探索的深入,空間環(huán)境對(duì)空間飛行器的電子設(shè)備和器件的影響逐漸顯現(xiàn) 出來(lái)。空間輻射效應(yīng),特別是單粒子效應(yīng),對(duì)空間任務(wù)的完成具有潛在的巨大危害。星載計(jì) 算機(jī)是衛(wèi)星的核心部件,在空間輻照環(huán)境下,必須充分考慮單粒子翻轉(zhuǎn)現(xiàn)象對(duì)星載計(jì)算機(jī)程 控功能的破壞或影響。針對(duì)該問題, 目前普遍采用糾錯(cuò)檢錯(cuò)(EDAC)設(shè)計(jì)對(duì)星載計(jì)算機(jī)的RAM 存儲(chǔ)單元進(jìn)行糾錯(cuò)檢錯(cuò)處理來(lái)消除SEU故障。

EDAC功能可采用硬件和軟件兩種手段來(lái)實(shí)現(xiàn)。采用軟件手段實(shí)現(xiàn),需要在讀寫RAM存儲(chǔ) 單元時(shí),對(duì)存儲(chǔ)數(shù)據(jù)和冗余信息進(jìn)行計(jì)算,因而要占用大量的CPU時(shí)間。對(duì)于星載計(jì)算機(jī)而 言,由于CPU器件選型的局限,限制了CPU的性能,使CPU資源非常寶貴,因此目前普遍采用 的是硬件手段來(lái)實(shí)現(xiàn)EDAC功能。隨著FPGA在通信信息特別是在航天領(lǐng)域的廣泛應(yīng)用,F(xiàn)PGA 已成為EDAC功能實(shí)現(xiàn)的最佳硬件手段。從目前可獲得的資料看,近些年歐美發(fā)射的衛(wèi)星均采 用了FPGA作為星載計(jì)算機(jī)的核心器件。

2 基于漢明碼的傳統(tǒng)EDAC設(shè)計(jì)

2.1漢明編碼

目前有許多編碼可以用來(lái)作為抗SEU的糾錯(cuò)碼使用,漢明編碼是最常用的EDAC編碼,由 Hamming于1950年構(gòu)造。這種編碼可以進(jìn)行檢錯(cuò)和糾錯(cuò),可以檢測(cè)1比特和2比特錯(cuò)誤,只能 糾正1比特錯(cuò)誤,因此適用于單組數(shù)據(jù)中出現(xiàn)多個(gè)錯(cuò)誤位概率較低的情況,這恰與SEU經(jīng)常會(huì) 修改星上RAM存儲(chǔ)單元1比特信息的情況相符。

漢明編碼的實(shí)現(xiàn)增加的硬件資源主要是存儲(chǔ)器單元,用來(lái)存儲(chǔ)冗余數(shù)據(jù),另外還增加了 編碼和解碼電路,參加編碼和解碼的異或門電路隨著原始數(shù)據(jù)位數(shù)的增加而線性增加。在處 理性能方面,編碼和解碼造成一定的延時(shí),增加了存儲(chǔ)器的讀寫時(shí)間。

2.2傳統(tǒng)的EDAC電路設(shè)計(jì)

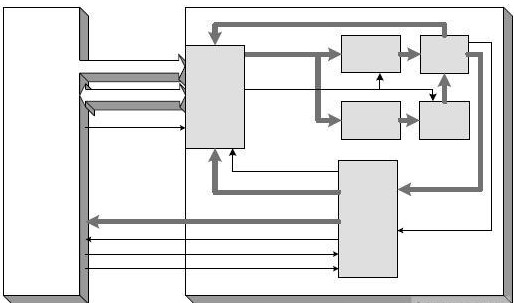

傳統(tǒng)的EDAC電路設(shè)計(jì)僅實(shí)現(xiàn)讀寫功能,基本原理框圖如圖1所示.寫操作時(shí),CPU將數(shù)據(jù)送入EDAC編碼模塊中,EDAC編碼模塊根據(jù)該數(shù)據(jù)生成校驗(yàn)碼,并將原始數(shù)據(jù)和校驗(yàn)碼分別寫 入數(shù)據(jù)RAM和校驗(yàn)RAM中;讀操作時(shí),CPU將數(shù)據(jù)RAM和校驗(yàn)RAM中的數(shù)據(jù)取出,送入EDAC糾錯(cuò)模 塊中,EDAC糾錯(cuò)模塊將正確的數(shù)據(jù)送至CPU。這里EDAC編碼\糾錯(cuò)模塊的硬件實(shí)現(xiàn)可以是專用 芯片,也可以采用通用的中小規(guī)模集成電路搭建。

SEU造成的RAM單元1比特錯(cuò)誤如果不定時(shí)清除,就會(huì)產(chǎn)生累積,使計(jì)算機(jī)由此處理的結(jié) 果產(chǎn)生出2比特甚至更多比特錯(cuò)誤,這種情況下將無(wú)法采用EDAC功能進(jìn)行數(shù)據(jù)糾錯(cuò),導(dǎo)致系 統(tǒng)錯(cuò)誤操作甚至任務(wù)失敗。因此定時(shí)對(duì)RAM存儲(chǔ)單元進(jìn)行更新是必要的,但在傳統(tǒng)EDAC電路 設(shè)計(jì)下,對(duì)RAM存儲(chǔ)單元的更新只能由計(jì)算機(jī)的CPU(單片機(jī))進(jìn)行,其操作流程如下:

(1) 從存儲(chǔ)單元讀出數(shù)據(jù);

(2) 將讀出數(shù)據(jù)重寫入;

(3) 重復(fù)(1)~(2),直至全部單元更新完。

以航天計(jì)算機(jī)常用的80C32單片機(jī)為例,CPU對(duì)外部存儲(chǔ)單元的讀或?qū)懖僮餍枰?個(gè)指令 周期,讀完再寫入需要4個(gè)指令周期,每個(gè)指令周期包含12個(gè)時(shí)鐘。假設(shè)CPU時(shí)鐘為20MHz, 更新1M個(gè)RAM存儲(chǔ)單元需要的CPU時(shí)間為:4×12×1M 20MHz = 2.4s。

對(duì)于星上非常緊張的CPU資源來(lái)說(shuō),這是難以接受的,大大增加了星上CPU軟件的設(shè)計(jì)難 度。這種方法的另一個(gè)大的缺點(diǎn)是無(wú)法獲得數(shù)據(jù)錯(cuò)誤信息,因?yàn)镃PU直接讀取的是糾錯(cuò)后的 數(shù)據(jù),所以無(wú)法對(duì)星上SEU造成RAM單元出錯(cuò)的概率和錯(cuò)誤模式進(jìn)行統(tǒng)計(jì)。

3 基于FPGA的自檢EDAC設(shè)計(jì)

3.1 功能分析

由于FPGA的內(nèi)部大量的邏輯資源,使EDAC電路設(shè)計(jì)可以實(shí)現(xiàn)更加復(fù)雜的功能。在星載計(jì) 算機(jī)中,為了提高效率并節(jié)省CPU資源,一個(gè)理想的EDAC電路設(shè)計(jì),應(yīng)具有以下三部分功能:

(1)數(shù)據(jù)讀寫功能。在CPU寫操作時(shí),對(duì)原始數(shù)據(jù)進(jìn)行編碼,生成校驗(yàn)碼,并將原始數(shù) 據(jù)和校驗(yàn)碼存儲(chǔ);在CPU讀操作時(shí),從存儲(chǔ)器中取出原始數(shù)據(jù)和校驗(yàn)碼,進(jìn)行計(jì)算,如有錯(cuò) 誤,將錯(cuò)誤糾正后輸出,如無(wú)錯(cuò)誤,直接將原始數(shù)據(jù)輸出。

(2)自檢、自糾錯(cuò)功能。在CPU控制要求下,可自動(dòng)對(duì)所有EDAC保護(hù)的RAM存儲(chǔ)區(qū)進(jìn)行 順序讀取和校驗(yàn),檢測(cè)出錯(cuò)誤數(shù)據(jù)或校驗(yàn)碼。在自檢狀態(tài)下,如果由CPU配置為自糾錯(cuò)狀態(tài), 當(dāng)某一RAM單元檢測(cè)出單比特錯(cuò)誤后,自動(dòng)將正確數(shù)據(jù)和校驗(yàn)碼重新寫入該RAM單元。該項(xiàng)功 能的實(shí)施,基本上可保證SEU對(duì)計(jì)算機(jī)RAM區(qū)造成的影響及時(shí)得到修復(fù)。

(3)錯(cuò)誤信息處理功能。在CPU讀操作或者自檢狀態(tài)下,通過輸出錯(cuò)誤標(biāo)志信號(hào),對(duì)CPU 產(chǎn)生中斷,對(duì)產(chǎn)生的錯(cuò)誤進(jìn)行相應(yīng)處理。在CPU讀操作或者自檢狀態(tài)下,如果檢測(cè)出錯(cuò)誤, 將出錯(cuò)的地址、原始數(shù)據(jù)和校驗(yàn)碼進(jìn)行暫存,可由CPU讀取,進(jìn)行相應(yīng)處理。

3.2 設(shè)計(jì)與實(shí)現(xiàn)

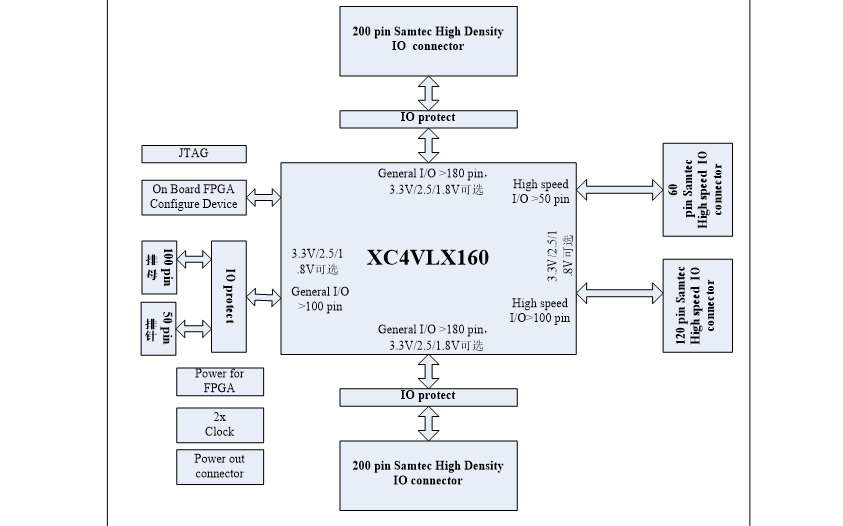

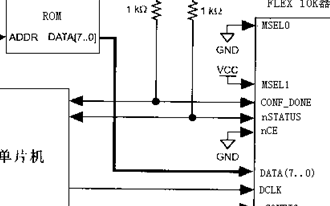

根據(jù)以上分析,筆者設(shè)計(jì)了如圖2所示的自檢EDAC電路,EDAC的功能主要由FPGA來(lái)實(shí)現(xiàn)。 到目前為止,具有航天等級(jí)的FPGA芯片已經(jīng)具有內(nèi)置的CPU硬核以及高達(dá)2.5Mbit的RAM資源, 因此該設(shè)計(jì)中的CPU和RAM模塊均可以是FPGA內(nèi)部資源,當(dāng)內(nèi)部資源無(wú)法滿足設(shè)計(jì)要求時(shí),也 可以采用外置CPU芯片或外置RAM芯片。

在本設(shè)計(jì)中,我們采用外置的CPU芯片和內(nèi)置的RAM單元,作為自檢EDAC電路的硬件平臺(tái) (或環(huán)境、資源)。CPU芯片在這里起到的作用是啟動(dòng)EDAC自檢,處理錯(cuò)誤中斷,向地面?zhèn)?送錯(cuò)誤信息,并根據(jù)地面要求對(duì)錯(cuò)誤信息進(jìn)行處理。

在該設(shè)計(jì)中,檢測(cè)一個(gè)存儲(chǔ)單元地址僅需要4個(gè)時(shí)鐘周期,如果開啟自糾錯(cuò)功能,并且 檢測(cè)到單比特錯(cuò)誤,再增加2個(gè)時(shí)鐘周期用來(lái)糾錯(cuò)。因此如果時(shí)鐘為20MHz,并且錯(cuò)誤數(shù)據(jù)較 少,則更新1M個(gè)RAM存儲(chǔ)單元需要的時(shí)間約為:4×1M 20MHz = 0.2s。

更重要的是,在這0.2s的時(shí)間里,僅在出現(xiàn)錯(cuò)誤時(shí)需要向計(jì)算機(jī)產(chǎn)生中斷,進(jìn)行相應(yīng)處 理,對(duì)地面進(jìn)行錯(cuò)誤報(bào)告,因而CPU處理時(shí)間很短,節(jié)省了寶貴的CPU資源。

3.3 仿真與驗(yàn)證

在空間環(huán)境下普遍存在的SEU,在地面環(huán)境下是很難獲得的,為了在地面對(duì)該EDAC電路 設(shè)計(jì)進(jìn)行驗(yàn)證,需要采取故障注入手段。由于在本例中RAM存儲(chǔ)單元采用FPGA內(nèi)部資源,因 此故障注入變得相對(duì)簡(jiǎn)單。在FPGA進(jìn)行程序綜合時(shí),可將預(yù)先編制好的RAM存儲(chǔ)單元初始化 文件一起綜合。因此我們可在編制RAM存儲(chǔ)單元初始化文件時(shí),對(duì)某些比特位進(jìn)行修改,以 模擬空間環(huán)境下SEU對(duì)RAM存儲(chǔ)單元的影響。

在這里采用Xilinx公司的XQRV300為硬件載體,該型號(hào)FPGA芯片在航天領(lǐng)域內(nèi)被廣泛使 用。為節(jié)省仿真時(shí)間,數(shù)據(jù)RAM存儲(chǔ)單元采用256*8bit,檢驗(yàn)RAM存儲(chǔ)單元采用25*bit。在 RAM存儲(chǔ)單元初始化文件中,人工加入了12個(gè)單比特錯(cuò)誤,以及1個(gè)兩比特錯(cuò)誤,如下表所示。

為仿真簡(jiǎn)便起見,向存儲(chǔ)單元存放的正確數(shù)據(jù)與存儲(chǔ)單元地址相同。

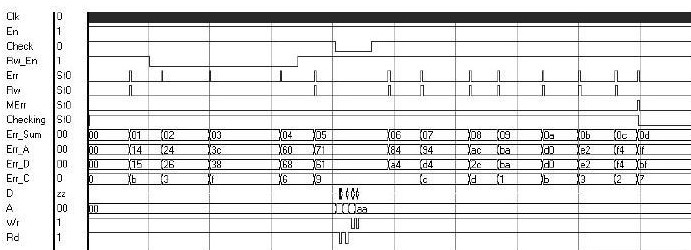

時(shí)鐘選擇為20MHz,通過采用ModelSim軟件進(jìn)行布線后仿真,我們可以得到圖3所示結(jié)果。

圖中: Clk — 系統(tǒng)時(shí)鐘;

En — EDAC 模塊使能控制;

Check — 自檢啟動(dòng)/使能信號(hào)(信號(hào)上升沿觸發(fā)一次巡檢,信號(hào)為低暫停巡檢);

Rw_En — 自糾錯(cuò)使能信號(hào)(為高允許糾錯(cuò));

Err — 錯(cuò)誤中斷(標(biāo)志)信號(hào);

Rw — 自糾錯(cuò)標(biāo)志信號(hào)(為高表示正在進(jìn)行自糾錯(cuò)操作);

MErr — 多比特錯(cuò)誤中斷(標(biāo)志)信號(hào);

Checking — 自檢標(biāo)志(為高表示尚未完成本次巡檢操作);

Err_Sum,Err_A,Err_D,Err_C — 錯(cuò)誤計(jì)數(shù),錯(cuò)誤地址,原始數(shù)據(jù),原始校驗(yàn)碼;

D,A,Wr,Rd — 單片機(jī)數(shù)據(jù)、地址、寫操作、讀操作信號(hào);

從圖中可以看出,啟動(dòng)EDAC自檢后,EDAC開始巡檢RAM存儲(chǔ)單元,產(chǎn)生錯(cuò)誤中斷(標(biāo)志) 信號(hào),給出錯(cuò)誤信息。當(dāng)單片機(jī)需要處理中斷時(shí),將Check信號(hào)置‘0’,可暫時(shí)停止巡檢, 此時(shí)單片機(jī)可對(duì)RAM存儲(chǔ)單元進(jìn)行正常讀寫操作。等中斷處理完后,單片機(jī)將Check信號(hào)置 ‘1’,恢復(fù)RAM巡檢操作。

另外可通過Rw_En的置‘0’或‘1’,來(lái)控制禁止或允許進(jìn)行自糾錯(cuò)操作。

當(dāng)出現(xiàn)可識(shí)別的多位錯(cuò)誤時(shí),產(chǎn)生Err和MErr兩個(gè)錯(cuò)誤中斷(標(biāo)志)信號(hào),但由于漢明碼僅能糾正單比特錯(cuò)誤,因此不進(jìn)行自糾錯(cuò)操作。

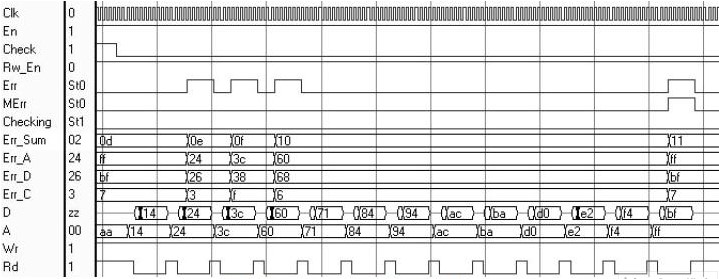

從原注入錯(cuò)誤數(shù)據(jù)對(duì)應(yīng)的地址讀出數(shù)據(jù),仿真輸出結(jié)果如圖4所示。

可以看出除最后一個(gè)地址(FFH)由于兩位錯(cuò)仍輸出錯(cuò)誤外,其他地址輸出數(shù)據(jù)均與地址相同,即為正確數(shù)據(jù)。

其中,24H、3CH、60H三個(gè)地址雖然輸出正確數(shù)據(jù),但仍報(bào)錯(cuò),表明存儲(chǔ)器內(nèi)數(shù)據(jù)仍然 為錯(cuò)誤數(shù)據(jù),在輸出時(shí)進(jìn)行了糾錯(cuò)。這是由于在上次巡檢到這部分地址空間時(shí),通過把Rw_En 信號(hào)拉低,從而禁止了自動(dòng)糾錯(cuò),導(dǎo)致這三個(gè)地址錯(cuò)誤數(shù)據(jù)未被糾正。而在對(duì)其他地址進(jìn)行 數(shù)據(jù)讀取時(shí),未產(chǎn)生錯(cuò)誤標(biāo)志,證明其他錯(cuò)誤數(shù)據(jù)已被糾錯(cuò)。

4 結(jié)論

本文在采用FPGA芯片實(shí)現(xiàn)基本EDAC讀寫功能的設(shè)計(jì)思路基礎(chǔ)上,創(chuàng)建了一種新型的可對(duì) RAM存儲(chǔ)單元進(jìn)行自檢的EDAC功能模塊。該模塊不但可以對(duì)RAM存儲(chǔ)單元進(jìn)行快速巡檢,巡檢 時(shí)間僅為傳統(tǒng)EDAC方法的十二分之一,還可以自動(dòng)糾正已發(fā)現(xiàn)的錯(cuò)誤。該模塊最大的優(yōu)點(diǎn)在 于節(jié)省了單片機(jī)資源,幾乎不需要單片機(jī)的參與即可完成所有自檢功能,從而使基于FPGA 的星載計(jì)算機(jī)對(duì)SEU事件防護(hù)能力得到較大的提升。本文中該模塊采用Verilog硬件描述語(yǔ)言 編程,具有可移植性,這種設(shè)計(jì)方法可用于各種體系結(jié)構(gòu)的星載計(jì)算機(jī)中。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21748瀏覽量

604025 -

RAM

+關(guān)注

關(guān)注

8文章

1369瀏覽量

114758 -

計(jì)算機(jī)

+關(guān)注

關(guān)注

19文章

7511瀏覽量

88137

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

邏輯電路的糾錯(cuò)技術(shù)是如何實(shí)現(xiàn)的?

移動(dòng)通信中變速率自糾錯(cuò)解碼器設(shè)計(jì)

S698M SoC芯片中EDAC模塊的設(shè)計(jì)與實(shí)現(xiàn)

基于FPGA的星載計(jì)算機(jī)自檢EDAC電路設(shè)計(jì)

計(jì)算機(jī)RAM檢錯(cuò)糾錯(cuò)電路的設(shè)計(jì)與實(shí)現(xiàn)

基于FPGA的檢糾錯(cuò)邏輯算法的實(shí)現(xiàn)

用FPGA實(shí)現(xiàn)糾錯(cuò)編碼的一種方法

基于FPGA的光電系統(tǒng)同步自適應(yīng)電路設(shè)計(jì)與實(shí)現(xiàn)

電路設(shè)計(jì)[FPGA]設(shè)計(jì)經(jīng)驗(yàn)

FPGA的硬件電路設(shè)計(jì)教程和FPGA平臺(tái)資料簡(jiǎn)介

FPGA最小系統(tǒng)配置電路設(shè)計(jì)與實(shí)現(xiàn)

FPGA_ASIC-S698MSoC芯片中EDAC模塊的設(shè)計(jì)與實(shí)現(xiàn)

FPGA CPLD數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享.

FPGA-SoC芯片中EDAC模塊的設(shè)計(jì)與實(shí)現(xiàn)

基于FPGA實(shí)現(xiàn)具有自檢、自糾錯(cuò)功能的EDAC電路設(shè)計(jì)

基于FPGA實(shí)現(xiàn)具有自檢、自糾錯(cuò)功能的EDAC電路設(shè)計(jì)

評(píng)論