任意波形發生器( Arbit rary Waveform Generato r,AWG) 是一種多波型的信號發生器, 它不僅能產生正弦波、指數波等常規波形, 也可以表現出載波調制的多樣化, 如: 產生調頻、調幅、調相和脈沖調制等。更可以通過計算機軟件實現波形的編輯, 從而生成用戶所需要的各種任意波形。任意波形發生器的實現方案主要有程序控制輸出、DMA 輸出、可變時鐘計數器尋址和直接數字頻率合成( DDS) 等多種方式 。目前任意波形發生器的研制主要基于DDS 技術, 與傳統的頻率合成器相比, DDS 具有低成本、低功耗、高分辨率和快速轉換時間等優點, 廣泛使用在通信、測量與電子儀器領域, 是設備全數字化的一個關鍵技術。

1 任意波形發生器的理論分析

1. 1 DDS 技術簡介

DDS( Direct Digital Sy nthesis) 的概念由美國學者J. T ier ncy、C. M. Rader 和B. Gold 在1971 年提出。該技術是從相位的概念進行頻率合成, 主要優點是輸出相位連續、相對帶寬較大、頻率分辨率很高、可編程、準確度和穩定度都比較高 。DDS 技術是利用查表法來產生波形, 而通過修改存儲在ROM 里的數據, 就可以產生任意波形。

1. 2 DDS 基本結構

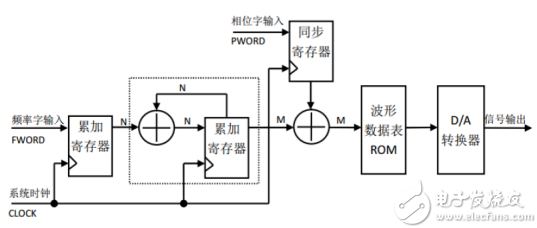

DDS 主要有相位累加器、ROM 波形查詢表、數模轉換器組成。其基本框圖如圖1 所示。

圖1 DDS 結構框圖

線性數字信號通過相位累加器逐級實現, 波形函數存儲在ROM 中, 根據累加器輸出的相位值作為地址,尋找存儲在ROM 中的波形函數的幅度量化值, 完成相位到幅值的轉換, 輸出相對應的序列。

2 硬件電路設計

2. 1 設計方案

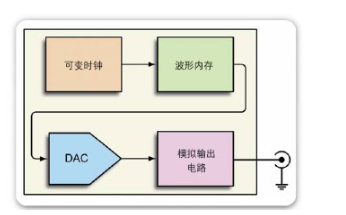

基于FPGA 實現DDS 功能, 通過單片機實現控制。此方案的核心在于FPGA 的設計實現邏輯功能,通過對存儲器查表后輸出信號, 由相連接的數模轉換器轉換為要求的波形。單片機作為控制器, 易于控制與調試。系統框圖如圖2 所示。

圖2 系統框圖

2. 2 D/ A 轉換器的使用

本案采用德州儀器的TLC7528。它是雙路、8 位D/ A 轉換器, 本案設計為: A 路的數字量控制B 路的電壓輸出, B 路則控制輸出的幅度。電路圖可以顯示,VA1( VOB1) 處輸入的A( B) 路電壓范圍為- 5~ 0 V,VA2( VOB2) 處為A( B) 路的電壓為- 5~ 5 V。DA 電路連接圖如圖3 所示。

圖3 TLC7528 電路連接圖

其中因為轉換方法的問題, 產生的零點誤差可以通過調整放大器的零點來校準; 而因為溫度變化產生的溫漂誤差在技術上就比較難消除。關于單極性DAC 的增益誤差可以通過調整放大器的閉環增益來消除。

2. 3 濾波器的設計

一般情況下, 橢圓濾波器的參數靈敏度最高, 在使用用相同階數時, 橢圓濾波器能夠得到最好的矩形系數, 7 階橢圓濾波器在通帶附近的頻點可得到40 dB 的帶外抑制, 很適合將雜散信號濾除。DDS 輸出的另一類波形是頻譜復雜的任意波形, 頻率比較低, 頻譜結構豐富, 具有較高的諧波分量, 選用等波紋誤差線性相位濾波器來濾波, 它在很大范圍內具有固定的延遲, 在遠離截止頻率處, 其幅度響應也比較好。

2. 4 單片機的設計

單片機采用傳統8051 單片機, 晶振為12 MHz, 采用內部振蕩方式; 復位輸入引腳為高電平有效, 保持2 個機器周期以上的的高電平便可以實現對單片機的復位; 采用MAX232 芯片作為串口芯片, 單片機通過異步通信串行接口與其他計算機或者外圍設備進行信息傳遞。

3 基于FPGA的DDS實現

FPGA 芯片采用ALT ERA 公司的CYCLON E 系列EP1C3T 144C8。設計采用Altera 公司的Quar tus , 使用AS 方式與JTAG 配置方式。

3. 1 固定波形輸出

本案使用幾個8 b 的ROM, 存儲深度為1 024 點,用來存儲正弦波等波形數據。每個波形數據存儲在一個固定的ROM 里, 如圖4Sine_ROM, Square _ROM等分別對應正弦、方波等存儲模塊。通過一個使能模塊控制, 采取低電平有效的方式, 選擇性讀取任意模塊的波形。輸出波形時, 僅有單獨一個ROM 工作, 其他模塊為高電平, 保證輸出所需固定波形。使能模塊的輸入端為行列式鍵盤, 設定為: 單鍵控制某一波形輸出。

圖4 波形ROM 與使能控制設計電路圖

3. 2 任意波形輸出

任意波形是由上位機下傳的波形數據, 由單片機控制, 必須設計一個能隨時接受數據更新的RAM。如圖5所示。

圖5 任意波形模塊設計電路圖

選用的D/ A 轉換器為8 位, 所以RAM 的字長也為8 位, 因此波形RAM 的地址線的位數取10 位。為了實現任意波形數據的更新, 波形RAM 設計成為雙口RAM。

4 性能與誤差分析

4. 1 測試結果

輸出波形如圖6 所示。本系統測試所用到的儀器為:

示波器 T ekt ronix 公司 型號: T DS1012

計數器 創瑞科技有限公司 型號: SPF40

圖6 輸出波形圖

4. 2 頻率測量

通過設定預定值, 用計數器測量出實際值, 基于此數據計算出誤差如下表( 只選取10 組數據) 。

由表1 可看出, 1 ~ 100 Hz 區間誤差較為明顯,1 kHz~ 1 MHz區間輸出頻率較為穩定( 該表為測試正弦波數據) 。

表1 頻率數據表

4. 3 誤差與雜散分析

除了工作環境與電源噪聲等問題是影響到頻譜純凈度的因素外, 還有以下主要原因:

( 1) 相位截斷產生雜散信號。硬件上無法滿足20 位的數據儲存, 設計中均采用了高位截斷的方法, 只取用累加器輸出的高幾位用于查表, 低位舍去。必然會造成誤差從而影響最終的輸出信號頻譜。正弦信號上引入了余弦分量, 造成時域上的疊加, 必然表現為頻域上的雜散。

( 2) D/ A 轉換器非線性引起的雜散分量。理想DAC 對DDS 的影響只表現在對信號頻譜的幅度和相位產生改變, 輸出上體現出滾降特性, 并不引入其它的頻率成分, 而非理想的DAC 的非線性、瞬間毛刺等非理想的轉換特性在輸出頻譜中產生了雜散。

( 3) 幅度量化產生的雜散。正弦查表內存儲的波形碼事一個模擬信號被均勻量化后的值。存儲器的容量有限, 不可能以無限二進制數來記錄正弦值, 因此出現幅度量化誤差。

減小DDS 輸出電壓中的雜散及噪聲的方法, 除了選用性能優良、工藝精湛的D/ A 轉換器, 提高位數與幅度量化字長外, 還可以通過設計良好的低通濾波器, 以濾除各種雜散及帶外噪聲, 也可選用DDS+ PLL 頻率合成技術, 以及數據壓縮法, 最高壓縮比可達128 1。另外可以在產生的相位字序列上加入高頻抖動( Dither) , 因為相位截位誤差成周期分布, 這將導致在某些頻率處產生較大的毛刺, 使DDS 產生的頻譜無雜波動態范圍減小。通過在相位上加入抖動, 能夠破壞相位誤差中較明顯的周期性分布, 從而使得毛刺的幅值得到減小, 增大了輸出正余弦波的無雜波動態范圍 。

還可以采用相位誤差反饋結構, 在SCMF( 相位累加器和正余弦函數生成器) 前加入一個二階FIR 濾波器( Finite Impulse Response, 有限沖擊響應) 來濾除輸出頻率附近的相位誤差。

5 結 語

任意波形發生器的設計是全國電子設計大賽中經典的選題之一, 任意波形發生器的設計不僅有廣泛的實踐應用空間, 并且對于電子科的學生動手能力的提高及學科知識的融會貫通同樣具有極大的指導價值。本文尋求功能強大、操作便捷、輸出參數穩定的設計效果, 并主要偏重基礎, 使之更符合教科書的典型教學條件, 并對相關參數進行測量, 分析原因。關于波形發生器的設計, 仍有許多可以設計擴展的功能, 雜散的削弱仍有較多的方法值得探究。

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603885 -

DDS

+關注

關注

21文章

634瀏覽量

152698 -

波形發生器

+關注

關注

3文章

293瀏覽量

31394

發布評論請先 登錄

相關推薦

基于ROM的任意波形發生器(DDS)

【Z-turn Board試用體驗】+基于FPGA和DDS技術的三相正弦波的發生器設計

任意波形發生器_DDS任意波形發生器的設計

基于Verilog實現的DDS任意波形發生器

利用FPGA實現DDS技術實際任意波形發生器

利用FPGA實現DDS技術實際任意波形發生器

評論