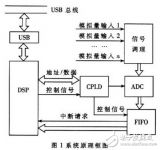

隨著可編程邏輯器件的不斷進步和發展,FPGA在嵌入式系統中發揮著越來越重要的作用。本文介紹的在電能質量監測系統中信號采集模塊控制器的IP核,是采用硬件描述語言來實現的。首先它是以ADS8364芯片為控制對象,結合實際電路,將6通道同步采樣的16位數據存儲到FIFO控制器。當FIFO控制器存儲一個周期的數據后,產生一個中斷信號,由PowerPC對其進行高速讀取。這樣能夠減輕CPU的負擔,不需要頻繁地對6通道的采樣數據進行讀取,節省了CPU運算資源。

1 ADS8364芯片的原理與具體應用

A/D轉換芯片ADS8364是TI公司推出的專為高速同步數據采集系統設計的高速度、低功耗、6通道(三相電壓、三相電流)同步采樣的16位A/D轉換芯片。采用模擬和數字分別供電,在模擬輸入端,有模擬參考電壓輸入、輸出引腳和信號六通道正反相輸入引腳;在數字端,主要包括控制ADS8364的讀/寫、復位、片選引腳和轉換結果輸出總線。

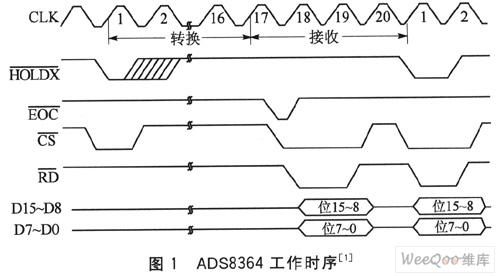

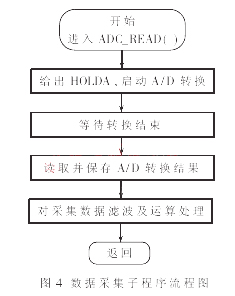

ADS8364芯片的轉換過程為:當ADS8364的HOLDX保持至少20 ns的低電平時,轉換開始。當轉換結果被存入輸出寄存器后,引腳EOC的輸出將保持半個時鐘周期的低電平,以提示數據分析處理器進行轉換結果的接收,處理器通過置RD和CS為低電平可使數據通過并行輸出總線讀出。在轉換數據的接收過程中,ADS8364芯片各引腳工作的時序達到協調一致,才能保證監測設備良好工作,具體時序安排如圖1所示。

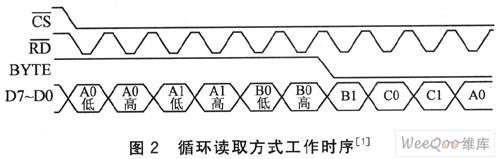

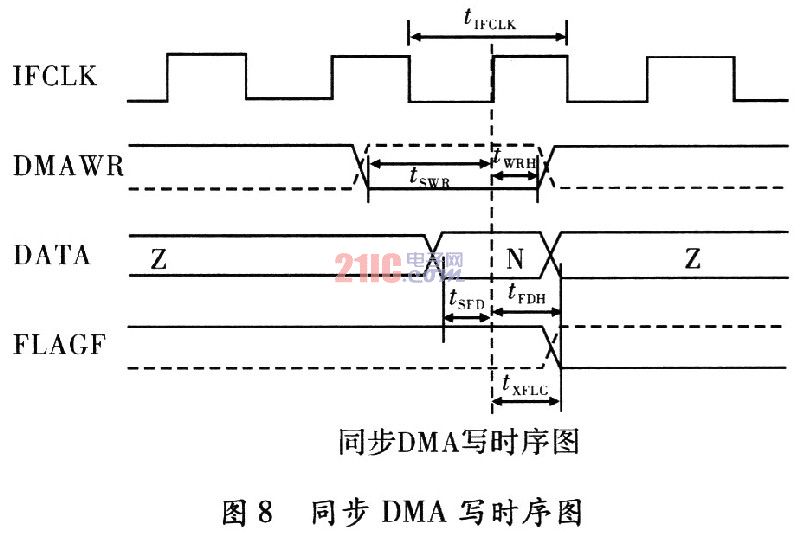

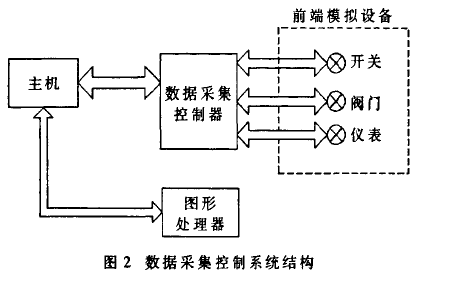

ADS8364芯片的數據輸出方式分別由BYTE、ADD與地址線A2、A1、A0組合控制,轉換結果的讀取方式由電能質量監測系統中采用的數據分析處理器決定,一般可取直接讀取、循環讀取和FIFO方式的任何一種。根據BYTE為0或者為1可確定每次讀取時得到的數據位數,根據ADD為0或者為1可確定第一次讀取的是通道地址信息還是通道A/D轉換結果。在實際應用中,我們結合了ADS8364模數轉換器中的6個16位ADC可以成對同步工作的能力,3 個保持信號(HOLDA、HOLDB、HOLDC)可以同時被選通,其轉換結果將保存在6個寄存器中。對于每一個讀操作,ADS8364均輸出16位數據,最高位為符號位。根據圖2所示的ADS8364循環讀取方式工作時序,需設置BYTE為0,A2、A1、A0分別為1、1、0。

2.3 A/D轉換芯片控制模塊及頂層文件的設計

控制器模塊的設計:

①根據ADS8364的工作原理:HOLDX保持至少20ns的低電平,轉換開始,所以控制器需根據時序要求產生HOLD周期信號。

②轉換結束后根據EOC的響應狀態,需要置RD和CS為低電平,使數據通過并行輸出總線讀出。下面是根據EOC的狀態改變RD值的Verilog描述:

根據圖1的工作時序和圖2的循環讀取方式以及對數據采集頻率(12.8 kHz)的要求,對芯片相應的引腳進行控制,并和FIFO進行連接使采集的數據能夠按照循環方式寫入FIFO。采用Verilog硬件描述語言實現上述功能,并建立頂層文件正確連接各個功能模塊。

頂層文件的Verilog描述如下:

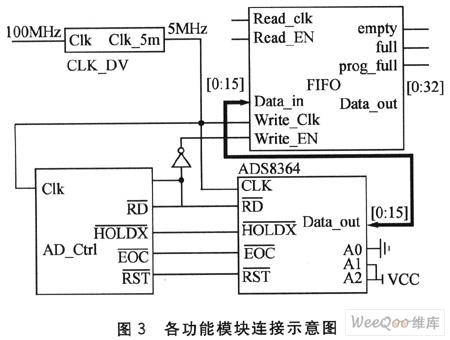

如圖3所示,時鐘分頻部分的輸出與FIFO的數據寫入時鐘、AD_Ctrl的時鐘和A/D轉換芯片的時鐘相連接。AD_Ctrl部分主要對ADS8364 芯片進行控制,其中輸出RD也連接到FIFO的寫使能端,對FIFO的數據寫入進行控制。FIFO的讀時鐘接到系統時鐘,讀使能由CPU控制。當FIFO 寫入一個周期的數據后,由prog_full產生中斷信號,CPU響應并對FIFO進行讀取。

2.4 仿 真

對頂層文件進行綜合,并在Mode-lsim中對其進行仿真。數據采集控制器的仿真結果如圖4所示。當holdx_n為低電平時,啟動A/D轉換,完成后根據EOC_n的低電平信號產生6個RD_n的低電平信號,循環讀取數據。當FIFO存儲了一個周期的數據后,CPU置FIFO的讀使能端口為高電平,對 FIFO中的數據進行高速讀取。若FIFO中數據為空,empty為高電平。

3 使用Xilinx嵌入式開發工具EDK設計IP核

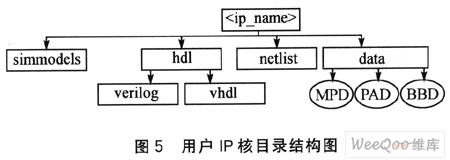

嵌入式開發軟件EDK為設計人員提供了自動化設計向導—— Base System Builder(BSB),可以指引工程師快速完成整個設計過程。使用BSB創建工程,在創建完成之后使用EDK自帶的CIP(Create and Import Peripheral Wizard)添加用戶自定義IP核,生成的用戶IP核保存在EDK工程目錄下的pcore文件夾。用戶IP核目錄如圖5所示。

其中文件夾data用于存放用戶IP的配置文件,如.prj文件、.mpd文件和.pao文件等;文件夾hdl用于存放用戶IP的HDL代碼,即.v或者.vhd文件;而devl(simmodels)文件夾中的工程可以使用戶在ISE平臺對工程進行設計、綜合與仿真,如果設計需要加入網表,可以放在 netlist文件夾。CIP在建立用戶IP核時,使用了一種專用接口規范(IPIF)。IPIF是一個驗證并優化的高度參數化的定制接口,它提供了一個簡化的總線協議IPIC(IP Intercon-nect),操作這個總線與直接操作PLB及OPB這些總線相比要簡單很多。通過IPIF模塊,對其進行參數化定制來滿足設計需求,將降低設計與測試的工作量。

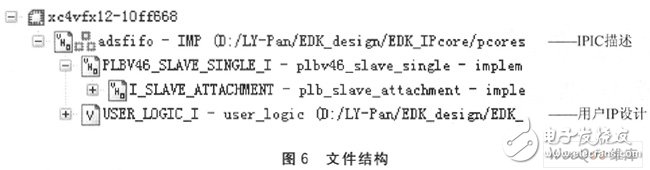

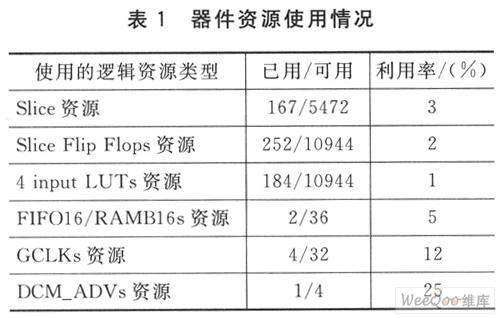

將設計的Verilog文件復制到IP核目錄下相對應的hdl文件夾下,啟動ISE開發平臺并打開devl文件夾中的工程文件,在Sources for Implementation中顯示的結構如圖6所示。圖中,adsfifo.vhd是IPIC的描述文件,user-logic.v(或 user_logic.vhd)可以實現用戶IP核功能設計。需要在adsfifo.vhd中加入必要的端口聲明與邏輯設計,使PLB控制器與用戶IP設計端口進行相應的連接。設計完成后在ISE平臺中對該IP核進行綜合并仿真。綜合后查看FPGA器件的資源使用情況,如表1所列。

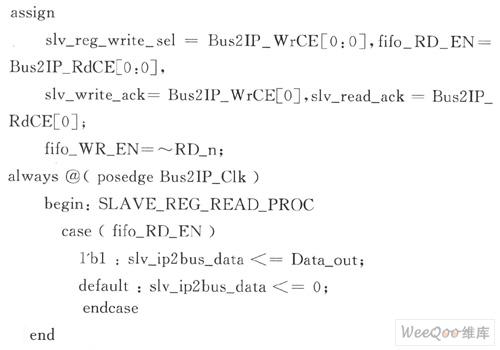

根據需要修改user_logic.v(或user—logic.vhd),向其中添加端口聲明與邏輯設計:

注意:在綜合后需要使用EDK中的CIP工具重新導入用戶IP核,在導入的過程中要指定MPD配置文件和XST project file(*.pfj)文件,這樣CIP可以自動加入相關聯的.v或.vhd文件。導入完成后在EDK的IPCatalog的Project Local pcores分類中可以看到用戶IP核,可以向EDK工程中加入該IP核,并設置其Bus Inter-face、Port和Addresses后生成位流文件,下載到開發板進行調試。

4 總 結

利用FPGA和ADS8364設計的數據采集的IP核,其接口簡單,采集精度高,可同時采集多路信號,而且能減輕FPGA嵌入式系統中CPU的負擔,節省CPU的運算資源。經過仿真和下載到開發板驗證,該設計能滿足高速交變電壓信號采集的高精度和高實時性的要求。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603017 -

控制器

+關注

關注

112文章

16334瀏覽量

177815 -

IP

+關注

關注

5文章

1703瀏覽量

149509

發布評論請先 登錄

相關推薦

調試ADS8364采集電壓數據DSP得到的數據不對

基于FPGA的數據采集控制器IP核的設計方案和實現方法研究

ads8364中文資料

ADS8364的原理及應用

并行模數轉換器ADS8364與TMS320F2812的接口設

基于ADS8364和ARM7單片機的導航姿態角采集系統設計

基于ADS8364的數據采集系統設計

基于ADS8364的數據采集系統設計

USB的高精度多通道數據采集卡設計

六通道同步采樣AD芯片ADS8364在數據采集中的應用

DSP與ADS8364的高速數據采集處理系統設計分析

如何使用FPGA進行仿真系統數據采集控制器IP核設計的資料概述

利用FPGA和ADS8364實現數據采集控制器IP核設計

利用FPGA和ADS8364實現數據采集控制器IP核設計

評論