引言

隨著網絡技術的不斷發展,數據交換、數據傳輸流量越來越大。尤其像雷達,氣象、航天等領域,不僅數據運算率巨大,計算處理復雜,而且需要實時高速遠程傳輸,需要長期穩定有效的信號加以支持,以便能夠獲得更加精準的數據收發信息,更好的為工程項目服務。傳統的并行傳輸方式由于走線多、信號間串擾大等缺陷,無法突破自身的速度瓶頸。而串行傳輸擁有更高的傳輸速率但只需要少量的信號線,降低了板開發成本和復雜度,滿足高頻率遠距離的數據通信需求,被廣泛應用到各種高速數據通信系統設計中。

目前,高速串行接口取代并行拓撲結構已經是大勢所趨。當今很多公用互連標準(如USB,PCI-Express)都是基于串行連接來實現高速傳輸的。相比于并行總線,串行連接的物理緊密度和鏈路韌性具有很多優勢。因此,很多傳輸領域都轉向了串行傳輸,如筆記本電腦顯示互連、高速背板互連和存儲器內部互連。該系統涉及到的技術主要包括:光纖傳輸、PCIE(PCI-Express)傳輸和DDR緩存技術,以及這幾種技術在FPGA中融合為一個完整的串行傳輸鏈路,并實現了在兩臺服務器之間的高速數據傳輸測試,這對于實際工程應用具有重要的現實意義。

1 系統結構

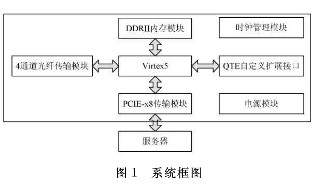

高速串行傳輸系統作為數據采集、傳輸、存儲中的一部分,對傳輸性能指標有著嚴格的要求。該系統要完成光信號到PCI-Express接口信號的相互轉換,并在轉換過程中完成數據的高速傳輸。信號一般可達4.25Gb/s,處理如此高的數據對硬件設計提出了很大的挑戰。其中所包含的硬件有:高速光電轉換電路,FPGA數據處理電路、DDRⅡ數據緩存電路、時鐘管理電路、PCIE傳輸模塊電路、電源模塊電路、自定義擴展接口電路。系統框圖如圖1所示。

技術要求主要有以下幾點:首先,傳輸卡中的4個光纖通道,每通道要達到2 Gb/s以上。其次,PCIE傳輸速率不小于6 Gb/s,支持DMA傳輸。再有,光纖和PCI-E傳輸誤碼率要小于1×10-10,連續傳輸相對穩定。

圖1中各個模塊的功能如下:Virtex5作為傳輸卡的核心,用來實現數據從光纖接口到PCIE接口的高速轉換。光纖傳輸模塊的作用是將內部數據經過編碼后,通過光纜傳輸給接收系統,以及接收外來光數據,并將光數據傳送給FPGA處理電路DDR緩存模塊的作用,就是將傳輸過程中的高速數據,進行緩存,以保持數據的完整性。PCI-Express傳輸模塊的作用,就是與PC之間實現PCI-Express傳輸協議,與PC實現串行數據傳輸,同時與外部擴展接口,DDR緩存,光纖傳輸模塊實現內部并行數據的交換。QTE自定義接口模塊的作用,就是進行外部功能擴展。比如,可以擴展高速數據采集板卡、存儲硬盤卡、圖像采集卡等。時鐘管理模塊的作用,是給光纖傳輸模塊提供參考時鐘。時鐘頻率由FPGA的時鐘控制模塊控制。根據光模塊的性能,給出指定的時鐘。PCI-Express的參考時鐘,是通過芯片從PC主板上提取的。電源管理模塊的作用,是給整個系統提供各種不同的電壓。

2 系統模塊設計與實現

為了實現所要求的系統配置,更好地發揮各模塊自身及相互之間的作用,必須對模塊間進行系統的協議分析。該系統的數據傳輸是雙向的,既可以傳輸數據,也可以接收數據。它主要由電源管理模塊,時鐘管理模塊,PCI-Express傳輸模塊,DDR緩存模塊,光纖傳輸模塊和外部擴展接口組成。其中,時鐘控制模塊和AURORA發送模塊、Aurora接收模塊是整個設計的重點。

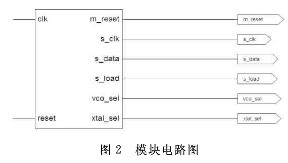

2.1 時鐘控制模塊 時鐘控制模塊主要用來控制FPGA外圍的時鐘芯片ICS8442來產生所需要的高信噪比、低抖動的差分時鐘。其模塊電路如圖2所示:輸出其中的信號用來完成對ICS8442的編程,使其能夠產生所需要的時鐘信號。

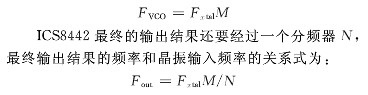

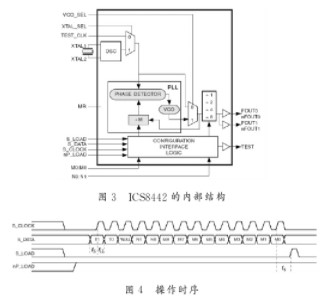

ICS8442的性能參數如下:輸出信號頻率范圍為31.25~700 MHz;晶振頻率范圍為10~25 MHz;VCO頻率范圍為250~700 MHz;ICS8442是LVDS邏輯電平,具有極低的相位噪聲,這種特性使它非常適合用來為吉比特以太網或同步光纖網提供時鐘信號。 ICS8442的內部結構圖3所示。ICS8442內部有一個完整的PLL鎖相環,其VCO的輸出頻率范圍在250~700MHz之間,倍頻系數是由M決定的,M的取值范圍在10~28之間。VCO的輸出頻率為:

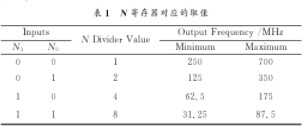

其中:N是一個2位的寄存器,其對應的取值如表1所示。

對ICS8442時鐘芯片的操作主要是對寄存器M,N的寫操作。ICS8442支持并行寫操作和串行寫操作,根據硬件電路的設計,程序采用串行的寫操作時序。當ICS8442的nP_LOAD置為高電平和S_LOAD置為低電平時,芯片實現串行操作。

當S_LOAD置為低且nP_LOAD置為高之后,數據在S_CLOCK的上升沿處寄存在緩沖器中,在S_LOAD的下降沿處將數據鎖存到寄存器M,N中。

由于AURORA光纖通信的輸出時鐘頻率設定的是125 MHz,結合硬件電路的設計,硬件晶振的頻率為20 MHz,因此選擇M值為000011001(25),N的值為10(4),故時鐘芯片的時鐘輸出頻率為:

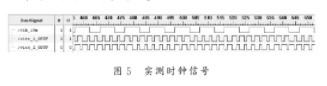

時鐘控制模塊的實測時鐘信號如圖5所示。

圖5是用Chipscope在線邏輯分析儀得到的波形,由于Chipscope在線邏輯分析儀的觸發時鐘是100 MHz,因此在抓取125 MHz的時鐘信號時,在圖上顯示的時鐘信號占空比不定,若將時鐘芯片產生的時鐘頻率降低,則此現象消失。

2.2 AURORA發送模塊

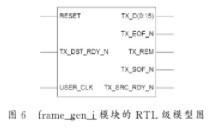

在生成AURORA IP CORE時,同時生成了一個基于AURORA協議的例示程序。因此,要實現基于AURORA協議的光纖通信,在發送端只需要在frame_gen_i模塊將要發送的數據打包,然后通過AURORA模塊發送出去。因此該模塊著重介紹如何將上一級傳送過來的數據進行打包壓縮,形成適合AURORA協議的數據幀,通過AURORA協議發送到接收端。圖6為frame_gen_i模塊的RTL級模型圖。

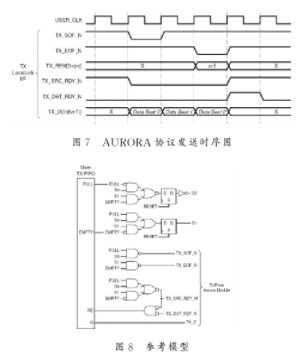

考慮到上一級傳輸數據速率可能會與AURORA傳輸的時鐘頻率不同,因此在發送端建立一個FIFO來做緩沖器。并且AURORA協議的發送時序圖如圖7所示。可以看出,TX_SOF_N為數據包幀的開始標志,TX_EOF_N為數據包幀的結束.標志,TX_REM[0:r(n)]記錄最后的傳輸數據的線程,TX_SRC_RDY_N為低代表數據有效,TX_DST_RDY_N為低代表準備好接受數據,TX_D[0:(8n-1)]是此模塊的輸出數據。以上信息是AURORA協議的發送時序,在使用FIFO做緩沖時也應該遵循這樣的協議。

發送端的FIFO模塊分別包括FIFO的復位信號、FIFO空、FIFO滿、以及讀/寫時鐘、使能和數據信號線。因此應該根據FIFO的標志位empty和full來產生AURORA的發送時序,參考模型如圖8所示:當RESET信號到來之時,首先將S0置為高電平,將S1置為低電平,同時根據FULL和EM-PTY的狀態確定接下來的S0和S1的狀態,進而根據以上邏輯關系得到TX_SOF_N,TX_EOF_N,TX_SRC_RDY_N等邏輯信號,并且根據數據X_DST_RDY_N和TX_SRC_RDY_N生成FIFO的讀使能。由以上邏輯可以看出,只有在FULL為1,EMPTY為0時,FIFO的讀使能才能被打開。TX_SOF_N為數據包的幀頭標志,TX_EOF_N為數據包的幀尾標志,TX_STC_RDY_N為低時代表數據有效,TX_DST_RDY_N為輸入信號,根據此輸入信號確定FIFO的讀寫時序。

對FIFO時序操作需要根據上述電路圖所產生。在上述電路圖中,有一個D觸發器,其RESET信號是復位信號,復位既是將觸發器輸出端口清零,即將S0置1,將S1置0。在之前的程序中誤將這里寫反,即RESET信號到來之后,將S0置0,S1置1。這樣導致的結果是在最開始輸入的一段數據丟失,之后的結果輸出正常。經過仿真分析之后檢查出問題并已改正。

2.3 AURORA接收模塊

同樣在AURORA協議模塊中,要實現對數據的接收,只需在frame_check模塊中對接收的代碼加以修改,增加自己所需要的內容,完成對數據的解碼提取,剔除冗余信息,并完成數據的緩存。[page]

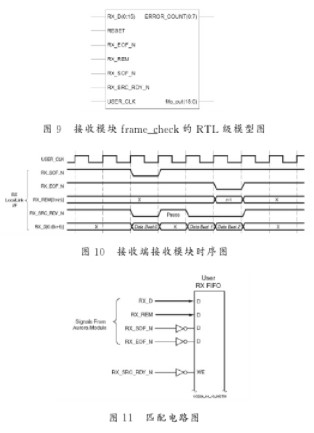

接收模塊frame_check的RTL級模型圖如圖9所示:其中,RX_D為接收端接收的緩存于FIFO的數據,REsET為復位信號,RX_EOF_N為數據包幀尾的標志,RX_SOF_N為數據包幀頭的標志,TX_SRC_RDY_N為低時代表數據有效,USER_CLK為系統時鐘。fifo_out為數據緩存的輸出,ERROR _COUNT為系統檢錯輸出結果。因此在接收端接收模塊的時序圖如圖10所示。根據該時序圖可以確定接收時序,同樣,在AURORA協議末端,由于與下一級系統的速率可能不匹配,因此需要在接收末端加上一個FIFO做緩存,同樣其電路圖如圖11所示:根據RX_SRC_RDY_N生成FIFO的寫使能信號,該發送模塊設計完畢。

3 測試分析

3.1 功能測試

在基本功能測試中,主要測試光纖模塊傳輸是否正確。由于光纖模塊共有A,B,C,D四個通道,對每個通道都要進行讀/寫測試。將通道A作為數據發送端,通道B作為數據接收端,應用光纖將A,B兩端進行聯通,然后將應用程序數據寫入A通道FIFO中,當FPGA接收到到數據后,將A通道數據通過光纖傳輸到通道B接收緩存中,然后通道B將數據發送到上位機,從而形成一個環路。比較發送和接受端的數據,可以驗證數據傳輸的正確性。同理可以將此方法應用于四個通道中的任意兩個作為發送端和接收端,從而驗證并測試傳輸功能。

3.2 性能測試

性能主要對其傳輸速度和傳輸誤碼率進行測試。就傳輸速度而言,主要由FPGA控制,在其內部設置了兩個初始值為0的計數器,在PCI-Express開始傳輸數據時,FPGA開始計數讀/寫數據包和發送數據包的個數,然后每隔一段時間將計數值寫入兩個計數寄存器中,并將原有值替換,為了精確速率,可以縮短計數時間,并多次測試取平均值,就可得到傳輸瞬時速度。經測試:PCI-Express接口的傳輸速度在600MB/ s,光纖傳輸在850 MB/s,滿足設計要求。對于誤碼率的測試,主要使用誤碼分析軟件對其誤碼性能進行測量,設計由上位機和PCI-Express接口,光纖通道組成數據傳輸環路,通過不同的指令和要求驗證傳輸正確性,當數據包大小在4 Kb,8 Kb,16 Kb,32 Kb,測試數據長度分別為1 000 Kb,1 000 000 Kb,100000 000 Kb時,錯誤率都為0 b,誤碼率滿足設計要求。

4 結語

該設計系統以Virtex-5為核心構建的平臺,對AURORA協議下串行傳輸系統進行了設計與實現。通過對核心問題的解決,將計算機與外部擴展很好的結合,達到信號傳輸的高速、穩定的目的。實驗證明,板卡設計的整體思路和核心方法的解決是完備的,并使得板卡的傳輸速率和穩定性的到了較大的提高。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603024 -

雷達

+關注

關注

50文章

2930瀏覽量

117467 -

電源模塊

+關注

關注

32文章

1701瀏覽量

92817

發布評論請先 登錄

相關推薦

RocketIO高速串行接口

基于Virtex-5 LXT助力串行背板接口設計

基于Virtex-5 LXT的串行背板接口設計

基于Virtex-5 LXT的串行背板接口設計

Xilinx Virtex-5 FXT FPGA開發方案

Virtex-5 Embedded Tri-Mode Eth

Opal Kelly推出基于Virtex-5的USB集成模塊

基于Virtex-5 FPGA的音視頻監視系統設計

基于Virtex-5的串行傳輸系統的實現

基于Virtex-5的3.125G串行傳輸系統的設計

基于賽靈思Virtex-5的音視頻監視系統設計的詳細分析

基于Virtex-5 RocketI0TM GTP收發器實現串行高速接口的開發應用

基于Virtex-5技術實現AURORA協議的串行傳輸系統的設計

基于Virtex-5技術實現AURORA協議的串行傳輸系統的設計

評論