零延遲指的是時鐘頻率合成器能夠提供與時鐘參考源邊沿對齊的輸出信號,其應(yīng)用包括許多同步系統(tǒng),如SONET和SDH網(wǎng)絡(luò)、高速網(wǎng)絡(luò)服務(wù)器、網(wǎng)絡(luò)線路卡以及用于W-CDMA和Wi-Fi的基帶定時等。

零延遲架構(gòu)

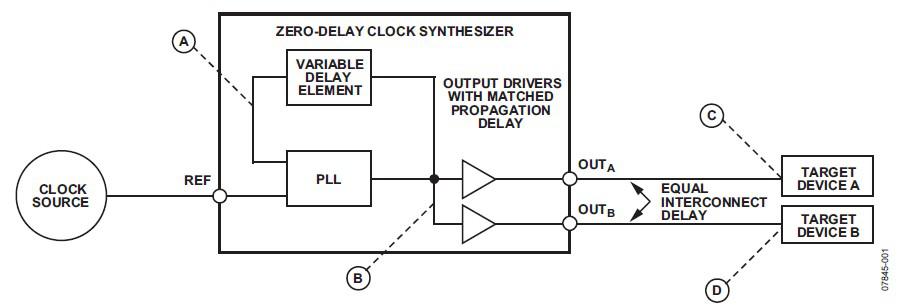

集成零延遲時鐘頻率合成器至少需要三個構(gòu)建模塊(見圖1)。第一個構(gòu)建模塊是鎖相環(huán)(PLL),它可以是常見的模擬類型或較新型的全數(shù)字設(shè)計。第二個構(gòu)建模塊是具有匹配傳播延遲的兩個(或更多)輸出驅(qū)動器。第三個構(gòu)建模塊是PLL反饋路徑中的可變延遲元件。此外,零延遲架構(gòu)要求從合成器輸出到關(guān)聯(lián)目標器件的互連延遲等同。等同的互連延遲是零延遲架構(gòu)的基本組成部分,沒有它,目標器件將無法實現(xiàn)時鐘沿對齊。

圖1. 通用零延遲頻率合成器

零延遲操作

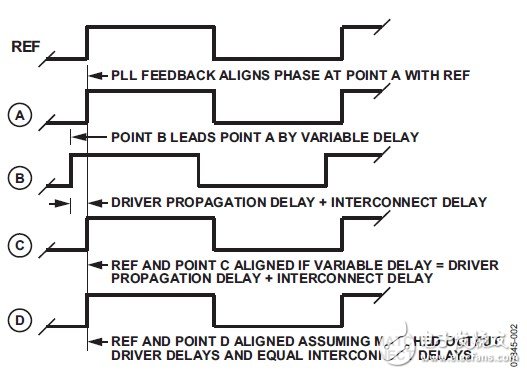

要了解零延遲操作,請參考圖2,它是圖1所示零延遲架構(gòu)的時序圖。注意,PLL的動作使得A點的時鐘沿與REF時鐘沿對齊。可變延遲元件位于PLL反饋路徑中,這意味著B點的時鐘沿比A點的時鐘沿提前一個可變延遲量。

圖2. 零延遲時序圖

將可變延遲設(shè)置為輸出驅(qū)動器傳播延遲與互連延遲之和,這樣C點的時鐘沿就與A點的時鐘沿重合,而A點的時鐘沿與REF時鐘沿重合,因此,REF與目標器件A的時鐘沿對齊。此外,由于輸出驅(qū)動器共享同一輸入信號,并且該信號在經(jīng)過各驅(qū)動器和各互連時均發(fā)生相同的延遲,因此REF時鐘沿不僅與目標器件A的時鐘沿對齊,而且與目標器件B的時鐘沿對齊。事實上,只要所有驅(qū)動器表現(xiàn)出相同的傳播延遲,并且所有互連具有相同的延遲,就可以將上述概念擴展到所需的許多輸出。

圖2中的時序圖顯示,PLL提供的頻率轉(zhuǎn)換比為1(即fREF = fOUT),這可以簡化說明,但并不是必需的。事實上,任何能夠提供整數(shù)(或整數(shù)倒數(shù))輸出/輸入頻率比的倍頻或分頻系數(shù)都是可以接受的。一般而言,輸入和輸出信號的頻率必須諧波相關(guān),時鐘沿對齊才有意義。

必須注意,"零延遲"的適用對象是相對時間,而不是絕對時間。圖2清楚地顯示,可變延遲元件導(dǎo)致B點的時鐘沿先于REF時鐘沿。顯然,在絕對時間中,時間無法倒流,B點的時鐘沿不可能先于REF時鐘沿。事實上,B點的絕對時鐘沿至少比REF時鐘沿落后一個完整的時鐘周期(減去可變延遲)。在實際的定時應(yīng)用中,時鐘沿只需要相對于參考時鐘對齊,因此使用"零延遲"這一術(shù)語完全妥當。

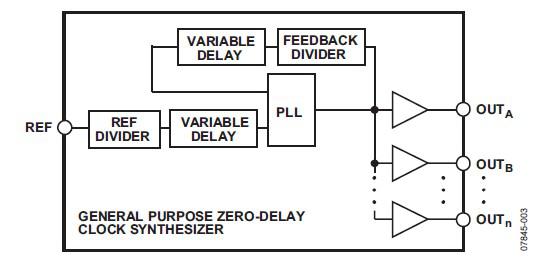

圖1用于說明零延遲架構(gòu)的概念是有益的,但要作為一種集成解決方案,它是有局限性的。更一般的解決方案是在PLL的REF和反饋路徑中各包括一個可編程分頻器(見圖3)。利用REF和反饋分頻器,單一器件就能設(shè)置不同的輸入/輸出頻率比,從而滿足許多應(yīng)用的需求。然而,對于零延遲應(yīng)用,只有諧波相關(guān)的輸入/輸出頻率比才是有意義的。注意,REF路徑中出現(xiàn)了第二個可變延遲單元,其主要作用是對REF分頻器造成的延遲進行邊沿時序補償。

圖3. 通用零延遲頻率合成器

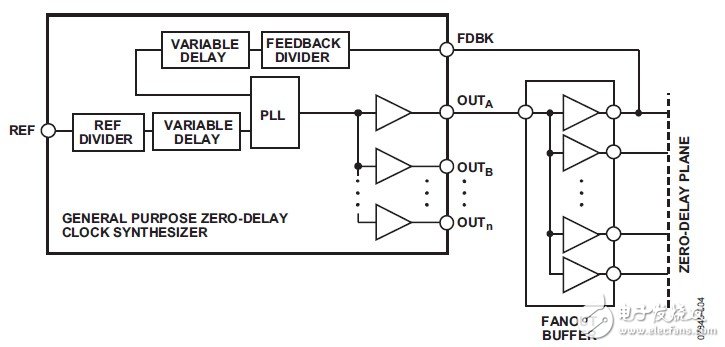

通用零延遲架構(gòu)的進一步擴展是從外部訪問PLL反饋路徑,這將使得零延遲架構(gòu)能夠支持外部扇出緩沖器,如圖4所示。

圖4. 外部零延遲架構(gòu)

集成解決方案

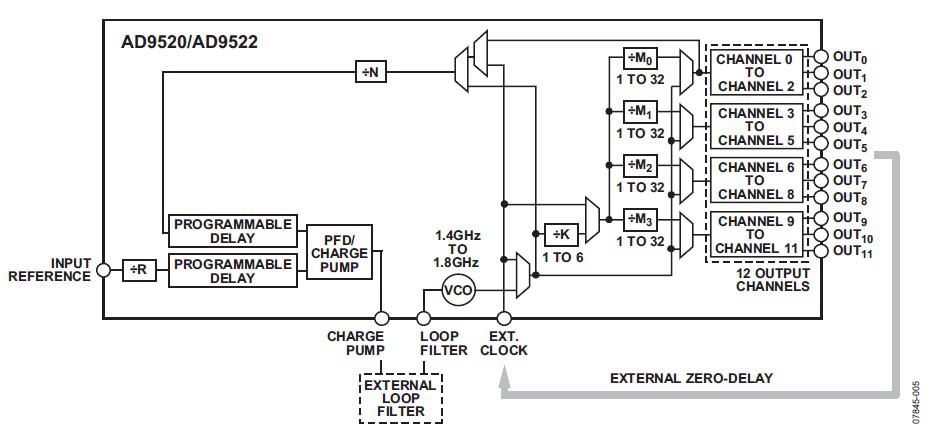

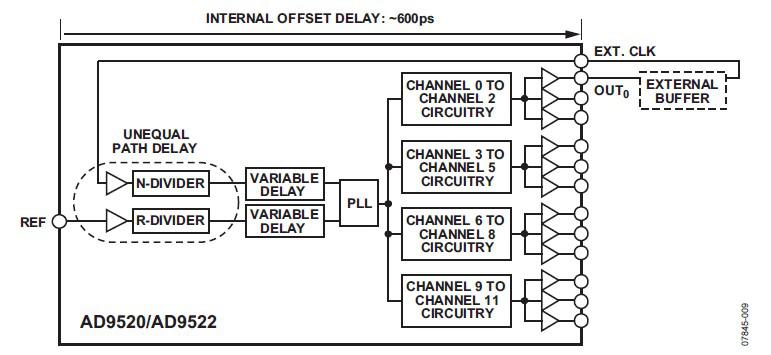

AD9520和AD9522是通用時鐘頻率合成器,能夠為許多應(yīng)用提供集成零延遲解決方案。兩款器件的唯一區(qū)別是AD9520采用LVPECL輸出驅(qū)動器,AD9522則采用LVDS驅(qū)動器。任一款器件的輸出驅(qū)動器都可以編程為CMOS.圖5所示為AD9520/AD9522的功能框圖。

圖5. AD9520/AD9522功能框圖

該器件具有一個串行編程接口,支持廣泛的時鐘合成解決方案,靈活的架構(gòu)同時支持內(nèi)部和外部零延遲應(yīng)用。AD9520/AD9522的PLL部分由PFD/電荷泵、外部環(huán)路濾波器和集成VCO(帶可選K分頻器)組成。R分頻器為參考分頻器,N分頻器為反饋分頻器。每個分頻器后置一個可編程延遲單元。兩個可編程延遲單元均以大約120 ps的步進提供大約1100 ps的延遲調(diào)整。AD9520/AD9522具有12個輸出驅(qū)動器(通道0至通道11),分為4組,每組包括三個驅(qū)動器。此外,各組通道都能訪問可選的通道分頻器(M0至M3)。

通道分頻器提供額外的分頻功能,增強了器件在頻率合成應(yīng)用中的靈活性。除分頻外,通道分頻器還提供邊沿時序

粗調(diào)功能。各通道分頻器的輸出邊沿時序是可編程的,編程步進為ΔT(最多32步),其中ΔT = 1/fCLK,fCLK為通道分頻器的輸入頻率。

通道分頻器雖然增強了AD9520/AD9522的頻率合成能力,但也使涉及零延遲的應(yīng)用更加復(fù)雜,原因是零延遲架構(gòu)要求從PLL輸出端到各輸出驅(qū)動器輸入端的延遲等同,通道分頻器的存在破壞了這種延遲等同性,除非用戶采取適當?shù)拇胧>唧w而言,對于任何用來執(zhí)行零延遲功能的通道必須同等對待。也就是說,如果一組零延遲輸出采用通道分頻器,則其他零延遲輸出也必須采用通道分頻器。此外,必須對零延遲輸出相關(guān)的所有通道分頻器應(yīng)用相同的分頻和延遲值。這些措施可以確保所有通道從PLL輸出端到各通道驅(qū)動器輸出端的延遲相同(至少通道之間的內(nèi)部延遲匹配)。

時序誤差:偏斜和偏移

理論上,如果外部互連延遲完全一致,則出現(xiàn)在零延遲平面的時鐘信號與REF信號邊沿對齊。然而,實際應(yīng)用中通常存在兩類時序誤差。一類是時序偏斜,它是指邊沿對齊存在細微的偏差,這些偏差隨機分布于多個時鐘信號中。另一類是時序偏移,它是指邊沿對齊的恒定偏移(相對于REF信號),對所有輸出時鐘信號都相同。

時序偏斜的一個誤差源是器件本身。器件各輸出通道的傳播延遲存在細微的差異,這是內(nèi)部時序偏斜產(chǎn)生的原因。雖然AD9520/AD9522的設(shè)計人員力圖將時序偏斜降至最小,但仍存在一些無法避免的偏差。時序偏斜的另一個是外部互連的物理或電氣長度存在細微的誤差。

在這兩個時序偏斜源中,內(nèi)部偏斜源相比于外部偏斜源通常可以忽略不計。當使用AD9520 LVPECL輸出時,情況更是如此,所有通道間的偏斜只有大約50 ps.即便使用AD9520/AD9522 CMOS或AD9522 LVDS輸出,所有通道間的偏斜分別也只有大約300 ps或200 ps.然而,如果用

戶努力通過設(shè)計消除外部偏斜,那么內(nèi)部偏斜就可能成為主要的偏斜源。應(yīng)當注意,在實際應(yīng)用中,一定量的時序偏斜是不可避免的,設(shè)計人員必須確定特定應(yīng)用的最大容許時序偏斜,然后據(jù)此進行設(shè)計。

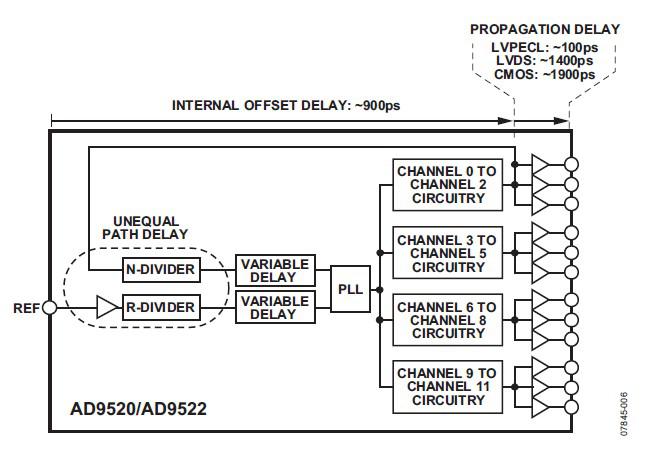

另一類時序誤差,即時序偏移,在AD9520/AD9522的內(nèi)部和外部零延遲架構(gòu)中具有不同的表現(xiàn)。對于內(nèi)部架構(gòu),需要考慮兩點(見圖6)。第一,輸出驅(qū)動器位于PLL反饋路徑外部,因此其傳播延遲表現(xiàn)為相對于REF信號的時序偏移。對于AD9520 LVPECL驅(qū)動器,該偏移量約為100 ps,AD9522 LVDS驅(qū)動器約為1400 ps,AD9520/AD9522 CMOS驅(qū)動器約為1900 ps.第二點考慮涉及到REF與反饋驅(qū)動器路徑之間的固有延遲不匹配,原因是N分頻器與R分頻器存在根本上的區(qū)別,導(dǎo)致延遲不匹配。此外,REF路徑包括一個時鐘接收器級,因此REF路徑的延遲比反饋路徑多出大約900 ps(假設(shè)可變延遲單元被旁路或具有相同的延遲值),這意味著LVPECL、LVDS和CMOS輸出的總不可調(diào)整偏移分別為1000 ps、2300 ps和2800 ps.

圖6. AD9520/AD9522內(nèi)部零延遲時序偏移誤差

通過旁路REF路徑中的可變延遲單元,并且使能反饋路徑中的可變延遲單元,可以減小該固有偏移。反饋路徑中的可變延遲單元提供1100 ps的調(diào)整范圍,因此全部1000 ps的固有偏移(使用LVPECL輸出時)都能得以消除。然而,當使用LVDS或CMOS輸出時,偏移僅可減小到大約1200 ps或1700 ps(固有偏移超出最大調(diào)整范圍的量)。任何情況下,設(shè)計人員必須確保殘余時序偏移不超過特定應(yīng)用的最大容許限值。

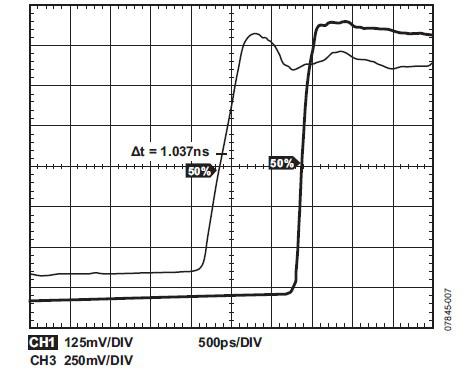

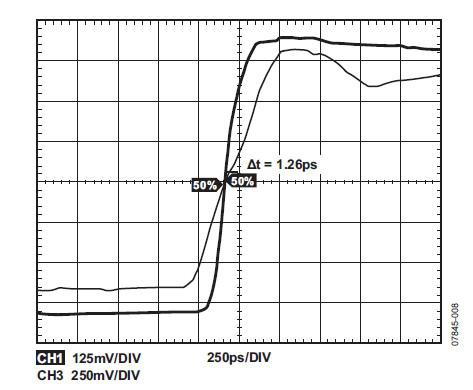

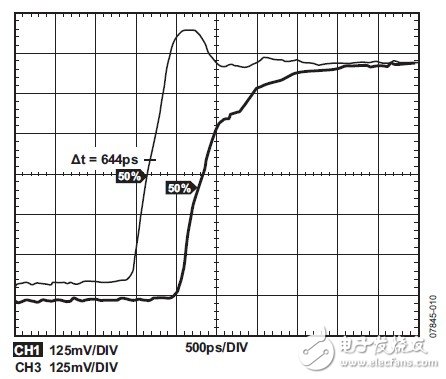

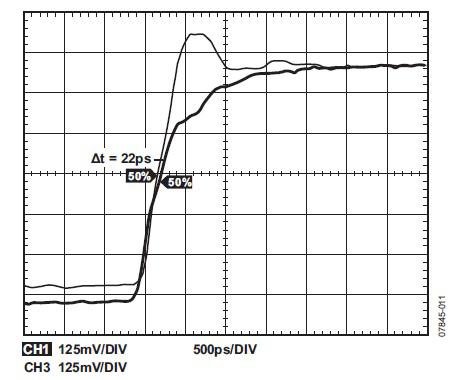

圖7和圖8所示為使用內(nèi)部零延遲架構(gòu)的實際時域測量結(jié)果。這些圖證明,使用AD9520 LVPECL輸出時,時序偏移幾乎被完全消除。測量使用匹配的探針進行,探針直接連接到器件的REF輸入和OUT1引腳。

圖7. 內(nèi)部零延遲固有偏移時序誤差(AD9520)

圖8. 內(nèi)部零延遲調(diào)整后的偏移時序(AD9520)

使用外部零延遲架構(gòu)時,驅(qū)動器(及任何外部緩沖器)包括在PLL的反饋路徑中,因此輸出驅(qū)動器的傳播延遲對偏移時序誤差無影響(見圖9)。PLL能夠有效吸收OUT0緩沖器(任選)的傳播延遲和經(jīng)過外部電路的延遲。然而,像內(nèi)部零延遲架構(gòu)一樣,REF與反饋驅(qū)動器路徑之間仍然存在固有的延遲不匹配,此外,對于外部架構(gòu),外部時鐘輸入需要一個時鐘接收器(顯示于N分頻器的輸入端)。整體偏移延遲為600 ps,比內(nèi)部架構(gòu)少300 ps,原因是外部時鐘輸入接收器具有額外的延遲。

圖9. AD9520/AD9522外部零延遲時序偏移誤差

由于固有偏移時序誤差僅為600 ps,因此可以將反饋路徑的可變延遲設(shè)置得比REF路徑的可變延遲大600 ps,從而消除誤差。當然,可變延遲單元的粒度為120 ps,這意味著仍可能有最多60 ps的殘余偏移。因此,設(shè)計人員必須確保最多60 ps的殘余時序偏移不超過特定應(yīng)用的最大容許限值。

圖10和圖11所示為使用外部零延遲架構(gòu)的實際時域測量結(jié)果,證明時序偏移誤差幾乎被完全消除。測量使用匹配的探針進行,探針直接連接到器件的REF輸入和外部時鐘引腳,OUT0反饋到外部時鐘輸入(類似于圖9)。

圖10. 外部零延遲固有偏移時序誤差(AD9520)

圖11. 外部零延遲調(diào)整后的偏移時序(AD9520)

涉及外部零延遲的考慮

在要求外部零延遲架構(gòu)的應(yīng)用中,務(wù)必避免引入過大的外部延遲以及將無用信號耦合到PLL反饋路徑。外部延遲可能導(dǎo)致PLL環(huán)路不穩(wěn)定,進入PLL反饋路徑的無用信號則可能破壞輸出時鐘信號。

注意,外部信號路徑中出現(xiàn)的任何延遲都會成為PLL反饋環(huán)路的一部分。如果PLL環(huán)路帶寬太寬,外部路徑的額外延遲可能會使環(huán)路不穩(wěn)定。用戶應(yīng)選擇外部環(huán)路濾波器,使得環(huán)路帶寬能夠支持額外的延遲,同時仍能確保環(huán)路穩(wěn)定。

外部零延遲架構(gòu)的PLL反饋路徑中包括外部電路,意外進入反饋路徑的無用信號可能會帶來嚴重問題,原因是進入PLL反饋路徑的任何信號都會被PLL放大。因此,即使非常小的信號,也可能變大到輸出端無法接受的程度。適當?shù)挠∷㈦娐钒宀季趾推帘渭夹g(shù)是防止無用信號侵入的最佳防護手段。

-

pll

+關(guān)注

關(guān)注

6文章

776瀏覽量

135139 -

時鐘

+關(guān)注

關(guān)注

10文章

1733瀏覽量

131458

發(fā)布評論請先 登錄

相關(guān)推薦

Σ-Δ調(diào)制頻率合成器【轉(zhuǎn)】

基于DDS的頻率合成器設(shè)計介紹

如何利用FPGA設(shè)計PLL頻率合成器?

AD9850 DDS 頻率合成器的原理及應(yīng)用

ΣΔ技術(shù)在鎖相環(huán)頻率合成器中的應(yīng)用

頻率合成器,頻率合成器原理及作用是什么?

間接式頻率合成器(IS)的定義和原理是什么?

單環(huán)鎖相頻率合成器,單環(huán)鎖相頻率合成器是什么意思

集成鎖相環(huán)頻率合成器,什么是集成鎖相環(huán)頻率合成器

射頻鎖相頻率合成器的設(shè)計與仿真

pll頻率合成器工作原理與pll頻率合成器的原理圖解釋

零延遲時鐘頻率合成器技術(shù)應(yīng)用分解

零延遲時鐘頻率合成器技術(shù)應(yīng)用分解

評論