1 概述

1588是IEEE規(guī)范定義的網(wǎng)絡(luò)實(shí)時(shí)同步標(biāo)準(zhǔn)。它提供一種通過(guò)網(wǎng)絡(luò)信息交互以獲得精準(zhǔn)時(shí)鐘信息的標(biāo)準(zhǔn)。和在廣域網(wǎng)上的NTP協(xié)議比較,1588最新標(biāo)準(zhǔn)提供高于納秒級(jí)別的時(shí)鐘精度,可以用來(lái)滿足要求在一個(gè)相對(duì)小的空間范圍內(nèi)對(duì)時(shí)鐘同步有嚴(yán)格要求的應(yīng)用場(chǎng)景,例如基站同步,音視頻網(wǎng)橋(AVB),工業(yè)控制,產(chǎn)線控制,軍事應(yīng)用等。

KeyStone架構(gòu)是TI推出的高性能多核架構(gòu),該架構(gòu)目前已演進(jìn)了兩代——KeyStone1 和KeyStone2。基于KeyStone架構(gòu),TI推出多款針對(duì)基站和網(wǎng)絡(luò)應(yīng)用的多核芯片。

KeyStone1家族基于40nm工藝,包括如下器件型號(hào):

TCI6616

TCI6618

TCI6614 和TCI6612

TMS320C6678、TMS320C6674、TMS320C6672 等

KeyStone2家族基于28nm工藝,包括如下器件型號(hào):

TCI6636K2H

TCI6634K2K

TCI6638K2K

TCI6630K2L

本文首先介紹IEEE1588的基本原理,然后以常見(jiàn)的基于PHY的IEEE1588實(shí)現(xiàn)方案為參考,介紹KeyStone架構(gòu)上支持IEEE1588的硬件功能。同時(shí),本文總結(jié)了在KeyStone1芯片上實(shí)現(xiàn)IEEE1588方案需要注意的實(shí)現(xiàn)細(xì)節(jié),并對(duì)KeyStone2芯片的1588方案做初步介紹。

2 IEEE1588時(shí)鐘同步原理

IEEE1588使用精準(zhǔn)時(shí)間協(xié)議PTP(Precision Timing Protocol),通過(guò)端到端的報(bào)文交互獲得時(shí)鐘參考信息,矯正本地時(shí)鐘頻率和相位。1588協(xié)議基于兩個(gè)假設(shè)條件:第一,在時(shí)鐘源設(shè)備和受時(shí)鐘設(shè)備之間,網(wǎng)絡(luò)報(bào)文傳輸時(shí)間是對(duì)稱的。也就是說(shuō)一個(gè)報(bào)文從時(shí)鐘源設(shè)備到受時(shí)鐘設(shè)備的傳輸時(shí)間等于報(bào)文從受時(shí)鐘設(shè)備到時(shí)鐘源設(shè)備的傳輸時(shí)間相同;第二,在PTP報(bào)文交換過(guò)程當(dāng)中,本地時(shí)鐘的漂移可以忽略不計(jì)。

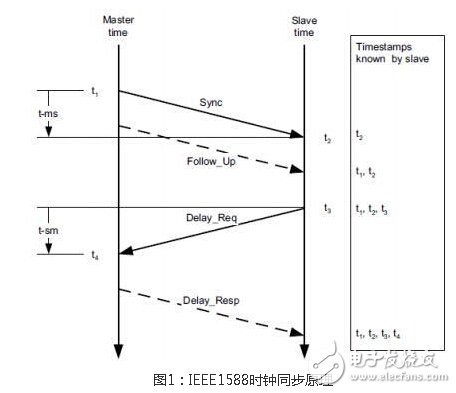

如圖所示,在經(jīng)過(guò)sync->delay_request->delay_response消息交互以后,受時(shí)鐘設(shè)備獲得4個(gè)時(shí)間值。以太網(wǎng)報(bào)文在兩個(gè)設(shè)備之間的環(huán)路時(shí)延可以計(jì)算為:

Troundtrip=(t4-t1)-(t3-t2)

假設(shè)包傳輸時(shí)延是對(duì)稱的,那么單路時(shí)延是:

Ttripdelay=((t4-t1)-(t3-t2))/2

從時(shí)鐘設(shè)備的時(shí)鐘和主時(shí)鐘的差值是:

Tdelta=t2-(t1+Ttripdelay)

實(shí)際部署時(shí),時(shí)鐘源發(fā)送sync消息,從設(shè)備根據(jù)多個(gè)sync消息來(lái)計(jì)算本地時(shí)鐘的偏差。當(dāng)從設(shè)備需要同步本地時(shí)鐘相位的時(shí)候,發(fā)送delay_req消息,時(shí)鐘源發(fā)送delay_response,從設(shè)備根據(jù)獲得的4個(gè)時(shí)間值來(lái)估計(jì)相位的偏差。

對(duì)于時(shí)鐘源設(shè)備,如果在發(fā)送sync報(bào)文時(shí)所帶的時(shí)間戳就是報(bào)文發(fā)送時(shí)采集的準(zhǔn)確時(shí)間,這種模式叫做single step模式。如果發(fā)送sync報(bào)文的時(shí)候所帶的時(shí)間戳只是一個(gè)近似時(shí)間,sync報(bào)文發(fā)送的準(zhǔn)確時(shí)間不能在發(fā)送sync報(bào)文的時(shí)候獲得或者實(shí)時(shí)插入到sync報(bào)文中,時(shí)鐘源設(shè)備需要發(fā)一個(gè)follow up消息報(bào)文,用來(lái)傳遞sync 報(bào)文的準(zhǔn)確發(fā)送時(shí)間,這種模式叫做two step模式。下面介紹的PHY 方案支持時(shí)鐘源single step,TI的KeyStone架構(gòu)支持時(shí)鐘源two step模式。

3 1588芯片實(shí)現(xiàn)方案

根據(jù)打時(shí)間戳的方式不同,常見(jiàn)的1588方案分為軟件時(shí)間戳方案和硬件時(shí)間戳方案。軟件方案通常是通過(guò)軟件手段在網(wǎng)絡(luò)報(bào)文的接收中記錄PTP報(bào)文接收或發(fā)送時(shí)間,處理靈活,可以根據(jù)應(yīng)用場(chǎng)景靈活處理PTP協(xié)議報(bào)文,支持多種封裝格式。但是因?yàn)檐浖袛嗟臅r(shí)間抖動(dòng)大,軟件時(shí)間戳方案的精度較差,在對(duì)精度要求不高的情況下使用。硬件方案通過(guò)特殊硬件解析PTP 報(bào)文,并用硬件記錄報(bào)文發(fā)送或接收時(shí)間。硬件方案精度高,但是需要特殊硬件解析PTP報(bào)文,在特殊場(chǎng)景中,例如PTP over IPSec,報(bào)文經(jīng)過(guò)加密,硬件無(wú)法解析PTP報(bào)文。根據(jù)硬件方案獲取報(bào)文收發(fā)時(shí)間地點(diǎn)不同,硬件方案又分在PHY上集成的1588方案和MII集成的1588方案等。

下面先簡(jiǎn)單介紹一下TI基于PHY的硬件解決方案作為參考,然后著重介紹KeyStone架構(gòu)上的基于MII和PA的1588 方案。

3.1 以太網(wǎng)PHY1588方案(DP83640)

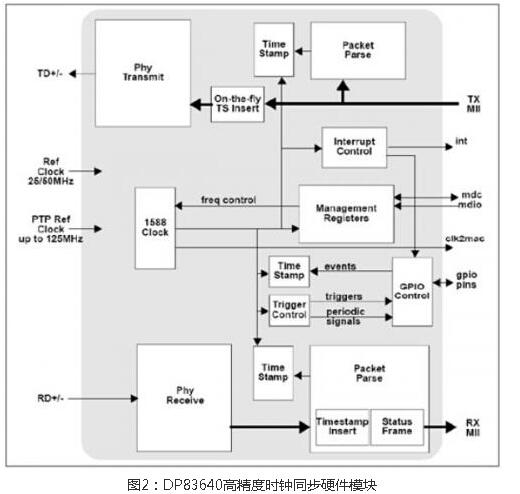

DP83640[11]是一款百兆網(wǎng)口PHY,集成1588功能,對(duì)外提供校準(zhǔn)過(guò)的時(shí)鐘和PPS信號(hào),同時(shí)還支持同步以太網(wǎng)功能,直接從物理層獲得遠(yuǎn)端時(shí)鐘。在支持同步以太網(wǎng)的情況下,使用1588做相位調(diào)整,實(shí)驗(yàn)表明最終的時(shí)鐘偏差精度可以達(dá)到納秒以下。

83640 timestamp模塊維護(hù)一個(gè)本地的1588計(jì)數(shù)器,包括32bit的秒計(jì)數(shù)和30bit的納秒計(jì)數(shù)。PTP報(bào)文中要求的48bit秒計(jì)數(shù)中的高16位需要軟件維護(hù)。上層軟件在發(fā)送一個(gè)1588報(bào)文的時(shí)候,時(shí)間戳中秒計(jì)數(shù)的高16位由軟件設(shè)置的,低32位設(shè)置為0。

報(bào)文解析模塊用來(lái)匹配解析PTP報(bào)文。83640支持1588Annex D&E和Annex F格式的報(bào)文。當(dāng)PTP報(bào)文送至PHY時(shí),報(bào)文解析硬件檢測(cè)到這個(gè)PTP報(bào)文的時(shí)鐘,在報(bào)文發(fā)出時(shí),把本地的時(shí)間戳寫到PTP報(bào)文里面,并修改相關(guān)的CRC 和CHKSUM值。83640支持1588 single step模式的時(shí)鐘源。在報(bào)文接收方向,同樣有報(bào)文解析硬件。在解析到PTP報(bào)文以后,接收?qǐng)?bào)文的準(zhǔn)確時(shí)間戳可以插入在報(bào)文里,或者通過(guò)控制接口上報(bào)。

83640的1588時(shí)鐘模塊對(duì)外提供頻率控制接口,軟件通過(guò)控制寄存器可以調(diào)整輸出的時(shí)鐘頻率。1588時(shí)鐘模塊根據(jù)上層軟件的配置,對(duì)1588時(shí)鐘模塊的輸入時(shí)鐘信號(hào)微調(diào),然后分頻輸出。時(shí)鐘調(diào)整是通過(guò)調(diào)整每個(gè)時(shí)鐘周期的時(shí)間來(lái)實(shí)現(xiàn)的。在每個(gè)時(shí)鐘周期調(diào)整的單位是2-32ns。在正常模式下,這個(gè)調(diào)整機(jī)制用來(lái)補(bǔ)償本地時(shí)鐘和時(shí)鐘源的差距。在長(zhǎng)期工作以后產(chǎn)生累積同步誤差時(shí),軟件可以調(diào)整寄存器的值,在一定時(shí)間內(nèi),對(duì)頻率向上或者向下微調(diào),以補(bǔ)償相位差距。當(dāng)在相位補(bǔ)償以后,恢復(fù)正常頻率補(bǔ)償模式。

軟件協(xié)議棧通過(guò)協(xié)議處理以后獲得本地的時(shí)鐘與時(shí)鐘源的絕對(duì)時(shí)間差值,然后通過(guò)寄存器調(diào)整本地絕對(duì)時(shí)間戳。在修改時(shí),軟件把絕對(duì)時(shí)間差值寫入寄存器,然后使能修改。這種方法適用初始同步時(shí)單次校正本地絕對(duì)時(shí)間戳。如在正常工作中出現(xiàn)累積相位偏差,應(yīng)該使用前面介紹的微調(diào)方法,避免輸出時(shí)鐘抖動(dòng)。

應(yīng)用層通過(guò)設(shè)置83640的trigger control模塊來(lái)控制輸出PPS 或者其他同步信號(hào)。應(yīng)用可以設(shè)置在timestamp 的哪些具體時(shí)刻某個(gè)GPIO管腳可以發(fā)生反轉(zhuǎn)。trigger的輸出可以線與并輸出到GPIO管腳,通過(guò)線與可以是輸出復(fù)雜的周期波形。

83640方案實(shí)現(xiàn)簡(jiǎn)單,直接輸出矯正時(shí)鐘及相位信號(hào),但是對(duì)于復(fù)雜傳輸場(chǎng)景支持困難;而且相比不包含IEEE1588功能的PHY芯片,83640的成本要高出許多。

3.2 KeyStone1 1588方案

KeyStone架構(gòu)是TI推出的高性能多核架構(gòu),現(xiàn)在已經(jīng)有KeyStone1和KeyStone2兩種架構(gòu)。KeyStone架構(gòu)中也包含了對(duì)IEEE1588功能的支持。

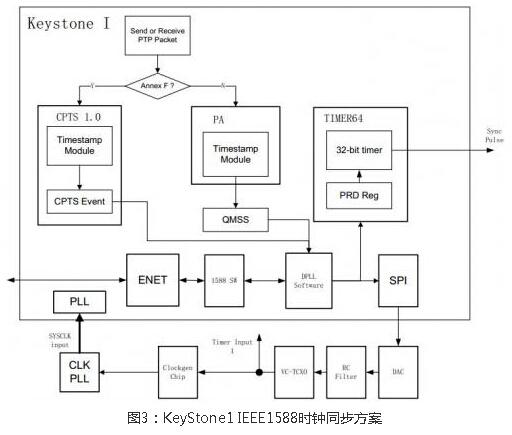

KeyStone1系列芯片的1588方案包括兩個(gè)硬件部分:記錄時(shí)間戳,發(fā)送同步脈沖。KeyStone1支持two step的時(shí)間戳模式,同時(shí)也能支持1588協(xié)議中Annex D&E和Annex F規(guī)定的PTP報(bào)文解析。

對(duì)于記錄時(shí)間戳,KeyStone1對(duì)于Annex D&E和Annex F采用不同的硬件來(lái)支持。Annex D&E使用以太網(wǎng)協(xié)處理(NetCP)里面的包加速器(PA)來(lái)支持;Annex F報(bào)文使用以太網(wǎng)交換機(jī)(GE Switch)里面的CPTS模塊來(lái)支持 [12-13]。

對(duì)于同步信號(hào)的輸出,KeyStone1里面需要通過(guò)Timer64[14]來(lái)完成。軟件通過(guò)CPTS或者PA獲取到時(shí)間戳后,計(jì)算需要調(diào)整的頻率和相位,然后通過(guò)配置Timer64的周期寄存器來(lái)更改Timer64的輸出周期,調(diào)整輸出的相位信息;通過(guò)SPI接口調(diào)整外部的VCXO的輸出頻率,矯正本地時(shí)鐘頻率。

3.2.1 Annex D&E PTP報(bào)文處理

PA內(nèi)部會(huì)維護(hù)一個(gè)48bit的計(jì)時(shí)器,該計(jì)時(shí)器的頻率與PA的頻率一致(一般是350MHz)。由于Annex D&E報(bào)文的承載方式為IP/UDP承載(報(bào)文模式為IPv4和IPv6),當(dāng)用戶收到或者發(fā)送一個(gè)IPv4或IPv6的PTP報(bào)文時(shí),在PA 側(cè)會(huì)記錄一個(gè)報(bào)文接收(或發(fā)送)的時(shí)間戳,這個(gè)時(shí)間戳只有32bit(為48bit中的低32bit)。這個(gè)時(shí)間戳保存在用戶指定的QMSS的某個(gè)Queue的描述符里面。

用戶從Queue中提取出該描述符:如果是接收,用戶可根據(jù)描述符信息解析報(bào)文類型,獲取報(bào)文內(nèi)容,同時(shí)讀取32bit時(shí)間戳并換算成絕對(duì)時(shí)間。如果是發(fā)送,用戶只需讀取時(shí)間戳,轉(zhuǎn)換為1588 48bit絕對(duì)時(shí)間后按照1588 two step的規(guī)則再做報(bào)文發(fā)送。

3.2.2 Annex F PTP報(bào)文處理

GE Switch模塊上的CPTS模塊支持對(duì)1588 Annex F(以太網(wǎng)封裝)的PTP報(bào)文解析,支持VLAN。在CPSW邏輯匹配到PTP報(bào)文時(shí),會(huì)觸發(fā)一個(gè)硬件信號(hào)給CPTS模塊用來(lái)觸發(fā)時(shí)間戳獲取。

CPTS 的時(shí)間戳模塊維護(hù)一個(gè)32bit的timer,根據(jù)配置,這個(gè)timer可以工作在二分之一CPU主頻上。這個(gè)timer 是一個(gè)free run timer。軟件通過(guò)這個(gè)timer換算得到1588的32bit納秒時(shí)鐘和48bit秒時(shí)鐘。因?yàn)閠imer只有32bit,所以軟件需要處理timer反轉(zhuǎn)事件,用來(lái)維護(hù)秒信息。CPTS得到時(shí)間事件以后,會(huì)將PTP報(bào)文的消息類型和Sequence ID等信息壓入EVENT FIFO中,并觸發(fā)中斷讓用戶處理。

3.2.3 同步信號(hào)的產(chǎn)生

同步信號(hào)需要通過(guò)Timer64來(lái)產(chǎn)生。由于Timer64,PA以及CPTS都是共用KeyStone外部的VCXO,因此從時(shí)間源上保證各個(gè)計(jì)時(shí)器之間沒(méi)有累積誤差。這樣計(jì)算出來(lái)的各個(gè)絕對(duì)時(shí)間也是固定不變的。

關(guān)于同步信號(hào)的時(shí)間戳,有兩點(diǎn)需要說(shuō)明:

1.KeyStone芯片的1588功能不維護(hù)絕對(duì)時(shí)間戳,時(shí)間信息是從CPTS timer或者PA的timer換算出來(lái)。這樣也不支持對(duì)1588報(bào)文發(fā)送時(shí)實(shí)時(shí)修改,所以在用KeyStone芯片做時(shí)鐘源時(shí),芯片只支持two step模式。

2.輸出時(shí)鐘方案需使用KeyStone1芯片上的定時(shí)器的輸出。因?yàn)镃PTS(或PA)上打時(shí)間戳的計(jì)數(shù)器和定時(shí)器使用的時(shí)鐘雖然是同源,但是相位不同,產(chǎn)生的PPS時(shí)鐘時(shí),需要軟件參與校正兩個(gè)計(jì)數(shù)器,并對(duì)記錄相應(yīng)的相位差。具體實(shí)現(xiàn)時(shí),需要首先對(duì)CPTS(或PA)里面的計(jì)數(shù)器和選定的Timer64計(jì)數(shù)器相差相位進(jìn)行計(jì)算。軟件首先操作CPTS(或PA)寄存器,觸發(fā)一個(gè)CPTS時(shí)間戳記錄事件(或者發(fā)起一個(gè)讀取PA時(shí)間戳寄存器的命令),然后馬上讀取timer64的值。考慮到cache問(wèn)題以及硬件總線上的競(jìng)爭(zhēng)可能性,軟件應(yīng)在一個(gè)循環(huán)內(nèi)多次執(zhí)行這個(gè)操作,保證執(zhí)行程序加載到L1 cache中,兩個(gè)時(shí)鐘之間的相位差應(yīng)該可以通過(guò)循環(huán)幾次獲得的值平均得到。

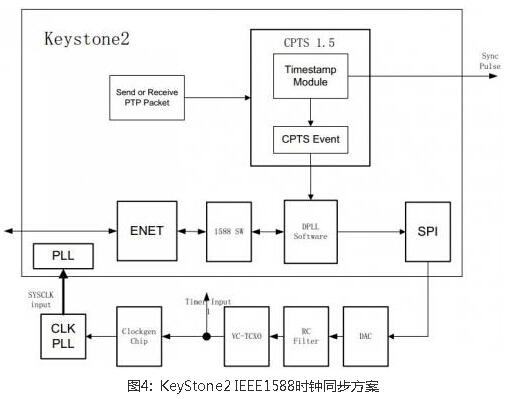

3.3 KeyStone2 1588方案

KeyStone2架構(gòu)的TI芯片對(duì)1588的支持做了改進(jìn)和增強(qiáng)。CPTS模塊支持同步以太網(wǎng)(Annex F)和1588 Annex D &E的報(bào)文。在KeyStone2芯片中,PPS輸出是直接由CPTS邏輯驅(qū)動(dòng)的。軟件通過(guò)設(shè)置相關(guān)寄存器設(shè)置下一個(gè)PPS 輸出時(shí)timestamp的值,當(dāng)計(jì)數(shù)器跑到設(shè)置的值的時(shí)候,硬件觸發(fā)PPS信號(hào)輸出。

相比KeyStone1的方案,KeyStone2的主要優(yōu)點(diǎn)在于:

1.方案簡(jiǎn)單,涉及到的硬件和底層器件更少

KeyStone1需要PA,CPTS,Timer64,QMSS等外設(shè)和加速器來(lái)支持整套方案,而KeyStone2只需要CPTS一個(gè)模塊就可以支持Annex D&E和Annex F的PTP報(bào)文,同時(shí)也支持同步信號(hào)的輸出;

2.時(shí)間戳個(gè)數(shù)減少,降低了計(jì)算復(fù)雜度

KeyStone1里面需要計(jì)算包括PA時(shí)間戳,CPTS時(shí)間戳以及Timer64的時(shí)間戳在內(nèi)的共計(jì)3個(gè)時(shí)間戳與PTP報(bào)文的真實(shí)時(shí)間的絕對(duì)時(shí)間相差;KeyStone2里面只有CPTS一個(gè)時(shí)間戳需要計(jì)算;

3.方案全由硬件邏輯完成,徹底避免了軟件干預(yù)同時(shí)也提高了同步精度

KeyStone 1的方案由于記錄時(shí)間戳的時(shí)間源(PA和CPTS)與發(fā)送同步信號(hào)的時(shí)間源(Timer64)是不同的,因此在系統(tǒng)運(yùn)行的時(shí)候需要軟件計(jì)算不同時(shí)間源的絕對(duì)時(shí)間差,這樣才能在后面的時(shí)間同步中精確調(diào)整時(shí)間。這里有軟件讀取并計(jì)算時(shí)間差的工作,這部分工作不可避免的存在軟件誤差,雖然可以通過(guò)多次計(jì)算取平均等統(tǒng)計(jì)手段縮小誤差,但還是對(duì)精度存在一定的影響。KeyStone2中,記錄時(shí)間戳和發(fā)送同步脈沖都在CPTS中,因此無(wú)需計(jì)算兩者的時(shí)間差,這樣就避免了軟件干預(yù),也提高了同步精度。

4 KeyStone1 1588方案實(shí)現(xiàn)

前文從原理和方案上描述了KeyStone中如何實(shí)現(xiàn)1588方案,本章節(jié)以KeyStone1為例,從技術(shù)細(xì)節(jié)方面來(lái)闡述1588實(shí)現(xiàn)方式。

以Annex F的PTP報(bào)文為例,1588的實(shí)現(xiàn)主要分為配置Gbe Switch[3]和計(jì)算時(shí)間偏差兩部分。整體流程如下:當(dāng)接收(或發(fā)送)一個(gè)802.3的PTP報(bào)文時(shí),Gbe Switch會(huì)自動(dòng)偵測(cè)到PTP報(bào)文的接收(或發(fā)送)時(shí)間,并將該時(shí)間戳記錄下來(lái);用戶根據(jù)記錄下來(lái)的時(shí)間戳,配置Timer64的時(shí)間輸出信號(hào),獲取當(dāng)前需要調(diào)整的時(shí)間偏差。

4.1 Gbe Switch配置

KeyStone1中的Gbe Switch是一個(gè)集成了1588 PTP報(bào)文檢測(cè)的交換機(jī),其中CPTS用來(lái)記錄時(shí)間戳,CPSW用來(lái)偵測(cè)1588報(bào)文。因此1588實(shí)現(xiàn)方式主要通過(guò)配置CPTS和配置CPSW來(lái)實(shí)現(xiàn)。

4.1.1 CPTS配置

CPTS是KeyStone1架構(gòu)中Gbe Switch中的一個(gè)模塊,請(qǐng)參考文獻(xiàn)[12]中的2.3.5章節(jié)。該章節(jié)詳細(xì)介紹了CPTS模塊的工作場(chǎng)景和寄存器列表。

CPTS 配置步驟如下:

1)復(fù)位CPTS模塊;

CPTS的復(fù)位通過(guò)將TS_CONTROL寄存器中的CPTS_EN位域?qū)?來(lái)實(shí)現(xiàn)。

2)選擇CPTS時(shí)鐘源;

CPTS時(shí)鐘源在CPTS_RFTCLK_SEL寄存器中選擇,有四種時(shí)鐘源可以選擇:SYSCLK3,SYSCLK4,TIMI0 和TIMI1。其中SYSCLK3是1/2 CPU時(shí)鐘,SYSCLK4是1/3 CPU時(shí)鐘,TIMI0和TIMI1分別是兩個(gè)外部時(shí)鐘輸入pin腳,原本是作為Timer64的輸入時(shí)鐘,這里也可以復(fù)用為CPTS的時(shí)鐘源。

3)使能CPTS模塊;

CPTS的使能通過(guò)將TS_CONTROL寄存器中的CPTS_EN位域?qū)?來(lái)實(shí)現(xiàn)。當(dāng)CPTS使能后,CPTS內(nèi)部的時(shí)間記數(shù)器就會(huì)根據(jù)輸入時(shí)鐘的頻率開(kāi)始記數(shù)。

4)使能CPTS中斷;

CPTS模塊中斷使能通過(guò)配置INT_EABLE來(lái)完成。CPTS可以產(chǎn)生多種事件的中斷,主要有:

Push中斷:用戶手動(dòng)觸發(fā)一個(gè)Push事件,該事件會(huì)記錄當(dāng)前CPTS的時(shí)間戳,并觸發(fā)中斷;

記數(shù)器翻轉(zhuǎn)中斷:當(dāng)CPTS的32bit記數(shù)器從0xFFFFFFFF變?yōu)?x00000000時(shí)會(huì)自動(dòng)觸發(fā)一個(gè)中斷;

記數(shù)器半翻轉(zhuǎn)中斷:當(dāng)CPTS的32bit記數(shù)器從0x7FFFFFFF變?yōu)?x80000000時(shí)會(huì)自動(dòng)觸發(fā)一個(gè)中斷;

以太網(wǎng)PTP報(bào)文接收中斷:當(dāng)接受1個(gè)以太網(wǎng)PTP報(bào)文時(shí)觸發(fā)中斷;

以太網(wǎng)PTP報(bào)文發(fā)送中斷:當(dāng)發(fā)送1個(gè)以太網(wǎng)PTP報(bào)文時(shí)觸發(fā)中斷;

4.1.2 CPSW的配置

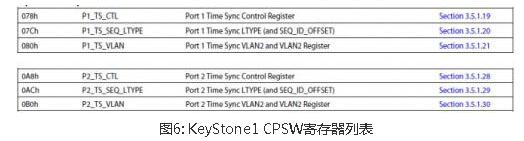

CPSW是屬于Switch的組成部分,可以通過(guò)配置CPSW讓Switch識(shí)別PTP報(bào)文。CPSW的報(bào)文識(shí)別功能也通過(guò)配置寄存器的方式來(lái)實(shí)現(xiàn)。需要說(shuō)明的是,由于Switch對(duì)外有兩個(gè)接口(port1和port2),因此對(duì)應(yīng)的寄存器也有兩份。其寄存器列表如下圖所示:

配置步驟如下:

1)配置LTYPE;

每種以太網(wǎng)報(bào)文都有一個(gè)類型,CPSW將根據(jù)這個(gè)類型配置偵測(cè)用戶需要的報(bào)文。根據(jù)以太網(wǎng)報(bào)文的定義,IEEE1588的PTP報(bào)文的類型為0x88F7。用戶需要將這個(gè)類型寫入Pn_TS_SEQ_LTYPE中(n表示端口號(hào))。

2)配置VLAN ID(如果使能了VLAN報(bào)文的話);

用戶可以定義需要的VLAN ID,在Pn_TS_VLAN寄存器里面配置。

3)使能CPSW檢測(cè)模塊;

CPSW的使能包括接收和發(fā)送的使能,需要用戶配置Pn_TS_CTL里面對(duì)應(yīng)的位域。

4.2 時(shí)間偏差的計(jì)算和調(diào)整

Gbe Switch完成對(duì)PTP報(bào)文的時(shí)間戳記錄之后,用戶需要根據(jù)時(shí)間戳計(jì)算當(dāng)前需要調(diào)整的時(shí)間數(shù)。由于真實(shí)系統(tǒng)時(shí)間是基于Timer64的時(shí)間戳,因此用戶在計(jì)算CPTS的時(shí)間戳之后需要換算到真實(shí)系統(tǒng)時(shí)間。

為了方便說(shuō)明和計(jì)算,在下面的配置中,假定CPU時(shí)鐘為1GHz,CPTS采用1/3 CPU時(shí)鐘,Timer64的定時(shí)周期為1ms。

4.2.1 CPTS時(shí)鐘到系統(tǒng)時(shí)鐘

由于CPTS的時(shí)間戳只有32bit,因此CPTS翻轉(zhuǎn)后時(shí)間戳不能代表真實(shí)時(shí)間,用戶需要記錄翻轉(zhuǎn)的次數(shù)以獲得Tcpts。那么換算關(guān)系如下:

其中,N代表CPTS翻轉(zhuǎn)次數(shù),TIME_STAMP_CPTS代表當(dāng)前CPTS的32bit時(shí)間戳。Timer64是以1ms為周期進(jìn)行記數(shù)的定時(shí)器,其輸入時(shí)鐘為固定的1/6 CPU時(shí)鐘,因此可以算出Timer64的記數(shù)器范圍為0~166666(Timer64采用連續(xù)記數(shù)方式)。因此可以得出如下公式:

其中TIME_STAMP_TIMER代表當(dāng)前Timer64的時(shí)間戳。當(dāng)Timer64和CPTS完成使能,用戶可以通過(guò)讀取兩者時(shí)間戳的方式獲取兩者的在1ms內(nèi)的基本時(shí)間戳。假設(shè)讀取之后兩者時(shí)間戳偏差為Toffset,由于Timer64和CPTS同源,因此可以認(rèn)為此偏差在CPTS或Timer64復(fù)位前保持不變。

4.2.2 時(shí)間調(diào)整

1588的時(shí)間調(diào)整包括調(diào)頻和調(diào)相兩部分。通常來(lái)說(shuō),需要先保證頻率同步,然后再進(jìn)行相位調(diào)整。調(diào)頻的部分不需要Timer64的參與,需要比對(duì)PTP報(bào)文中的時(shí)間戳差值和CPTS記錄的時(shí)間戳,處理如下:

其中Teth1和Teth0分別表示收到的兩個(gè)PTP報(bào)文中自帶的主時(shí)鐘時(shí)間戳(納秒級(jí)),而Tcpts1和Tcpts0代表這接收這兩個(gè)PTP報(bào)文時(shí)由CPTS得到的時(shí)間。考慮到傳輸對(duì)稱性,這里可以不考慮傳輸過(guò)程時(shí)延的影響。

用戶通過(guò)比對(duì)?eth和?cpts來(lái)確定當(dāng)前系統(tǒng)頻率與主時(shí)鐘頻率的差別。

當(dāng)調(diào)頻過(guò)程基本完成,即?eth≈?cpts時(shí)可以進(jìn)行相位調(diào)整。調(diào)相的主要工作是調(diào)整Timer64的輸出脈沖,由于輸出脈沖以1ms為周期,因此只需計(jì)算在1ms內(nèi)的偏差即可。相位調(diào)整的主要原理如下:

其中,Teth表示接收到的PTP報(bào)文的主時(shí)鐘時(shí)間,Tcpts表示該P(yáng)TP報(bào)文對(duì)應(yīng)的CPTS時(shí)間,Toffset表示CPTS和Timer64的時(shí)間差,Ttripdelay表示網(wǎng)絡(luò)傳輸時(shí)間。

按照計(jì)算后,Timer64的輸出周期需要滿足如下條件:

4.3 KeyStone1 1588方案的說(shuō)明

KeyStone1的1588方案主要依靠配置Gbe Switch和軟件換算時(shí)間戳兩部分來(lái)完成。需要強(qiáng)調(diào)的是,在軟件換算時(shí)間的部分,這涉及到具體的1588時(shí)間戳計(jì)算算法。基于應(yīng)用的需求和精度需求,許多算法往往比這里介紹的更復(fù)雜,但是原理上來(lái)說(shuō)都是相同的。這也是KeyStone架構(gòu)使用軟件實(shí)現(xiàn)1588部分的一個(gè)優(yōu)勢(shì),用戶可以靈活使用軟件功能來(lái)提高1588的同步精度。

5 小結(jié)

從目前來(lái)看,IEEE1588v2標(biāo)準(zhǔn)已經(jīng)越來(lái)越多的應(yīng)用在通訊網(wǎng)絡(luò)中。由于IEEE1588v2標(biāo)準(zhǔn)也還在不斷的完善中,因此從技術(shù)角度出發(fā),熟悉1588同步原理,了解并設(shè)計(jì)不同場(chǎng)景中的1588方案,不論是從芯片設(shè)計(jì)角度或者基站整體解決方案角度來(lái)說(shuō),都是十分必要的。

本文簡(jiǎn)要的介紹了IEEE1588的原理,并分類分析了1588同步功能在PHY 以及KeyStone1和KeyStone2芯片上的應(yīng)用方案。以太網(wǎng)PHY實(shí)現(xiàn)1588同步的精度最高,但是成本相對(duì)比較昂貴;德州儀器的KeyStone架構(gòu)上集成了支持1588的Switch,用戶可以通過(guò)KeyStone架構(gòu)靈活實(shí)現(xiàn)1588同步功能,也為用戶的方案設(shè)計(jì)提供了更多的選擇。

-

芯片

+關(guān)注

關(guān)注

455文章

50714瀏覽量

423157 -

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5419瀏覽量

171603 -

寄存器

+關(guān)注

關(guān)注

31文章

5336瀏覽量

120232

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

STM32 IEEE1588時(shí)間同步

IEEE1588的原理

請(qǐng)問(wèn)怎么用STM32以太網(wǎng)的IEEE1588 PTP實(shí)現(xiàn)內(nèi)部RTC的同步更新?

IEEE1588協(xié)議及測(cè)試技術(shù),總結(jié)的太到位了

介紹一種IXIA IEEE1588測(cè)試解決方案

如何使用IEEE1588 (PTP) 同步時(shí)間?

請(qǐng)問(wèn)W5500芯片是否支持IEEE1588?

IEEE1588在分散運(yùn)動(dòng)控制系統(tǒng)中的應(yīng)用

IEEE1588時(shí)鐘同步在PTN網(wǎng)中的實(shí)現(xiàn)

IEEE1588同步原理及其在PTN網(wǎng)中的實(shí)現(xiàn)

IEEE1588及其測(cè)試方法簡(jiǎn)介[圖]

Silicon Labs推出為簡(jiǎn)化IEEE1588實(shí)施而設(shè)計(jì)的全新完整解決方案

Xilinx Zynq系統(tǒng)如何實(shí)現(xiàn)IEEE1588協(xié)議

IEEE1588時(shí)鐘同步在PTN網(wǎng)中的實(shí)現(xiàn)

在KeyStone器件實(shí)現(xiàn)IEEE1588時(shí)鐘方案

IEEE1588的原理介紹及在KeyStone1芯片上實(shí)現(xiàn)IEEE1588設(shè)計(jì)方案

IEEE1588的原理介紹及在KeyStone1芯片上實(shí)現(xiàn)IEEE1588設(shè)計(jì)方案

評(píng)論