1.引言

在現代雷達系統中,含DSP電路板應用很廣,含DSP電路板通常是以某種DSP芯片為核心,外圍配以雙口RAM(DRAM)和閃存(Flash)等器件。DSP芯片大多支持IEEE1149.1標準,并且在電路板中形成了邊界掃描鏈,支持邊界掃描。本文采用邊界掃描技術與傳統的外部輸入矢量測試方法相結合,為含DSP電路板的測試與診斷提供了可以借鑒的方法。

2.電路原理簡介及總體測試思想

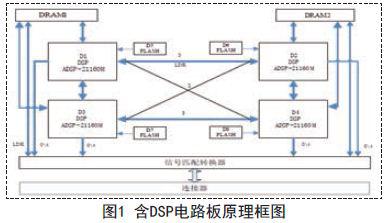

2.1 電路原理介紹

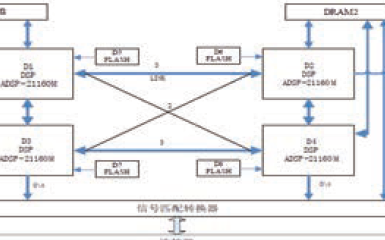

本文以雷達系統中某含DSP電路板為例對測試方法進行介紹,該電路以AD公司的ADSP-21160M為核心,外加DRAM、Flash、信號匹配轉換器組成,Flash為DSP工作提供配置程序,4個DSP之間通過Link口進行數據交換,同時DSP的部分數據線和地址線與DRAM的數據線和地址線相連,DSP的Link口通過信號匹配轉換器與外部連接器進行數據交換。該電路板在電路器件構成上使用了集成度較高的器件,芯片封裝采用了PQFP132、PLCC100等多種表貼器件,器件引腳間距極小,采用探筆測試可能破壞電路工藝;并且電路上的DSP芯片不能從電路板上取下,所以采用邊界掃描技術較為合理。如圖1所示。

2.2 測試與診斷分析

對電路中核心器件DSP的資料分析,芯片具有JTAG測試接口,具備邊界掃描測試的條件。但邊界掃描測試不是基于IP內核的測試,使用邊界掃描技術可以對電路測試但無法達到全面的測試與診斷,所以可以利用與傳統的外部輸入矢量測試方法相結合的方式實現電路的互連以及器件功能的測試,達到故障定位的目的。

2.3 測試系統組成

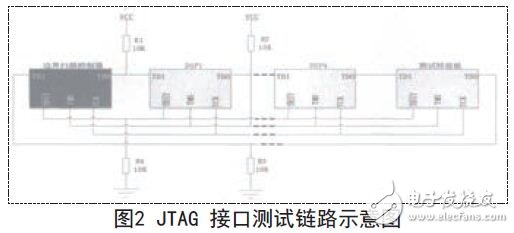

根據測試與診斷需求、測試工具以及電路本身的特點,設計穩壓電路、JTAG測試接口轉換電路以及加入一片具有邊界掃描功能的芯片(FPGA)構成的電路實現了對電路測試所需的資源。

*穩壓電路。穩壓電路對測試系統程控電源發送過來的電壓進行濾波、穩壓后提供被測板的工作電壓,保證被測板電源不會因為意外的原因產生突變。

*FPGA電路。該部分電路為被測板提供測試的地址和數據信號,測試時使用系統平臺上的邊掃控制器將被測電路板上DSP的測試鏈路的JTAG口與適配板上的FPGA的JTAG口構成一個測試鏈路,實現4個DSP之間互連測試、DSP與連接器連線測試、通過對FPGA配置程序實現FPGA與DSP間互連線測試。

*JTAG測試接口轉接電路。將被測板上的DSP與測試轉接板上的FPGA的JTAG接口構成一個測試通道,形成一個邊界掃描測試鏈路。如圖2所示。

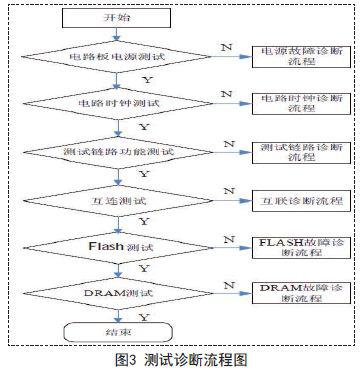

3.測試與診斷流程開發

基于邊界掃描技術的測試診斷流程開發主要內容包括對邊掃器件鏈路設計、引腳映射關系設置、邊界掃描控制器相關文檔設置,以及測試腳本語言的開發。圖3是該電路板的測試診斷流程圖。

*測試鏈路功能測試。實現對邊掃器件構成的測試鏈路的連接情況進行測試,以及完成邊掃器件引腳輸入輸出功能是否正常測試,只有在測試鏈路測試通過后才能使用邊界掃描控制器進行后續測試。

*互連測試。依據被測板電路原理圖和測試轉接板原理圖的網表文件,通過邊界掃描測試軟件實現對被測電路板上的邊掃器件(DSP)、測試轉接板上FPGA共五個器件間兩兩互連線的是否出現開路、短路、虛焊等問題的測試。

*Flash測試。被測電路板上的每個Flash的控制使能信號由不同的器件進行控制,在對Flash的測試過程中需要開發針對各Flash測試與診斷的測試腳本,在測試的過程中完成對故障的分析和定位,開發的測試腳本能夠定位到器件的具體引腳故障。

*DRAM測試。通過連接器發送DRAM配置程序的觸發信號,FPGA產生DRAM的讀寫時序,對DRAM的讀寫功能進行測試,FPGA讀寫的測試結果進行判讀并生成一定的測試結果數據由連接器采集至測試系統,判斷該部分電路功能是否正常。

按照上述開發過程實現的測試診斷流程的故障覆蓋率≥83%,故障檢測率約為92%,隔離到3個器件以內的故障隔離率≥95%.

4.總結

通過在測試轉接板上放置具有邊界掃描功能的芯片將該芯片與被測板上的邊掃芯片構成測試簇,傳統的外部輸入矢量測試彌補了邊掃測試的不足,進而實現了較高的電路測試覆蓋率。

-

dsp

+關注

關注

553文章

7987瀏覽量

348763 -

DRAM

+關注

關注

40文章

2311瀏覽量

183448 -

連接器

+關注

關注

98文章

14477瀏覽量

136431 -

雷達

+關注

關注

50文章

2930瀏覽量

117465

發布評論請先 登錄

相關推薦

基于邊界掃描的電路板測試系統

邊界掃描測試技術在帶DSP芯片數字電路板測試中的應用解析

柔性電路板的主要測試方法

針對含DSP電路板的測試方法與診斷分析

針對含DSP電路板的測試方法與診斷分析

評論