它是由常用的電路結構所決定的,低電平時電路往往有較高電平時更低的環路阻抗,而低阻抗則意味著抗干擾能力更強。

結合實際講一個有用的例子來加深印象:

有的同學可能已經學習了這樣的一條PCB布線規則-----在條件許可的情況下,高電平有效線要盡量縮短,低電平有效的線則盡量延長----這一條規則的存在基礎就是基于低電平時環路阻抗比較低,抗干擾能力比較強才起來的。

如OC或OD電路要控制一個電平就是通過它這個開關的通斷來實現的。

有在上拉電阻的情況下,開關接通,得低電平;開關切斷,得高電平。這樣,為了防止電路失控的情況下仍然是有效電平,那么當然是低電平有效才更“保險”了。結構上,象OC電路那樣,由于集電極更難擊穿,所以,也更不容易損壞。

對于其它圖騰柱輸出的電路,雖然0和1都有同樣的風險,但應用中還是有人愿意加一個上拉電阻,以取得類似OC或OD輸出的效果。至于為什么不采用下拉電阻而用上拉電阻,大家也可以分析一下。

另一個方面是OC或OD輸出的電路,使用上拉電阻后具有節能的效果。因為關斷后它是具有獲得高電平時的電流幾乎為0。

-

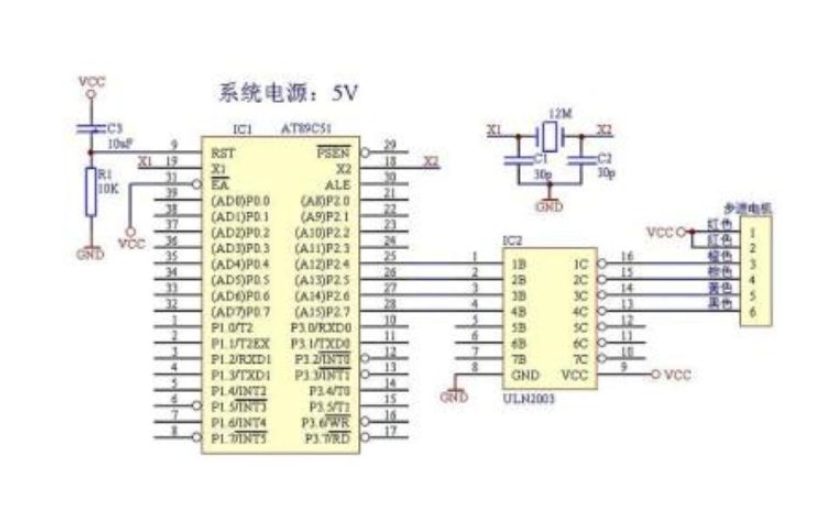

單片機

+關注

關注

6035文章

44554瀏覽量

634660 -

低電平

+關注

關注

1文章

115瀏覽量

13269

原文標題:為什么單片機管腳設計成低電平才有效?

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

為什么單片機有些管腳要設計成低電平有效?

為什么單片機有些管腳要設計成低電平有效?

單片機高低電平問題

單片機的管腳為什么要設計成低電平電路呢

單片機IO口初始為低電平的方法

單片機IO口低電平不為0V

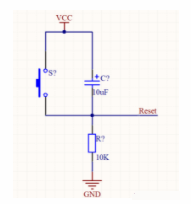

電子設計(4)高電平、低電平復位電路

為什么單片機管腳設計成低電平才有效

單片機管腳設計成低電平的原因是什么?

單片機管腳設計成低電平的原因是什么?

評論