復位電路的作用

在上電或復位過程中,控制CPU的復位狀態:這段時間內讓CPU保持復位狀態,而不是一上電或剛復位完畢就工作,防止CPU發出錯誤的指令、執行錯誤操作,也可以提高電磁兼容性能。

無論用戶使用哪種類型的單片機,總要涉及到單片機復位電路的設計。而單片機復位電路設計的好壞,直接影響到整個系統工作的可靠性。許多用戶在設計完單片機系統,并在實驗室調試成功后,在現場卻出現了“死機”、“程序走飛”等現象,這主要是單片機的復位電路設計不可靠引起的。

數字電路剛通電時都需要進行復位,復位的功能是將單片機里的重新開始,主要防止程序混亂,也就是跑飛、或者死機等現象,目的是使系統進入初始狀態,以便隨時接受各種指令進行工作,CPU的復位可靠性決定著產品系統的穩定性,因此在電路當中,發生任何一種復位后,系統程序將從重新開始執行,系統寄存器也都將恢復為默認值。下面總結幾種CPU復位方式。

1、上電復位上電復位就是直接給產品上電,上電復位與低壓 LVR操作有聯系,電源上電的過程是逐漸上升的曲線過程,這個過程不是瞬間的完成的,一上電時候系統進行初始化,此時振蕩器開始工作并提供系統時鐘,系統正常工作

2、看門狗復位

看門狗定時器CPU內部系統,它是一個自振式的 RC振蕩定時器,與外圍電路無關,也與CPU主時鐘無關,只要開啟看門狗功能也能保持計時,該溢出時候也會溢出,并產生復位

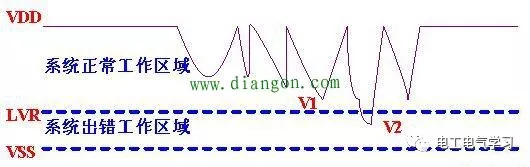

3、LVR低壓復位每個CPU都有一個復位電壓,這個電壓很低,有1.8V、2.5V等,當系統由于受到外界的影響導致輸入電壓過低,當低至復位電壓時候系統自動復位,當然,前提是系統要打開LVR功能,有時候也叫掉電復位。diangon.com如圖,當LVR<工作電壓<VDD時候,比如在V1時候工作是正常的,當VSS<工作電壓<LVR時候,系統有可能出錯,比如在V2時候,也就是我們常說的死區,這個狀態不確定。

4、外圍電路復位如果系統內部不能正常復位或者軟件復位無效的時候,可以依靠外部硬件復位。

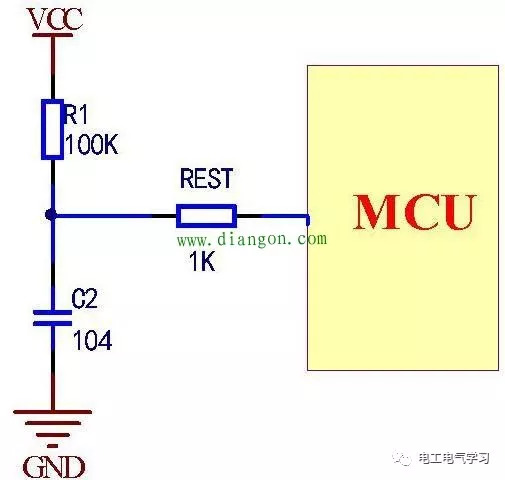

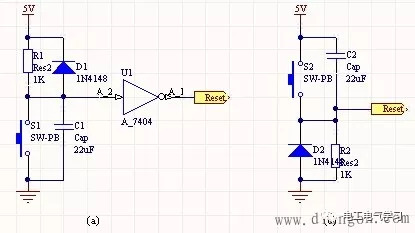

如圖是一種簡單的RC復位電路,電源接通時候,通過R1對C2進行充電,經過一段延遲后加到電路當中產生復位信號,這個復位信號的上升速度低于電源的上電速度,當復位引腳檢測到高電平時候,系統復位結束,進入正常工作狀態。

基本的復位方式

單片機在啟動時都需要復位,以使CPU及系統各部件處于確定的初始狀態,并從初態開始工作。89系列單片機的復位信號是從RST引腳輸入到芯片內的施密特觸發器中的。當系統處于正常工作狀態時,且振蕩器穩定后,如果RST引腳上有一個高電平并維持2個機器周期(24個振蕩周期)以上,則CPU就可以響應并將系統復位。單片機系統的復位方式有:手動按鈕復位和上電復位。

1、手動按鈕復位

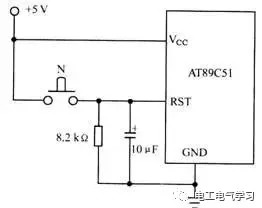

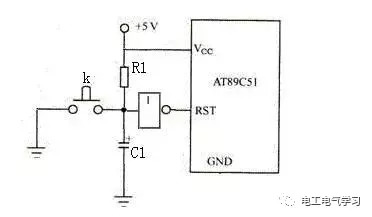

手動按鈕復位需要人為在復位輸入端RST上加入高電平(圖1)。一般采用的辦法是在RST端和正電源Vcc之間接一個按鈕。當人為按下按鈕時,則Vcc的+5V電平就會直接加到RST端。手動按鈕復位的電路如所示。由于人的動作再快也會使按鈕保持接通達數十毫秒,所以,完全能夠滿足復位的時間要求。

圖1

圖2

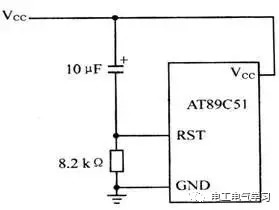

2、上電復位

AT89C51的上電復位電路如圖2所示,只要在RST復位輸入引腳上接一電容至Vcc端,下接一個電阻到地即可。對于CMOS型單片機,由于在RST端內部有一個下拉電阻,故可將外部電阻去掉,而將外接電容減至1μF。上電復位的工作過程是在加電時,復位電路通過電 容加給RST端一個短暫的高電平信號,此高電平信號隨著Vcc對電容的充電過程而逐漸回落,即RST端的高電平持續時間取決于電容的充電時間。為了保證系統能夠可靠地復位,RST端的高電平信號必須維持足夠長的時間。上電時,Vcc的上升時間約為10ms,而振蕩器的起振時間取決于振蕩頻率,如晶振頻率為10MHz,起振時間為1ms;晶振頻率為1MHz,起振時間則為10ms。在圖2的復位電路中,當Vcc掉電時,必然會使RST端電壓迅速下降到0V以下,但是,由于內部電路的限制作用,這個負電壓將不會對器件產生損害。另外,在復位期間,端口引腳處于隨機狀態,復位后,系統將端口置為全“l”態。如果系統在上電時得不到有效的復位,則程序計數器PC將得不到一個合適的初值,因此,CPU可能會從一個未被定義的位置開始執行程序。

3、積分型上電復位

常用的上電或開關復位電路如圖3所示。上電后,由于電容C3的充電和反相門的作用,使RST持續一段時間的高電平。當單片機已在運行當中時,按下復位鍵K后松開,也能使RST為一段時間的高電平,從而實現上電或開關復位的操作。

根據實際操作的經驗,下面給出這種復位電路的電容、電阻參考值。

圖3中:C:=1uF,Rl=lk,R2=10k

圖3 積分型上電復位電路

專用芯片復位電路

上電復位電路 在控制系統中的作用是啟動單片機開始工作。但在電源上電以及在正常工作時電壓異常或干擾時,電源會有一些不穩定的因素,為單片機工作的穩定性可能帶來嚴重的影響。因此,在電源上電時延時輸出給芯片輸出一復位信號。上復位電路另一個作用是,監視正常工作時電源電壓。若電源有異常則會進行強制復位。復位輸出腳輸出低電平需要持續三個(12/fc s)或者更多的指令周期,復位程序開始初始化芯片內部的初始狀態。等待接受輸入信號(若如遙控器的信號等)。

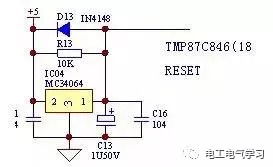

圖4 上電復位電路原理圖

上電復位電路原理分析

5V電源通過MC34064的2腳輸入,1腳便可輸出一個上升沿,觸發芯片的復位腳。電解電容C13是調節復位延時時間的。當電源關斷時,電解電容C13上的殘留電荷通過D13和MC34064內部電路構成回路,釋放掉電荷。以備下次復位啟用。

上電復位電路的關鍵性器件

關鍵性器件有:MC34064 。

圖6 內部結構框圖

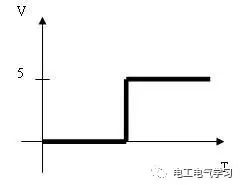

輸入輸出特性曲線

MC34064的輸出腳1腳的輸出(穩定之后的輸出)如下圖所示:

三極管欠壓復位電路

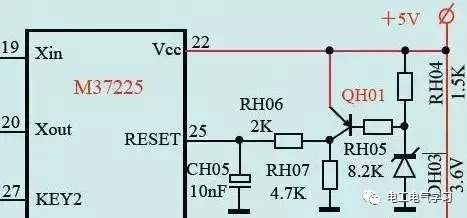

欠壓復位電路工作原理(圖6)w 接通電源,+5V電壓從“0V”開始上升,在升至3.6V之前,穩壓二極管DH03都處于截止狀態,QH01(PNP管)也處于截止狀態,無復位電壓輸出。w 當+5V電源電壓高于3.6V以后,穩壓二極管DH03反向擊穿,將其兩端電壓“箝位”于3.6V。當+5V電源電壓高于4.3V以后,QH01開始導通,復位電壓開始形成,當+5V電源電壓接近+5V時,QH01已經飽和導通,復位電壓達到穩定狀態。

圖6 欠壓復位電路圖

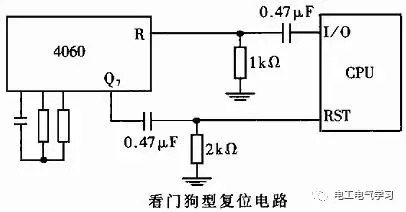

看門狗型復位電路

看門狗型復位電路主要利用CPU正常工作時,定時復位計數器,使得計數器的值不超過某一值;當CPU不能正常工作時,由于計數器不能被復位,因此其計數會超過某一值,從而產生復位脈沖,使得CPU恢復正常工作狀態。典型應用的Watchdog復位電路如圖7所示。此復位電路的可靠性主要取決于軟件設計,即將定時向復位電路發出脈沖的程序放在何處。一般設計,將此段程序放在定時器中斷服務子程序中。然而,有時這種設計仍然會引起程序走飛或工作不正常。原因主要是:當程序“走飛”發生時定時器初始化以及開中斷之后的話,這種“走飛”情況就有可能不能由Watchdog復位電路校正回來。因為定時器中斷一真在產生,即使程序不正常,Watchdog也能被正常復位。為此提出定時器加預設的設計方法。即在初始化時壓入堆棧一個地址,在此地址內執行的是一條關中斷和一條死循環語句。在所有不被程序代碼占用的地址盡可能地用子程序返回指令RET代替。這樣,當程序走飛后,其進入陷阱的可能性將大大增加。而一旦進入陷阱,定時器停止工作并且關閉中斷,從而使Watchdog復位電路會產生一個復位脈沖將CPU復位。當然這種技術用于實時性較強的控制或處理軟件中有一定的困難

圖7 看門狗型復位電路

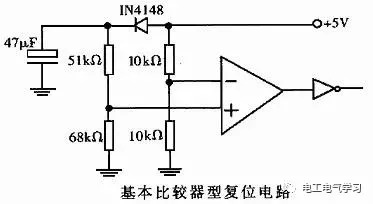

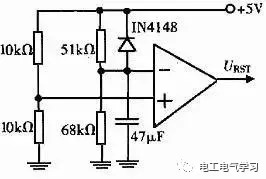

比較器型復位電路

比較器型復位電路的基本原理如圖8所示。上電復位時,由于組成了一個RC低通網絡,所以比較器的正相輸入端的電壓比負相端輸入電壓延遲一定時間。而比較器的負相端網絡的時間常數遠遠小于正相端RC網絡的時間常數,因此在正端電壓還沒有超過負端電壓時,比較器輸出低電平,經反相器后產生高電平。復位脈沖的寬度主要取決于正常電壓上升的速度。由于負端電壓放電回路時間常數較大,因此對電源電壓的波動不敏感。

但是容易產生以下二種不利現象:

(1)電源二次開關間隔太短時,復位不可靠;

(2)當電源電壓中有浪涌現象時,可能在浪涌消失后不能產生復位脈沖。為此,將改進比較器重定電路,如圖9所示。這個改進電路可以消除第一種現象,并減少第二種現象的產生。為了徹底消除這二種現象,可以利用數字邏輯的方法與比較器配合,設計如圖9所示的比較器重定電路。此電路稍加改進即可作為上電復位與看門狗復位電路共同復位的電路,大大提高了復位的可靠性。

圖8 比較器型復位電路

圖9 改進型比較器型復位電路

單片機在可靠的復位之后,才會從0000H地址開始有序的執行應用程序。同時,復位電路也是容易受到外部噪 聲干擾的敏感部分之一。因此,復位電路應該具有兩個主要的功能:

1. 必須保證系統可靠的進行復位;

2. 必須具有一定的抗干擾的能力;

復位電路應該具有上電復位和手動復位的功能。以MCS-51單片機為例,復位脈沖的高電平寬度必須大于2個機器周期,若系統選用6MHz晶振,則一個機器周期為2us,那么復位脈沖寬度最小應為4us。在實際應用系統中,考慮到電源的穩定時間,參數漂移,晶振穩定時間以及復位的可靠性等因素,必須有足夠的余量。圖1是利用RC充電原理實現上電復位的電路設計。實踐證明,上電瞬間RC電路充電,RESET引腳出現正脈沖。只要RESET端保持10ms以上的高電平,就能使單片機有效的復位。

單片機在可靠的復位之后,才會從0000H地址開始有序的執行應用程序。同時,復位電路也是容易受到外部噪 聲干擾的敏感部分之一。因此,復位電路應該具有兩個主要的功能:

1. 必須保證系統可靠的進行復位;

2. 必須具有一定的抗干擾的能力;

一、復位電路的RC選擇

復位電路應該具有上電復位和手動復位的功能。以MCS-51單片機為例,復位脈沖的高電平寬度必須大于2個機器周期,若系統選用6MHz晶振,則一個機器周期為2us,那么復位脈沖寬度最小應為4us。在實際應用系統中,考慮到電源的穩定時間,參數漂移,晶振穩定時間以及復位的可靠性等因素,必須有足夠的余量。圖1是利用RC充電原理實現上電復位的電路設計。實踐證明,上電瞬間RC電路充電,RESET引腳出現正脈沖。只要RESET端保持10ms以上的高電平,就能使單片機有效的復位。

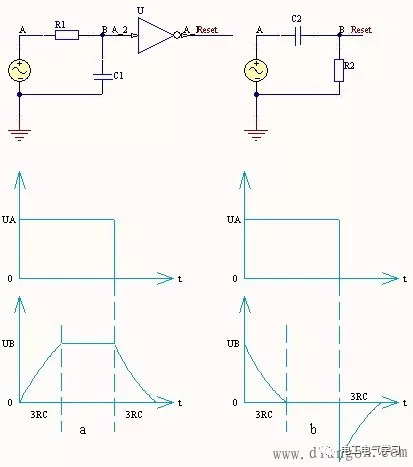

圖 1

對于圖1-a中的電容C兩端的電壓(即復位信號)是一個時間的函數:u(t)=VCC*[1-exp(-t/RC)]

對于圖1-b中的電阻R兩端的電壓(即復位信號)也是一個時間的函數u(t)=VCC*exp(-t/RC)

其中的VCC為電源電壓,RC為RC電路的時間常數=1K*22uF=22ms。有了這個公式,我們可以更方便的對以上電路進行透徹的分析。

圖1-a中非門的最小輸入高電平UIH=2.0v,當充電時間t=0.6RC時,則充電電壓u(t)=0.45VCC=0.45*5V,約等于2V,其中t即為復位時間。圖a中時間常數=22ms,則t=22ms*0.6=13ms。

二、復位電路的可靠性與抗干擾性分析

單片機復位電路端口的干擾主要來自電源和按鈕傳輸線串入的噪聲。這些噪聲雖然不會完全導致系統復位,但有時會破壞CPU內的程序狀態字的某些位的狀態,對控制產生不良影響。

1.電路結構形式與抗干擾性能

以圖1為例,電源噪聲干擾過程示意圖如圖2種分別繪出了A點和B點的電壓擾動波形。

有圖2可以看出,圖2(a)實質上是個低通濾波環節,對于脈沖寬度小于3RC的干擾有很好的抑制作用;圖2(b)實質上是個高通濾波環節,對脈沖干擾沒有抑制作用。由此可見,對于圖1所示的兩種復位電路,a的抗干擾電源噪聲的能力要優于b。

2. 復位按鈕傳輸線的影響

復位按鈕一般都是安裝在操作面板上,有較長的傳輸線,容易引起電磁感應干擾。按鈕傳輸線應采用雙絞線(具有抑制電磁感應干擾的性能),并遠離交流用電設備。在印刷電路板上,單片機復位端口處并聯0.01-0.1uF的高頻電容,或配置使密特電路,將提高對串入噪聲的抑制能力。

圖 2

3. 供電電源穩定過程對復位的影響

單片機系統復位必須在CPU得到穩定的電源后進行,一次上電復位電路RC參數設計應考慮穩定的過渡時間。

為了克服直流電源穩定過程對上電自動復位的影響,可采用如下措施:

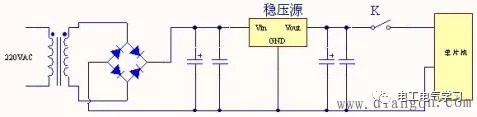

(1) 將電源開關安裝在直流側,合上交流電源,待直流電壓穩定后再合供電開關K,如圖3所示。

圖 3

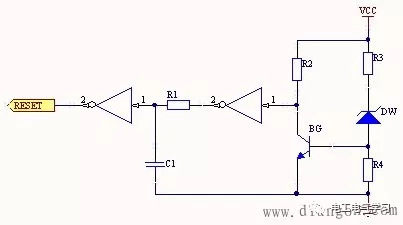

(2) 采用帶電源檢測的復位電路,如圖4所示。合理配置電阻R3、R4的阻值和選擇穩壓管DW的擊穿電壓,使VCC未達到額定值之前,三極管BG截止,VA點電平為低,電容器C不充電;當VCC穩定之后,DW擊穿,三極管BG飽和導通,致使VA點位高電平,對電容C充電,RESET為高電平,單片機開始復位過程。當電容C上充電電壓達到2V時,RESET為低電平,復位結束。

圖 4

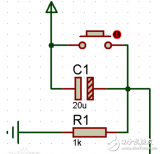

4. 并聯放電二極管的必要性

在圖1復位電路中,放電二極管D不可缺少。當電源斷電后,電容通過二極管D迅速放電,待電源恢復時便可實現可靠上電自動復位。若沒有二極管D,當電源因某種干擾瞬間斷電時,由于C不能迅速將電荷放掉,待電源恢復時,單片機不能上電自動復位,導致程序運行失控。電源瞬間斷電干擾會導致程序停止正常運行,形成程序“亂飛”或進入“死循環”。若斷電干擾脈沖較寬,可以使RC迅速放電,待電源恢復后通過上電自動復位,使程序進入正常狀態;若斷電干擾脈沖較窄,斷電瞬間RC不能充分放電,則電源恢復后系統不能上電自動復位。

I/O接口芯片的延時復位

在單片機系統中,某些I/O接口芯片的復位端口與單片機的復位端口往往連在一起,即統一復位。接口芯片由于生產廠家不同,復位時間也稍有不同;復位線較長而又較大的分布電容,導致這些接口的復位過程滯后于單片機。工程實踐表明,當單片機復位結束立即對這些I/O芯片進行初始化操作時,往往導致失敗。因此,當單片機進入0000H地址后,首先執行1-10ms的軟件延時,然后再對這些I/O芯片進行初始化。

-

單片機

+關注

關注

6035文章

44554瀏覽量

634659 -

接口芯片

+關注

關注

0文章

87瀏覽量

16777 -

復位電路

+關注

關注

13文章

322瀏覽量

44586

原文標題:單片機復位電路總結

文章出處:【微信號:EngicoolArabic,微信公眾號:電子工程技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

CPU與單片機的復位電路的作用及基本復位方式

復位電路的作用及基本的復位方式

復位電路的作用及基本的復位方式

評論