本文主要是關于tms320c6748的相關介紹,并著重對tms320c6748原理圖及其DSP子系統進行了詳盡的闡述。

tms320c6748

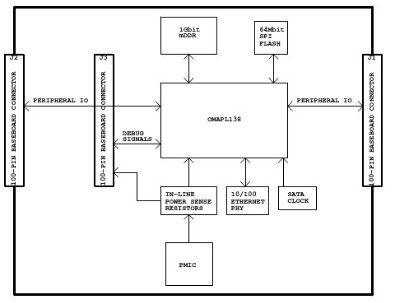

TMS320C6748是德州儀器 (TI) 推出浮點功能的全新高性能處理器 ,這款芯片也是業界功耗最低的浮點數字信號處理器 (DSP),可充分滿足高能效、連通性設計對高集成度外設、更低熱量耗散以及更長電池使用壽命的需求。不僅具備通用并行端口 (uPP),同時也是 TI 首批集成串行高級技術附件 (SATA)的器件。 廣州創龍推出的TL6748-EVM評估套件為開發者使用TI TMS320C6748處理器提供了完善的軟件開發環境,系統支持:裸機、SYS/BIOS、DSP/BIOS。提供參考底板原理圖,DSP C6748入門教程、豐富的Demo程序、完整的軟件開發包,以及詳細的C6748系統開發文檔,方便用戶快速評估TMS320C6748處理器、設計系統驅動及其定制應用軟件,也大大降低產品開發周期,讓客戶產品快速上市。主要面向電力、通信、工控、音視頻處理等數據采集處理行業。 TL6748-EVM評估套件是一個功能豐富的開發板,為嵌入式設計人員提供快捷簡單的實踐方式來評估TMS320C674x系列處理器,是一個完整的實驗評估平臺。

德州儀器 (TI) 推出浮點功能的全新高性能處理器 —— TMS320C6748,這款芯片也是業界功耗最低的浮點數字信號處理器 (DSP),可充分滿足高能效、連通性設計對高集成度外設、更低熱量耗散以及更長電池使用壽命的需求。不僅具備通用并行端口 (uPP),同時也是 TI 首批集成串行高級技術附件 (SATA)的器件。

廣州創龍推出的TL6748-EVM評估套件為開發者使用TI TMS320C6748處理器提供了完善的軟件開發環境,系統支持:裸機、SYS/BIOS、DSP/BIOS。提供參考底板原理圖,DSP C6748入門教程、豐富的Demo程序、完整的軟件開發包,以及詳細的C6748系統開發文檔,方便用戶快速評估TMS320C6748處理器、設計系統驅動及其定制應用軟件,也大大降低產品開發周期,讓客戶產品快速上市。主要面向電力、通信、工控、音視頻處理等數據采集處理行業。

TL6748-EVM評估套件是一個功能豐富的開發板,為嵌入式設計人員提供快捷簡單的實踐方式來評估TMS320C674x系列處理器,是一個完整的實驗評估平臺。

tms320c6748下的DSP系統

DSPSS包括C674X核心模塊和幾塊內部存儲器。本章給出了DSPSS的概述和以下幾條相關內容:

·內存映射

·中斷

·電源管理

2.2 TMS320C674X核心模塊

由以下幾部分組成:

·TMS320C674X CPU

·內存控制器:

-1級程序存儲器控制器(PMC)

-1級數據存儲器控制器(DMC)

-2級統一內存控制器(UMC)

-擴展內存控制器(EMC)

-內部直接內存訪問(IDMA)控制器

·內部外設

-中斷控制器(INTC)

-斷電控制器(PDC)

-帶寬管理(BWM)

·高級事件觸發(AET)

2.2.1 內存控制器

C674X核心模塊實現了一個兩級的存儲器架構,其內部存儲器基于緩存,外部存儲器給予支持。1級存儲器(L1)可分成獨立的程序存儲器(L1P)和數據存儲器(L1D)。L1可以通過CPU無延遲地訪問。L2也可以分為L2 RAM(正常可尋址的片上內存)和作緩存外部存儲器位置用的L2緩存。IDMA管理L1P,L1D和L2存儲器之間的DMA。

2.2.2 內部外設

2.2.2.1 INTC

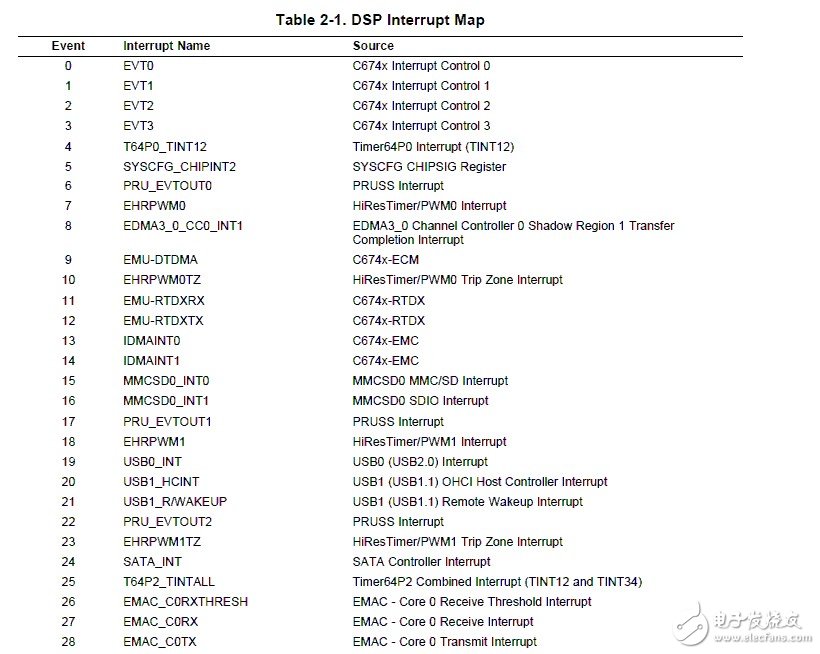

INTC將DSP設備事件映射到12個CPU中斷。所有的DSP設備事件都列舉在下表中了。

2.2.2.1.1 中斷控制寄存器

2.2.2.1.2 NMI中斷

除了表2-1中的中斷,DSP還支持一個特殊的中斷,即不可屏蔽中斷(NMI),這個中斷表現地更像一個異常。NMI中斷受系統配置模塊中的兩個寄存器控制,芯片信號寄存器(CHIPSIG)和芯片信號清除寄存器(CHIPSIG_CLR)。

2.2.2.2 斷電控制器

PDC可以將DSP子系統中的C674X核心模塊和內部存儲器的所有部分斷電,即:

·CPU

·1級PMC

·1級DMC

·2級UMC

·EMC

·IDMA控制器

·L1P存儲器

·L1D存儲器

·L2存儲器

該設備支持C674X核心模塊的靜態斷電特性。

*靜態斷電:PDC接受軟件指令后立即引發整個C674X核心模塊和所有內存的斷電(時鐘門控)。

靜態斷電(時鐘門控)影響C674X核心模塊和內存的所有部分。軟件可以通過控制PDC命令寄存器(PDCCMD)的一個位來引發斷電。

2.2.2.3 BWM

BWM為資源請求程序間的優化帶寬提供一個可編程接口,這些請求包括:

·EDMA3引發的DMA傳輸(并導致一致性操作)

·DSPSS IDMA引發的傳輸(并導致一致性操作)

·可編程緩存一致性操作

-基于塊的一致性操作

-全局一致性操作

·CPU直接引發的傳輸

-數據存取(加載/存儲)

-程序存取

資源包括:

·L1P存儲器

·L1D存儲器

·L2存儲器

·C674X核心模塊意外的資源:外部存儲器,片上外設,寄存器

由于任何的請求都有可能阻塞資源,造成額外時間損失,帶寬管理可以保證所有請求之間的公平。

帶寬管理實現了加權優先級驅動的帶寬分配。再每次傳輸時,每個請求(EDMA3,DSPSS IDMA,CPU等)都分配到一個優先級。在整個系統中可編程優先級都是單一不重復的。一共有9個優先級,0是最高優先級而8是最低的。當有幾個請求對一塊資源產生競爭時,會訪問最高優先級的請求。當競爭發生在連續周期時,競爭計數器會保證低優先級請求在每n次仲裁循環中得到1次訪問,n是可編程的。-1優先級代表一個由于競爭計數器終止而優先級增加的傳輸(不懂?),或者是對特定資源有最高優先級的傳輸。

2.2.2.4 IDMA控制器

IDMA實現C674X核心模塊本地任何兩塊內存位置之間的快速數據塊傳輸。本地內存位置被定義為在L1P,L1D和L2存儲器,或者在外部外設配置(CFG)端口。IDMA不能將數據從內部DSP內存映射寄存器空間傳入或導出。

2.3 內存映射

2.3.1 DSP內部存儲器

2.3.2 外部存儲器

(有關章節會詳細介紹)

2.4 AET

C674X核心模塊支持AET。這一性能可以用來調試復雜問題和理解用戶應用程序的性能特點。AET提供了以下功能:

·硬件程序斷點:指定可以產生事件的地址或地址序列,例如中斷處理器或觸發路徑捕獲。

·數據監視點:指定可以產生事件的數據可變地址,地址序列,或數據值,如中斷處理器或觸發路徑捕獲。

·計數器:為性能監測而計算事件或循環發生次數。

·狀態排序:為復雜序列精確產生事件而允許硬件程序斷點和數據監視點的組合。

結語

關于tms320c6748的相關介紹就到這了,如有不足之處歡迎指正。

-

dsp

+關注

關注

553文章

7987瀏覽量

348745 -

TMS320C6748

+關注

關注

3文章

42瀏覽量

13117

發布評論請先 登錄

相關推薦

【TL6748 DSP申請】廣州創龍TMS320C6748 DSP開發板免費申請試用

【TL6748 DSP申請】基于TMS320C6748高速DSP信號處理模塊設計

TMS320C6748 Fixed/Floating-Poi

TI推出TMS320C6748 DSP與OMAP-L138 DSP+ARM處理器

TMS320C6748固定和浮點DSP硅修訂2.3_2.1_2.0_1.1_1.0_英版

TMS320C6748 TMS320C6748 Fixed/Floating Point DSP

tms320c6748主要參數和原理圖 tms320c6748 IO圖淺析

TMS320C6748和TMS320C6747芯片對比

基于TI TMS320C6748定點/浮點DSP C674x處理器

德州儀器DSP的TMS320C6748技術手冊

使用TPS650061為TMS320C6742、TMS320C6746和TMS320C6748供電

tms320c6748 原理圖 淺談tms320c6748下的DSP系統

tms320c6748 原理圖 淺談tms320c6748下的DSP系統

評論