這篇文章聊一聊輸入輸出(IO)中的輸出。大家都知道IO是芯片跟系統交互的直接路徑,IO做的好與壞系統很容易就能檢測出來。比如輸出無法達到VOH/VOL、輸出波形爬的太慢或者太快、輸出的上升沿或下降沿不對稱等等。輸出特性的好壞更專業的是用如下的眼圖來描述。

圖中的陰影部分表示眼睛,眼睛睜開的越大,表示傳輸特性越好,有機會IC君會好好的研究一下眼圖,先給自己留個作業。

1

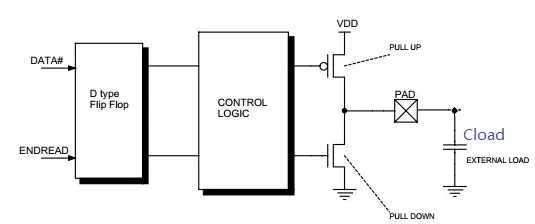

對于中低速的應用而言,比如Flash的數據輸出速度大概是100MHz左右,基本的CMOS輸出電路如下圖所示:

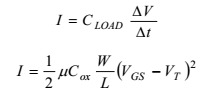

原理也很簡單,輸出“1”的時候,PMOS作為上拉管對Cload進行充電,從0到VOH;輸出“0”的時候,NMOS作為下拉管對Cload進行放電,從VOH到0。根據MOS的充放電電流,假設MOS管一直工作在飽和區(實際平均電流是飽和區和線性區的平均),得到以下公式:

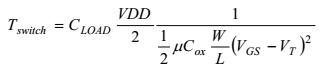

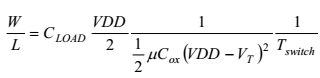

當電壓達到VDD/2時所消耗的時間為:

最終可以得到MOS管子的寬長比如下:

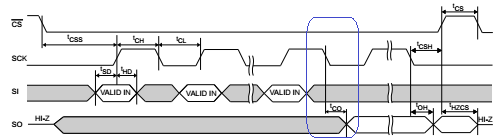

輸出電路的最重要的設計spec通常如下圖藍色框圖所示:

從CLK的某個沿到輸出數據valid的時間 tCO舉個例子 Cload=30pF ,tCO=9ns。

根據這個spec以及上面的公式可以得到PMOS/NMOS的尺寸,再通過hspice來確認自己設計的正確性。當然實際設計要留更多的Margin來cover一些工藝的偏差,還要考慮信號線和電源線的routing,另外在設計中要注意盡量降低數據在切換時候的PMOS/NMOS同時導通的cross bar 電流。

在整個設計過程中,芯片輸出在PCB板上驅動至下一個芯片的路徑看成了一根理想導線,被驅動的芯片作為負載簡化成了Cload。這樣的假設在中低頻的應用中(200Mhz以下)可能問題不大,而且VDD通常也是1.8V或者3V,幅度也比較寬。信號在整個傳輸過程中,不用特別考慮信號完整性的問題。

2

對于高速應用而言,比如DRAM的速度都是Ghz量級的,低功耗DRAM LPDDR4 的VDD電壓幅度為1.1V,而且有越來越小的趨勢。 DRAM的性能趨勢可以參考下圖:

高速應用下芯片輸出在PCB板上驅動至下一個芯片的路徑不能只當作導線,必須考慮信號完整性的問題。

信號完整性大致受到以下2個方面的影響:

傳輸線效應,比如反射;

與通道其他因素的交互,比如串擾和電源線的噪聲。

信號完整性問題和很多因素相關,頻率提高、上升時間減少、擺幅降低、互聯通道不理想、供電環境惡劣、通道之間延時不一致等都可能導致信號完整性問題。但究其根源,主要是信號上升時間減小了。上升時間越小,信號中包含的高頻成分就越多,高頻分量和通道間的相互作用(反射、串擾、電源噪聲等)就可能使得信號產生嚴重的畸變。

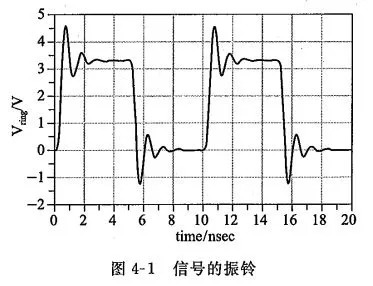

下圖就是由反射引起的振鈴現象:

信號在2個不同阻抗域傳輸的反射系數和傳輸系數:

反射系數為反射電壓和輸入電壓的比值:

Xf =(Z2-Z1)/ (Z1+Z2)

傳輸系數是傳輸電壓和輸入電壓的比值:

Xtran = 2*Z2 / (Z1+Z2)

反射的具體原理有興趣可以找文章末尾的參考書籍閱讀。

從反射系數的公式可以看到,要想消除反射的影響,必須阻抗匹配,也就是Z2=Z1。

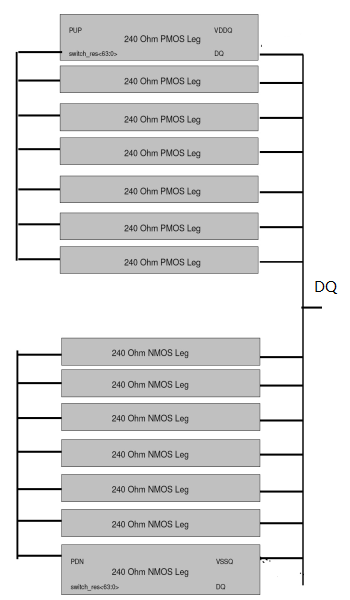

考慮到反射的消除以及輸出上升下降時間的控制,輸出電路的示意圖如下:

上拉由7條240歐姆的PMOS分支構成,具體enable哪幾條可以調整,在DRAM中可以通過模式寄存器控制。比如enable其中3條,那上拉電阻就是3條并聯,最終電阻為80歐姆;下拉也是也是由7條240歐姆的NMOS分支構成,工作原理與上面類似。

有人肯定要問,這個電路就能做到精確的電阻匹配嗎?

答案是不能。

因為我們的芯片在制造過程中會引入工藝的偏差,而且實際使用過程中溫度電壓也不一樣,那怎么辦呢?

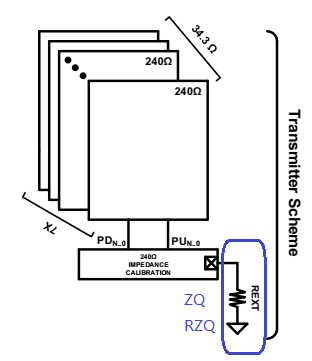

引入校準機制,校準之后就可以得到相對精確的阻抗。首先要引入一個精確外部電阻作為標準,不然后續的校準基礎都是錯誤的。

DRAM引入了ZQ pin, 這個pin 外接了一個精確的電阻240歐姆。DRAM在上電之后就會進行ZQ 校準,校準出系統需要的阻抗,傳遞給所有的輸出pin。

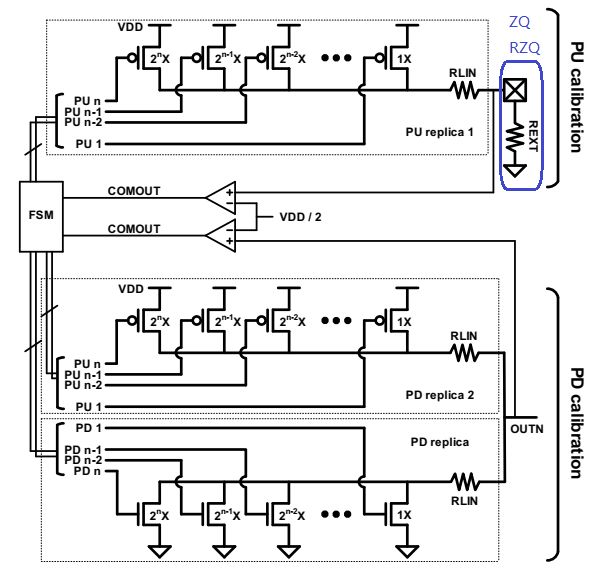

電路示意圖如下圖所示:

每一個分支的具體電路示意圖如下:

可以看出,每一個分支是由一堆并聯的PMOS或者NMOS,再串聯一個電阻RLIN得到。我們的目標就是將這個分支精確匹配到240歐姆。

從MOS管的IV特性得出MOS管的等效阻抗其實不是線性的,希望阻抗得到精確匹配,就不能完全用MOS來作為等效電阻。

串聯電阻RLIN可以取一個比較大的值,比如100歐姆,那剩下的MOS就要匹配240-100=140歐姆的電阻。可以通過PU1 PU2 ... PUN來確定到底開多少個MOS管,然后用分壓去跟VDD/2去作為比較,根據比較結果動態調整PU[5:1]的值。通常這里用的是逐次逼近SAR算法,這個算法也蠻有意思的,ADC中也經常會用到,IC君會在后續的文章中研究,又留一次作業。

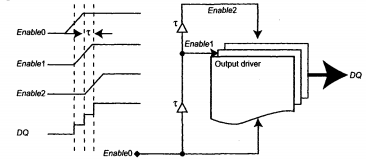

說完電阻匹配,再來聊一聊信號的上升下降沿的時間(斜率)控制。輸出信號的斜率可以通過打開分支的時間來控制,示意圖如下:

逐步打開分支,使得輸出DQ信號的斜率相對緩慢的上去。

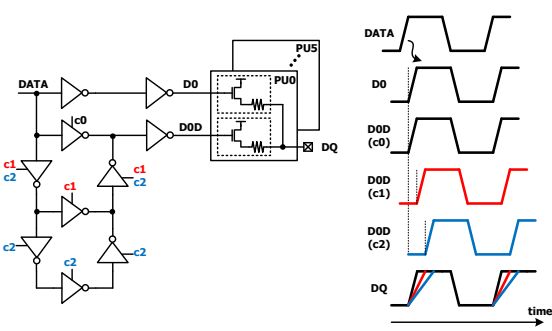

同時我們還可以在分支內部做精細的控制,示意圖如下:

把MOS的gate控制信號進行延遲,可以通過C0、C1、C2這3條路徑得到不同的D0D。D0D驅動的DQ與D0驅動的DQ疊加,調整最終DQ的斜率。

3

從低頻到高頻,對于CMOS類型的輸出電路設計而言,基本的原理其實差不多。但是高頻需要考慮信號完整性的問題,電路也因此變得更復雜。

-

DRAM

+關注

關注

40文章

2351瀏覽量

185737 -

FlaSh

+關注

關注

10文章

1679瀏覽量

151988 -

輸出電路

+關注

關注

0文章

79瀏覽量

16193

原文標題:從低速Flash到高速Dram,輸出電路設計的不同點

文章出處:【微信號:icstudy,微信公眾號:跟IC君一起學習集成電路】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

評論