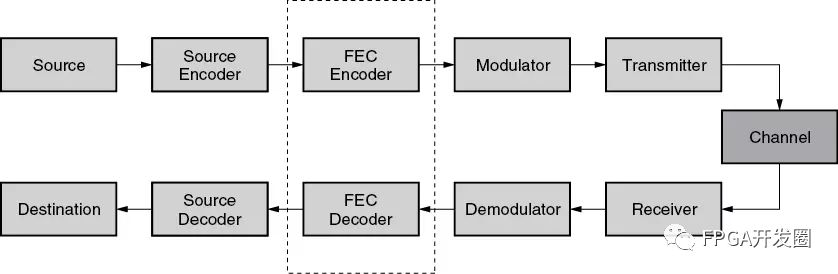

無論是無線還是有線數據通信,保持傳輸可靠性都是高質量解決方案的基本要求。此類系統的關鍵構成部分在于高性能軟判決前向糾錯 (SD-FEC) 功能,發送(編碼器)和接收(解碼器)路徑都需要這個功能。

圖 1:典型的數據通信系統

隨著數據帶寬的不斷提升,例如 5G 新無線電 (5G NR) 技術和有線電纜數據服務接口規范 3.1 (DOCSIS 3.1),上述系統對數據吞吐量要求極高,因此,SD-FEC 塊必須實現高效處理。

賽靈思推出業界首款可配置集成型 (SD-FEC) IP 塊

此類 SD-FEC 功能通常在高性能 FPGA 的可編程邏輯中實現。隨著為了支持數千兆位速率而進一步推進系統要求,性能、功耗和成本均成為了關鍵設計因素。相對于集成型解決方案而言,上述功能的軟實現不盡人意。

因此,賽靈思推出了業界首款可配置集成型 SD-FEC IP 塊,可實現:

緩解性能和吞吐量瓶頸 → 約 3 Gb/s 的峰值 LDPC 解碼吞吐量

大幅降低資源需求 → 每個 SD-FEC 實例減少約 10 萬 LUT

大幅降低功耗 → 轉向集成型解決方案,功耗降低 80%

圖 2:集成型 SD-FEC 與軟 LDPC 解碼器的功耗對比

采用 SD-FEC 功能集成成果的應用實例

如前所述,類似于 ASIC 的 SD-FEC 塊相對于軟實現而言能提高吞吐量,降低時延,并降低功耗。由于能夠為 Turbo 解碼的長期演進發展 (LTE) 以及 LTE-A 應用提供支持,因此構成了 4G 和 5G 前系統的低功耗解決方案。

利用低密度奇偶校驗 (LDPC) 對解碼和編碼的支持,我們能夠為無線市場的 5G 基帶和回傳平臺等應用提供支持。除 Zynq UltraScale+ RFSoC (ZU28DR) 系列中的 RF-ADC/DAC 之外,SD-FEC 還為 DOCSIS 3.1 標準的遠程 PHY 提供了極富吸引力的解決方案。

如需了解賽靈思 Zynq UltraScale+ RFSoC 中的集成型 SD-FEC 以及如何利用其功耗和吞吐量優勢的更多詳情,歡迎花上 10 分鐘的時間點擊“閱讀原文”,閱讀以下白皮書,該白皮書簡述了塊級功能和優勢。

-

編碼器

+關注

關注

45文章

3646瀏覽量

134647 -

數據通信

+關注

關注

2文章

431瀏覽量

33778

原文標題:實現更低功耗的更高吞吐量 —— Xilinx業界首款可配置集成型 SD-FEC

文章出處:【微信號:FPGAer_Club,微信公眾號:FPGAer俱樂部】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

賽靈思低溫失效的原因,有沒有別的方法或者一些見解?

新思科技推出業界首款連接大規模AI加速器集群的超以太網和UALink IP 解決方案

英飛凌推出業界首款用于太空應用的QML認證512 Mbit抗輻射加固設計NOR閃存

英飛凌推出業界首款太空級NOR Flash

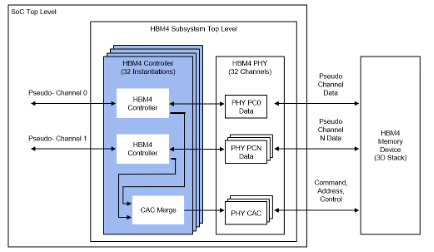

Rambus推出業界首款HBM4控制器IP

Rambus宣布推出業界首款HBM4控制器IP,加速下一代AI工作負載

賽靈思推出業界首款可配置集成型(SD-FEC) IP塊

賽靈思推出業界首款可配置集成型(SD-FEC) IP塊

評論