在電路系統的單板設計中我們經常用到各種電源,DC/DC是最廣泛的一種,比如BUCK降壓電路,一般我們都采用的是相關廠家的集成芯片如TI、ADI、Linear等,總的來說應用還是比較簡單的,按照參考電路配置外圍器件即可,然后按照布局布線原則完成單板設計。但是如果僅僅是知道基本原理卻不知所以然,導致的結果就是在出現問題時完全摸不著頭腦,比如最近遇到一個問題就是DC/DC在空載時電壓異常的現象。

這個問題是偶然出現的:該芯片已在其他單板上使用正常,但是最新的一塊板子卻出現電壓異常波動。對比二者原理圖發現都一樣,但是檢查完PCB后檢查原理圖發現輸出電容配置有問題,改過電容后電壓正常。那么為何同樣的設計之前的沒有問題,現在的有問題呢?進一步發現,新的問題板子在未使用時是空載的,而之前的板子都是一直帶載,于是不改變電容插上負載,輸出電壓也正常了。這是一個典型的開關電源的環路響應問題。我們在學習運放的時候就研究過運放的閉環反饋特性,也就是幅頻特性和相頻特性。

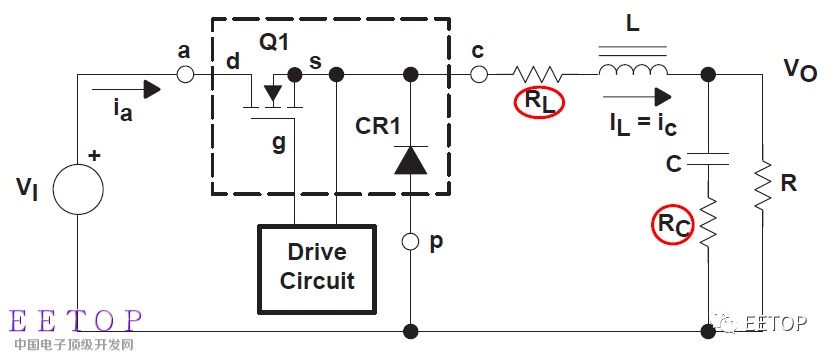

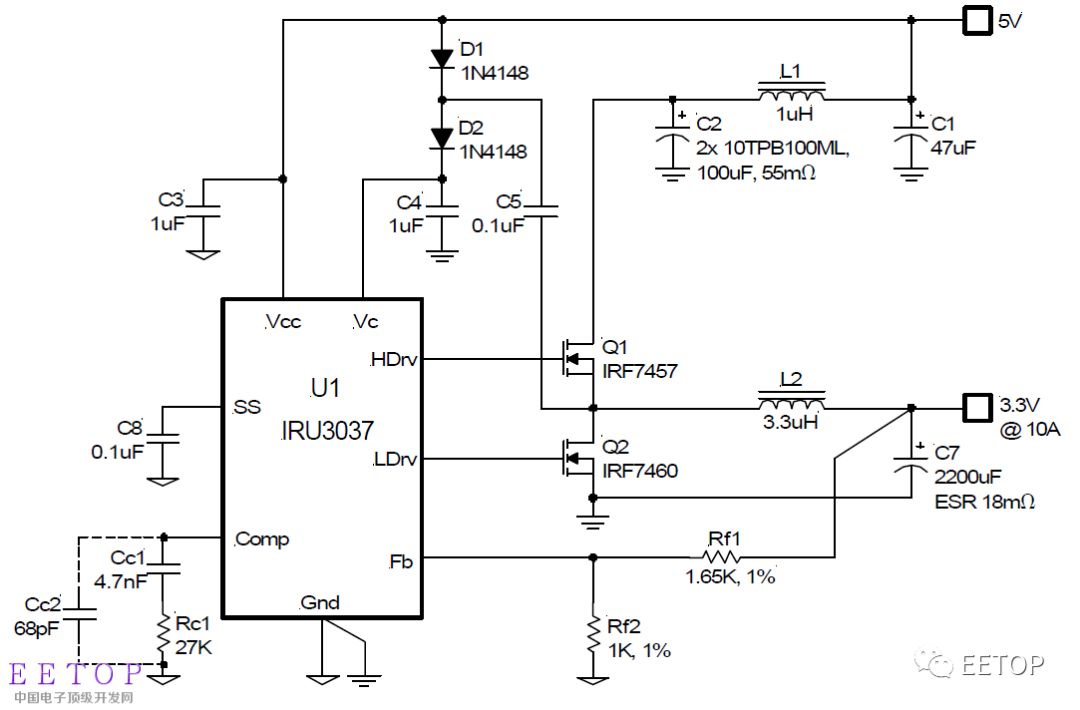

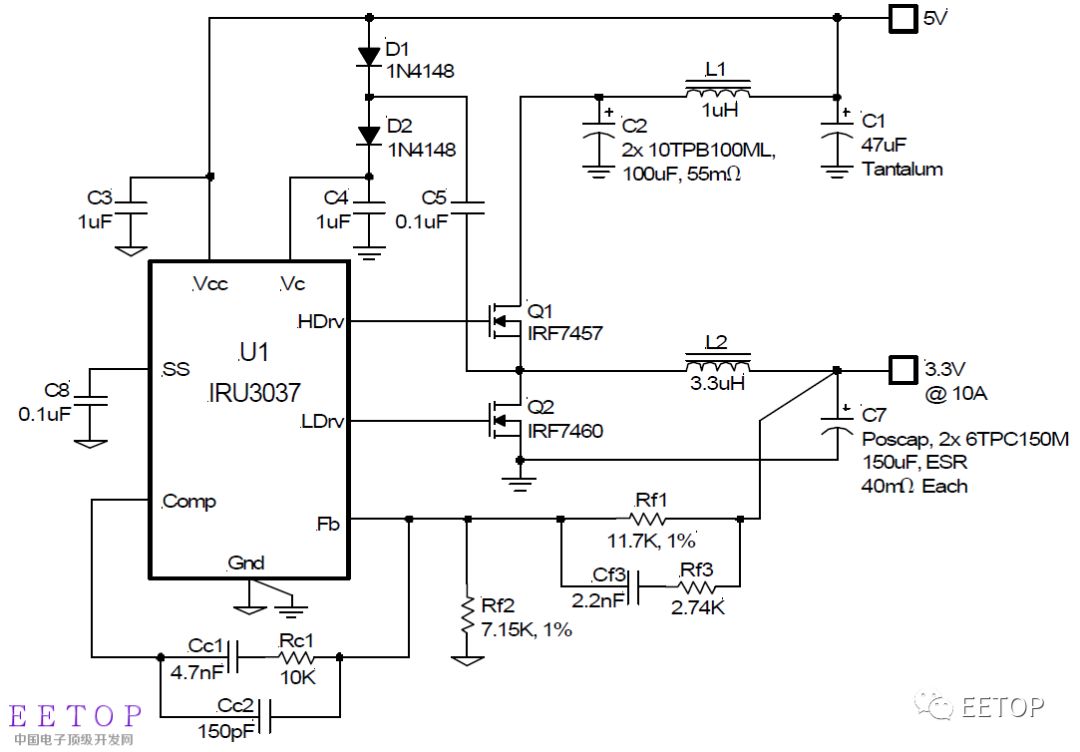

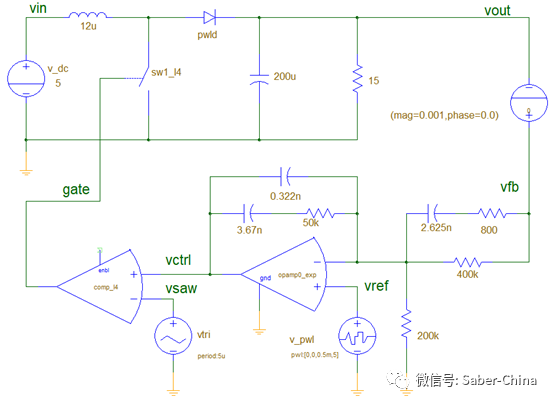

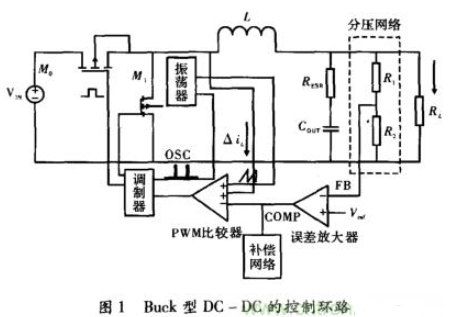

那么對于DC/DC而言,環路同樣具有類似特性,下圖是一個同步BUCK電路。

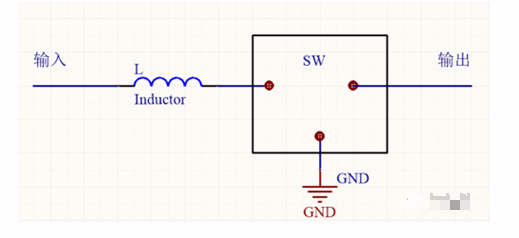

基本的傳輸拓撲為:

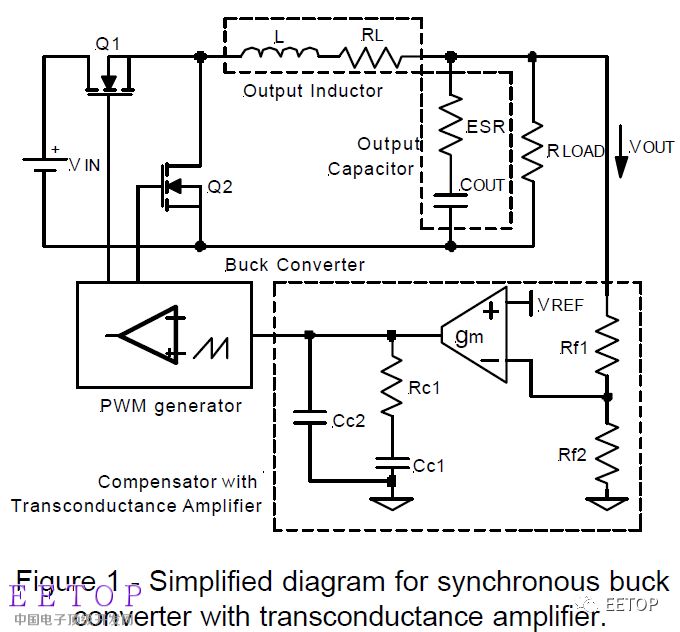

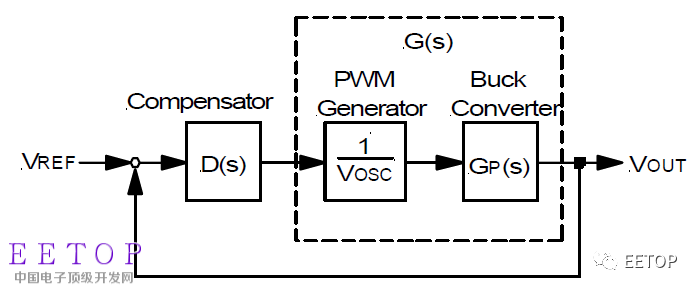

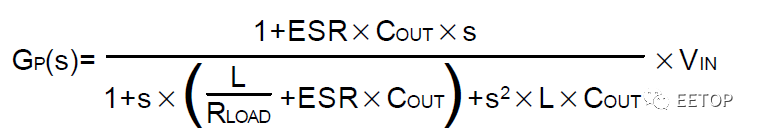

傳輸函數可簡化為下圖,S為頻率參數。

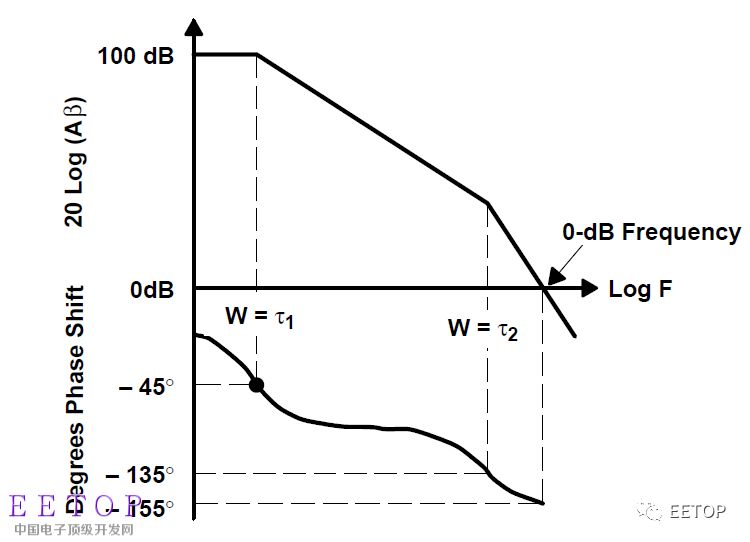

對于BUCK電路而言,我們可以得到輸出的零極點分析

LC為環路的主極點,而輸出電容和ESR則為環路的一個零點。

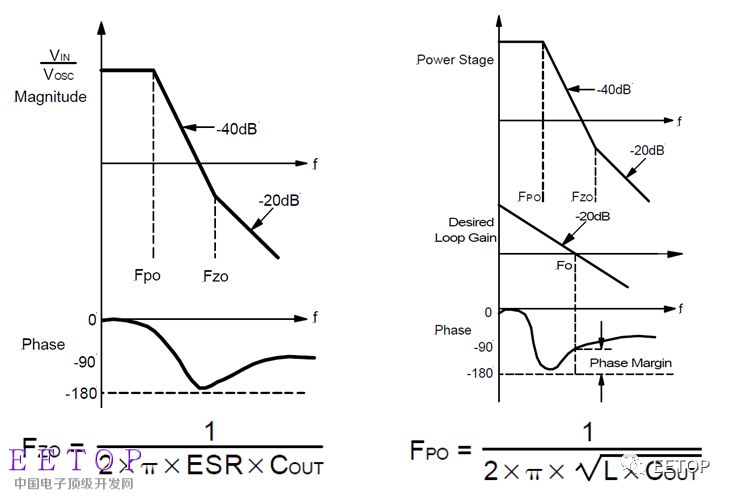

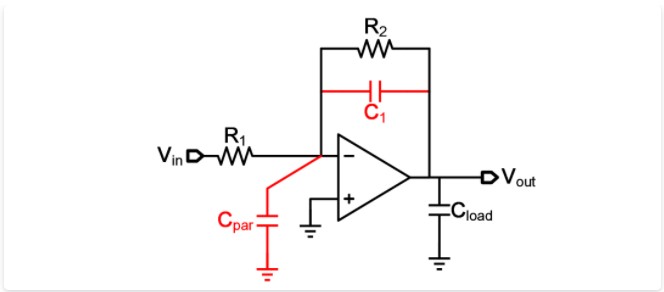

我們知道如圖的相位裕度是反映環路穩定性的重要指標,因此環路設計中重要的就是如何保證合適的參數。下面就介紹幾種補償方式,目的是前推零點,提高相位裕度。

我們由極點公式看到L和Cout決定了環路的帶寬,這個參數其實也代表著環路的響應速度。

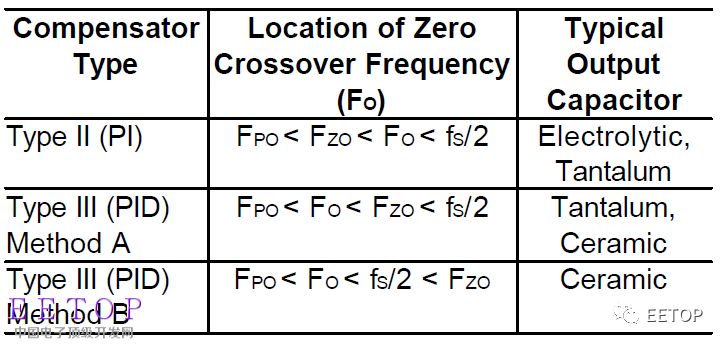

Fs是開關電源的頻率,那么電源設計中就需要進行補償設計。

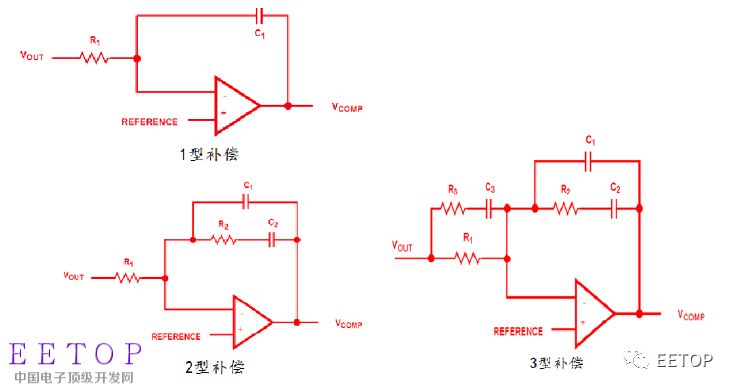

兩種補償方式,具體的計算公式就不貼了。

PI方式:

PID方式:

我們非電源單板硬件設計中考慮環路補償的情況比較少,實際應用中我們按照推薦的參數設計一般沒有問題,但是像這次遇到的這種設計錯誤時,能夠從輸出電壓的特性上判斷出可能的原因,輸出電容設計錯誤導致環路異常出現電壓波動,而帶載同樣影響了環路,因此在設計錯誤的情況下同樣正常工作。總之環路的頻率特性與環路的響應、噪聲等相關,我們在遇到問題時最好能夠從一定基礎角度出發才能盡快解決問題,是以為記。

-

降壓電路

+關注

關注

13文章

168瀏覽量

59520 -

電路系統

+關注

關注

0文章

69瀏覽量

12921

原文標題:硬件開發者之路--簡單理解DC/DC的環路穩定性問題

文章出處:【微信號:eetop-1,微信公眾號:EETOP】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

開關電源環路穩定性分析(一)

電阻型放大電路的穩定性問題

如何在SaberRD中評估閉環DC-DC升壓變換器的環路穩定性?

環路增益的穩定性

開關電源環路穩定性測量問題

電源環路穩定性評價方法

做了一個接收機電路性能出了穩定性問題是什么原因?怎么解決?

一個穩定性高的DC/DC 電源模塊

淺析環路穩定性原理與DCDC Buck環路穩定性

環路穩定性主要技巧與經驗

電流模Buck型DC—DC環路穩定性分析

環路穩定性原理與DCDC Buck環路穩定性

淺析DC/DC的環路穩定性問題

淺析DC/DC的環路穩定性問題

評論