摘要:

工程應用中,在對模糊圖像處理時,由于空域去卷積的方式難度較大,通常對圖像進行頻域變換后,在頻域中進行相關(guān)的處理與實現(xiàn)。針對圖像去模糊系統(tǒng)的頻域處理硬件資源消耗大、轉(zhuǎn)換靈活性差、處理時間長等問題,以DE2開發(fā)板為硬件平臺,結(jié)合模糊圖像及去模糊算法特點,采用輸入數(shù)據(jù)預處理、原位計算、拋位、流水線結(jié)構(gòu)、并行處理等方式設(shè)計實現(xiàn)了一種針對圖像去模糊系統(tǒng)的頻域處理方式。實驗數(shù)據(jù)顯示,方法對圖像數(shù)據(jù)頻域處理的精確度始終保持在98.5%以上,硬件資源僅用了9 162個邏輯單元。實驗結(jié)果表明,所設(shè)計的系統(tǒng)在處理精度及資源利用上優(yōu)于其他同類系統(tǒng)。

0 引言

隨著電子技術(shù)的發(fā)展,嵌入式系統(tǒng)在圖像處理領(lǐng)域的應用越來越廣,但相關(guān)芯片卻有明顯不足:ASIC芯片開發(fā)周期長、成本高、靈活性差;DSP和ARM的串行結(jié)構(gòu)難以滿足圖像的實時處理要求等。然而,FPGA融合了DSP和ASIC等芯片的優(yōu)點,具有靈活的配置方式,因易于實現(xiàn)并行處理功能和流水線工作方式,使得FPGA在圖像處理領(lǐng)域具有更高的應用價值[1]。

由于在空域中對模糊圖像的模糊核估計手段有限,且處理精度不高,故大多采用頻域轉(zhuǎn)換的方式,在頻域中對模糊圖像進行處理。頻域轉(zhuǎn)換的硬件實現(xiàn)通常采用直接調(diào)用IP核或設(shè)計通用的信號頻域轉(zhuǎn)換器等方法,這樣不僅在硬件資源消耗和處理效率上大打折扣,而且沒有充分利用模糊圖像及去模糊算法的特點來減少資源利用及處理時間。

本文結(jié)合模糊圖像及頻域去模糊算法的特點,采用圖像數(shù)據(jù)預處理、原位計算、拋位、流水線處理等方法,設(shè)計實現(xiàn)了一種針對圖像去模糊系統(tǒng)的頻域處理方法。相比其他同類頻域處理方法,其具有資源利用率高、硬件實現(xiàn)簡單、針對性強等特點。

1 系統(tǒng)總體設(shè)計

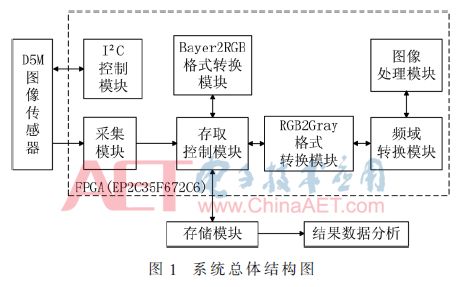

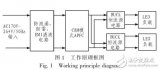

系統(tǒng)以DE2開發(fā)板為開發(fā)平臺,以Altera的EP2C-35F672C6型號的FPGA芯片為核心處理單元,采用TRDB-D5M圖像傳感器進行圖像數(shù)據(jù)采集。系統(tǒng)總體結(jié)構(gòu)設(shè)計如圖1所示。

圖像傳感器通過DE2平臺的通用輸入輸出口與FPGA連接,F(xiàn)PGA通過I2C控制模塊對其進行寄存器及工作方式的設(shè)定[2]。圖像傳感器獲得Bayer圖像數(shù)據(jù)流后,通過格式轉(zhuǎn)換處理,將其轉(zhuǎn)換成RGB數(shù)據(jù)。由于圖像傳感器工作時,內(nèi)部各部分的時鐘頻率不同,為了使采樣與顯示協(xié)調(diào)一致,加入SDRAM存儲模塊對采集的圖像信息進行緩存,SDRAM以四端口的形式存取數(shù)據(jù),四個端口中兩個為寫端口,兩個為讀端口,使系統(tǒng)的讀取效率提高了一倍。數(shù)據(jù)存入存儲模塊的同時,將圖像數(shù)據(jù)送至RGB2Gray格式轉(zhuǎn)換模塊,在該模塊中完成圖像從彩色圖像到灰度圖像的轉(zhuǎn)換,接著傳送至頻域轉(zhuǎn)換模塊,完成圖像的頻域變換,最后傳送至圖像處理模塊,對模糊圖像進行去模糊預處理后,存入存儲模塊,通過MATLAB平臺對處理結(jié)果進行分析驗證。

2 核心模塊設(shè)計

2.1 圖像灰度變換模塊設(shè)計

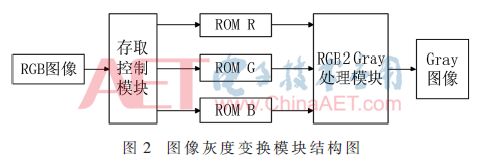

考慮到直接對彩色圖像進行頻域轉(zhuǎn)換時,需分三通道對圖像進行存儲及處理,故本文在對圖像頻域處理前加入灰度變換模塊,既不損壞圖像信息,又減少了數(shù)據(jù)量及存儲空間。

從存儲模塊中提取采集到的圖像信息,加入一個存取控制模塊,控制將要讀取的圖像數(shù)據(jù)的地址。利用QuartusII創(chuàng)建ROM IP核,并將彩色圖像數(shù)據(jù)分R、G、B 3個顏色通道存儲在ROM中,根據(jù)式(1)彩色圖像轉(zhuǎn)換成灰度圖像的算法公式,設(shè)計RGB2Gray處理模塊。結(jié)構(gòu)圖如圖2所示。處理完成后,將灰度圖像數(shù)據(jù)存儲在存儲模塊,待后面處理時讀取即可。

2.2 一維FFT模塊設(shè)計

在進行一維FFT設(shè)計時,本文采用按頻率抽取(DIF)的FFT算法。由于各蝶形運算的輸入與輸出互不重復,任何一個蝶形的兩個輸入量經(jīng)蝶形運算后可以實現(xiàn)同址運算。這種原位運算方式節(jié)省了大量的存儲單元,降低了硬件資源的使用成本[4]。

本文參照CORDIC算法對蝶形運算單元進行設(shè)計,目的是充分利用FPGA的流水線結(jié)構(gòu),提高蝶形運算單元的處理速度。另外,考慮到數(shù)據(jù)在頻域轉(zhuǎn)換后主要對頻譜中的亮條信息進行處理分析,故在蝶形運算單元中加入了拋位運算,這樣既對模糊圖像有效信息未造成影響,在資源消耗及處理速度上也進一步得到優(yōu)化。

基-2FFT設(shè)計主要由存儲單元、M(log2N,N為FFT輸入序列的長度)級蝶形運算單元、倒位序轉(zhuǎn)為順序單元等部分組成,總體結(jié)構(gòu)如圖3所示。在模塊輸入時序的控制下,將待處理的數(shù)據(jù)流輸入到模塊中,通過數(shù)據(jù)流水線模塊的控制,將有效數(shù)據(jù)按設(shè)定時鐘依次輸入到(M-1)級蝶形運算單元中,直到完成最后一級的蝶形運算后(最后一級無乘法器),經(jīng)過順序排序單元,即可將輸出的倒位序數(shù)據(jù)按自然順序輸出到存儲單元中。其中,為了保證資源的有效利用,且不影響算法的有效性,在順序排序單元的設(shè)計中,本文設(shè)置了兩個存儲單元,既能保證數(shù)據(jù)流水線輸入,又能避免在順序排序單元的工作過程中出現(xiàn)數(shù)據(jù)交叉讀取的問題。

2.3 二維FFT模塊設(shè)計

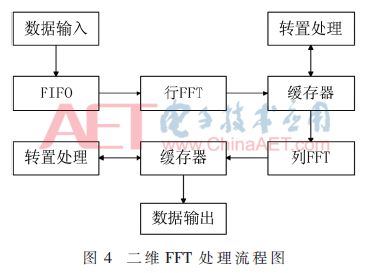

由于傅里葉變換具有可分性的性質(zhì),處理圖像的傅里葉變換時,通常將二維變換通過降維的方式轉(zhuǎn)化為行和列的一維傅里葉變換。首先將圖像數(shù)據(jù)以行為單位,依次進行行方向的一維傅里葉變換,待行方向數(shù)據(jù)處理完畢后,對結(jié)果矩陣進行轉(zhuǎn)置處理,將處理后的數(shù)據(jù)再次進行傅里葉變換[6]。本文設(shè)計的二維FFT處理模塊如圖4所示,由于FFT處理速率與圖像輸入速率不匹配,故將圖像數(shù)據(jù)經(jīng)過FIFO緩存模塊后,以數(shù)據(jù)流的模式進行行FFT處理。接著將處理結(jié)果存儲在緩存器中,在存儲器內(nèi)進行數(shù)據(jù)的交換,完成矩陣轉(zhuǎn)置處理。對轉(zhuǎn)置后的矩陣再次進行FFT處理,同樣將結(jié)果存儲在緩存器模塊中,重復之前的轉(zhuǎn)置處理后,將結(jié)果送入到FIFO模塊,輸出結(jié)果即為圖像的二維FFT處理結(jié)果。在圖像的二維FFT處理中,行FFT和列FFT處理模塊結(jié)構(gòu)完全相同,只需在處理過程中加入轉(zhuǎn)置算法及所需的存儲模塊。

由于FPGA均以定點數(shù)的形式對數(shù)據(jù)進行處理,本文將行(列)數(shù)據(jù)進行了如式(2)所示的算法處理,將兩行(列)數(shù)據(jù)以復數(shù)形式轉(zhuǎn)化成一組數(shù)據(jù),這樣在進行FFT處理時,使處理速度提高了一倍[3],結(jié)合相應的換算,對應的輸出可用式(3)、式(4)表示。

2.4 去模糊算法簡述

空域中,在忽略加性噪聲的情況下,模糊圖像可轉(zhuǎn)化成清晰圖像與模糊核的卷積過程。將空域轉(zhuǎn)換到頻域,卷積問題就變成了相乘問題,去模糊的核心就是對模糊尺度和方向的估計。對模糊圖像進行頻域轉(zhuǎn)換后,圖像的模糊核信息主要集中在頻譜的亮條中[7]。借助相關(guān)算法將亮條信息進行提取,即可得到模糊圖像的像素偏移角度和偏移距離,從而實現(xiàn)圖像的去模糊。

3 系統(tǒng)測試

完成系統(tǒng)各模塊設(shè)計之后,在QuartusII環(huán)境下使用Programmer軟件,將圖像采集與顯示模塊的工程文件下載到FPGA中。系統(tǒng)圖像采集效果如圖5(a)所示。從測試結(jié)果可以看出系統(tǒng)實時圖像采集正常,條紋、細線等細節(jié)顯示清晰,畫面穩(wěn)定,功能完全符合設(shè)計要求。采集的圖像大小為320×240。

為了便于對系統(tǒng)處理結(jié)果進行分析比較,本文在MATLAB中,創(chuàng)建了一個運動位移為30像素、運動角度為10°的點擴散函數(shù)(PSF),使用PSF對采集的圖像進行卷積操作,得到一幅簡單運動模糊圖像,如圖5(b)所示。

將經(jīng)模糊處理后的圖像數(shù)據(jù)輸入到灰度變換模塊,將彩色圖像分R、G、B三通道分別存儲,接著進行相應算法處理后,即得到灰度圖像,將結(jié)果數(shù)據(jù)在MATLAB讀出,結(jié)果如圖5(c)所示。

在FFT處理模塊的工程設(shè)計中,使用Verilog HDL語言對該設(shè)計模塊進行了行為級描述。以Altera DE2開發(fā)板的EP2C35F672C6為目標芯片,在Quartus II平臺上進行綜合、布局、布線。硬件器件使用報告顯示此設(shè)計資源占用較少,僅用了9 162個邏輯單元,使用了73個引腳。

為了便于對圖像進行FFT處理,將一行256點的數(shù)據(jù)輸入到FFT模塊,在經(jīng)過9級蝶形運算單元后,對結(jié)果數(shù)據(jù)輸入到順序排序模塊重新按自然順序排序后,即可得到FFT處理結(jié)果。

在Modelsim環(huán)境下編寫Testbench文件,對FFT模塊進行仿真測試。由仿真結(jié)果可知,在旋轉(zhuǎn)因子片選(rTwiCsEp)和寫脈沖(rTwiWrEp)有效的情況下,將旋轉(zhuǎn)因子(rTwiCoe)存入到FFT模塊。待旋轉(zhuǎn)因子輸入完畢后,數(shù)據(jù)輸入使能為高,開始輸入待處理數(shù)據(jù)(rSrcFFT)。等到輸入數(shù)據(jù)達到所設(shè)定的存儲容量后,輸出使能(rFftOutEn)變?yōu)楦撸_始輸出FFT處理結(jié)果(fftout)。每當幀有效(frmval)給一個信號脈沖時,證明將輸出一行(列)數(shù)據(jù),待一整行數(shù)據(jù)輸出完成后,將給下一個信號脈沖,形成流水線處理模式。具體時序如圖6所示。從仿真波形看,時序符合預期設(shè)計。

4 系統(tǒng)分析

待圖像數(shù)據(jù)完成二維FFT處理后,將生成的結(jié)果數(shù)據(jù)通過MATLAB軟件讀出,將之與通過MATLAB的fft2函數(shù)處理后的結(jié)果進行對比,如圖7所示,結(jié)果是一致的。由圖可知,經(jīng)本文設(shè)計的頻域處理算法處理后的數(shù)據(jù)保留了模糊圖像的有效信息。

從兩種方式處理的功率譜看,輪廓基本一致,少許差別的原因在于本文設(shè)計算法采用了塊浮點及針對去模糊系統(tǒng)使用的數(shù)據(jù)拋位方法,而MATLAB采用的是純浮點的處理方法。功率譜如圖8所示。

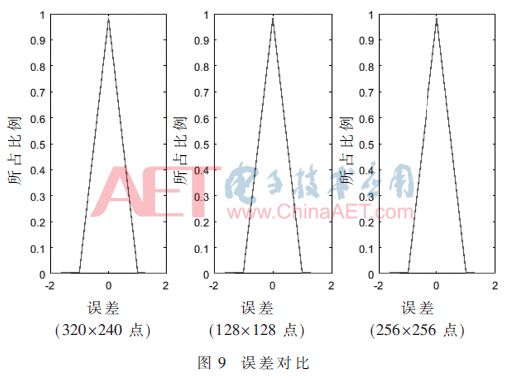

對經(jīng)本文設(shè)計的頻域處理方法得到的結(jié)果與經(jīng)MATLAB直接調(diào)用fft2得到的結(jié)果進行對比,統(tǒng)計對應像素點的絕對誤差,結(jié)果如圖9所示。從圖可得,在不考慮定點與浮點數(shù)據(jù)處理方式的影響下,本文設(shè)計的頻域處理方式在128×128點、256×256點和320×240點不同點數(shù)環(huán)境下的處理精度都保持在98.5%以上。

5 結(jié)論

頻域處理對于圖像去模糊系統(tǒng)的性能起著極重要的作用。本文針對去模糊系統(tǒng)在頻域處理的硬件實現(xiàn)中遇到的資源利用高和處理精度低等問題,設(shè)計完成了一種基于FPGA的流水線型結(jié)構(gòu)的頻域處理方法。從實驗結(jié)果及分析可見,相比于FPGA自帶的IP核及其他處理方法,該方法在圖像去模糊系統(tǒng)的頻域處理,結(jié)合圖像數(shù)據(jù)和模糊信息的特點,在頻域處理的設(shè)計上降低了存儲消耗,提高了處理速度,具有一定的工程價值與參考意義。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603005 -

圖像傳感器

+關(guān)注

關(guān)注

68文章

1897瀏覽量

129527 -

數(shù)據(jù)采集

+關(guān)注

關(guān)注

38文章

6053瀏覽量

113622

原文標題:【學術(shù)論文】圖像去模糊系統(tǒng)的頻域處理改進方法

文章出處:【微信號:ChinaAET,微信公眾號:電子技術(shù)應用ChinaAET】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

求一種CCD圖像采集處理系統(tǒng)的設(shè)計方法

一種用于植物細胞的顯微圖像處理系統(tǒng)

一種基于HVS的模糊控制圖像水印算法

一種新的模糊系統(tǒng)建模方法研究與應用

一種改進的模糊變換靜脈圖像增強方法

一種改進的模糊變換靜脈圖像增強方法

新結(jié)構(gòu)重心法去模糊單元電路設(shè)計

基于LO正則化去模糊算法

一種廣義運動模糊模型

基于尺度迭代深度神經(jīng)網(wǎng)絡(luò)的圖像去模糊算法

一種多粒度融合的模糊規(guī)則系統(tǒng)圖像特征學習算法

基于深度學習的圖像去模糊算法及應用

去模糊算法適對發(fā)射點擴散函數(shù)(PSF)的假設(shè)要求最低

一種針對圖像去模糊系統(tǒng)的頻域處理方法

一種針對圖像去模糊系統(tǒng)的頻域處理方法

評論