許多中等規(guī)模的可編程邏輯器件(PLD)設(shè)計,特別是控制方面的應(yīng)用,通過片上總線互聯(lián)一些接口至微處理器,這些微處理器可以是片上芯片或外部的。雖然每個接口往往是相對簡單的,構(gòu)建所有片上的互連和對它們進(jìn)行調(diào)試的任務(wù)可能會非常耗時和令人沮喪。越來越多的設(shè)計人員使用預(yù)設(shè)計的基于處理器系統(tǒng)的開發(fā)板來加快開發(fā)過程。

這種方法有幾個好處。首先,沒有必要裝配許多IP或構(gòu)建選擇的IP至片上總線的緩沖。此外,片上總線結(jié)構(gòu)不需要選擇和構(gòu)建。第二是沒有必要手工連接各種IP至片上總線。即使是本文中討論的相對較小的設(shè)計,使用約1000個查找表(LUT),對于頂層的連接大約需要300行的 Verilog代碼。第三,使用這種方法構(gòu)建硬件的時間大大減少。設(shè)計人員可能需要花數(shù)天時間來組成基本的硬件部分,并進(jìn)行所有重要的接口調(diào)試。一旦調(diào)試接口工作使設(shè)計已經(jīng)處于穩(wěn)定狀態(tài),添加或刪除接口就變得非常簡單。此外,如果修改設(shè)計導(dǎo)致調(diào)試接口失敗,很容易返回到最近所知的成功設(shè)計版本。

典型的開發(fā)板

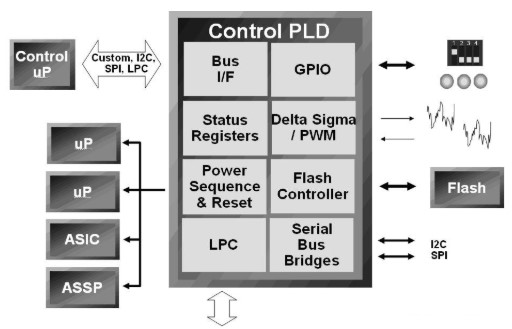

這里以開發(fā)環(huán)境為實例,允許設(shè)計人員用預(yù)先設(shè)計的系統(tǒng)作為起點,然后修改它來構(gòu)建自己的樣機,在將它移植到最終的系統(tǒng)之前使用萊迪思的MachXO迷你開發(fā)板。雖然適用于許多應(yīng)用場合,這個電路板最適用于控制設(shè)計,這種設(shè)計往往用小型的非易失可編程邏輯器件來實現(xiàn)。圖1說明了典型的用可編程邏輯器件實現(xiàn)控制應(yīng)用的功能。

圖1用可編程邏輯器件實現(xiàn)的典型控制功能

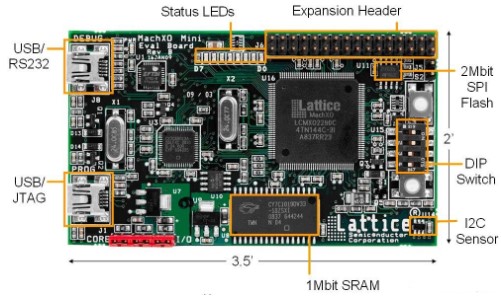

迷你開發(fā)板的中心是MachXO2280非易失、基于閃存的擁有2280個LUT邏輯實現(xiàn)的可編程邏輯器件。圖2展示了MachXO迷你開發(fā)板,并對主要接口加了注釋。這個電路板提供五種主要的功能:

1、通過發(fā)光二極管組、擴(kuò)展端、DIP開關(guān)和按鈕開關(guān)提供GPIO和狀態(tài)指示器。

2、 SPI閃存和I2C溫度傳感器用作這些常用串行接口的例子。

3、SRAM內(nèi)存提供了額外的便箋式存儲器。

5、通過USB的JTAG用作對器件編程的接口。

對于開發(fā)過程而言,通過USB接口至RS232的方式和通過USB至 JTAG的方式是至關(guān)重要的。利用這兩個小的“B”型的USB連接器,可以通過電纜連接到任何個人電腦的USB接口。一旦加載適當(dāng)?shù)尿?qū)動程序(適用于Windows XP及更高版本),通過USB接口至JTAG的方式允許萊迪思的ispVM軟件對所需修改設(shè)計的MachXO進(jìn)行編程。采用相應(yīng)的驅(qū)動程序,通過USB接口至RS232的方式對通過USB至RS232的方式進(jìn)行仿真。驅(qū)動程序包括Linux的最新版本,也可用于Windows XP及更高版本。串行端口只作為主機的“COM”端口。此接口為片上設(shè)計提供了一個簡便的方法,用于發(fā)送狀態(tài)及適當(dāng)修改、調(diào)試信息至主處理器。

圖2 MachXO迷你開發(fā)板

預(yù)測試的片上系統(tǒng)設(shè)計

迷你開發(fā)板加速開發(fā)的關(guān)鍵是采用預(yù)開發(fā)的,預(yù)加載的片上系統(tǒng)(SOC)設(shè)計,可以作為用PLD實現(xiàn)控制功能的起點。下面是一個典型的開發(fā)流程和相關(guān)的時間,假設(shè)相應(yīng)的軟件工具和驅(qū)動程序已被加載至PC主機:

1、驗證硬件和接口的正常運行如所期望的那樣。(通常為5分鐘。)此刻設(shè)計人員已經(jīng)了解了硬件情況。

2、確認(rèn)可以使用ispVM編程軟件將FPGA配置文件再次載入MachXO。 (通常為5分鐘。)

3、使用ispLEVER設(shè)計軟件重新編譯設(shè)計,并確認(rèn)所產(chǎn)生的配置如預(yù)期的情況工作。 (通常為10分鐘。)此時,設(shè)計者有一個已知的良好起點。

4、首先修改設(shè)計,重新編譯并加載新的配置。(通常是60分鐘,但實際的時間取決于所修改的量。)

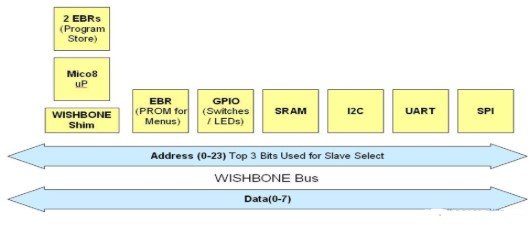

按照這個開發(fā)流程,初始開發(fā)需要幾個星期的時間可以減少到數(shù)小時。SoC設(shè)計的概況如圖3所示。可以看到設(shè)計由六個接口和一個微處理器組成,并通過一個片上總路線聯(lián)在一起。

圖3 MachXO迷你板預(yù)裝載了SOC設(shè)計

這個設(shè)計的中心是片上總線。使用WISHBONE標(biāo)準(zhǔn):WISHBONE是一個開放源代碼的總線標(biāo)準(zhǔn),為SOC設(shè)計提供了一個理想的基本結(jié)構(gòu)。WISHBONE標(biāo)準(zhǔn)的優(yōu)點有以下幾個方面:

· WISHBONE是開放源代碼,所以可以用于各種FPGA或ASIC。

· 有大量的適用于WISHBONE接口開放源碼IP。

· 簡單但靈活的定義使設(shè)計人員能夠?qū)π阅艿膹?fù)雜性進(jìn)行平衡。

由于許多用于控制的可編程邏輯器件的性能要求相對較低,Wishbone總線是與主微處理器作為主器件(master)的共享總線。地址總線有24位,保留的前3位用于產(chǎn)生從器件的選擇信號。

ico8(參考設(shè)計RD1026)和相關(guān)的WISHBONE適配器(RD1043)用于構(gòu)成設(shè)計核的處理器。Mico8具有開放源代碼的優(yōu)點。這是非常重要的,因為設(shè)計人員通常要為嵌入式處理器開發(fā)大量的代碼。LatticeMico8開放源代碼的性質(zhì)意味著它可以在各種FPGA或ASIC中實現(xiàn),保護(hù)了嵌入式代碼的投資。

Mico8有8位的數(shù)據(jù)通道,18位寬的指令和16或32個通用寄存器。外部存儲器是分頁的,前面的8位地址包含在相關(guān)操作碼中。用R15和R16寄存器控制地址總線的其他16位。程序存儲器可以設(shè)置成512和4096之間的深度。在這種情況下,使用18位寬可達(dá)1024深度。程序存儲器存儲在兩個嵌入式RAM塊(EBR.)中,這些可以被初始化為器件啟動時所需的內(nèi)容。請注意,每個MachXO EBR支持9位字節(jié),深度達(dá)1024。Mico8大約使用300個LUT。

通過修改匯編清單可以很容易地生成針對Mico8的新代碼,匯編清單是作為項目文件的一部分。于是通過修改后的代碼可以LatticeMico8工具鏈和生成的相應(yīng)HEX文件。ispLEVER工具可以使用這些HEX文件,合適地初始化EBR用于編程的存儲。Mico8工具鏈也是開放源代碼,可從萊迪思網(wǎng)站下載源代碼以及可執(zhí)行文件。

其他的EBR存儲器連接到Wishbone總線。這個EBR配置成1024深度 8位字節(jié)。針對通過RS232接口的Mico8顯示的各種菜單,存儲空間是用來共享數(shù)據(jù)。

SPI接口利用了萊迪思的SPI WISHBONE控制器參考設(shè)計(RD1044)的修改版本。 SPI接口連接外部2兆位的SPI閃存至Wishbone總線。如果需要的話,SPI WISHBONE控制器可以用來控制多達(dá)8個從器件(slave)。盡管在這種情況下使用了8位寄存器,接收和發(fā)送寄存器可配置為1到32位長度,。寄存器是雙緩沖的,當(dāng)微處理器服務(wù)響應(yīng)中斷請求以清除其他緩沖區(qū)時,允許接收或發(fā)送數(shù)據(jù)。這個參考設(shè)計大約使用了113個LUT。這個I2C接口使用了Wishbone總線接口的萊迪思的I2C主器件(master)參考設(shè)計(RD1046)。這個設(shè)計支持7位或10位尋址模式和一個8位接收/發(fā)送緩沖器。I2C參考設(shè)計大約使用了234個LUT。

UART的設(shè)計采用了Lattice WISHBONE UART參考設(shè)計(RD1042.)。這個設(shè)計用類似常用的獨立NS16450 UART功能實現(xiàn)了一個靈活的UART。設(shè)計占用大約291個LUT的資源。 SRAM接口相對比較簡單,是針對這個項目的代碼。這是一個簡單的WISHBONE外設(shè)的很好的例子。

整合所有的一切

MachXO迷你開發(fā)板的目標(biāo)是為了加快小的、非易失FPGA設(shè)計的開發(fā)速度。為了實現(xiàn)這一點,所有在本文中討論的關(guān)于系統(tǒng)芯片設(shè)計的信息可作為一個軟件包從萊迪思網(wǎng)站上下載。而且,除了文件和源文件,針對所討論的SoC設(shè)計,還提供了一個完整的ispLEVER項目,以及TransFR和使用睡眠模式以減少功耗的演示。提供的信息包括項目文件和所有必要的優(yōu)先選擇和約束,以便在第一時間編譯設(shè)計。

因此,如果要對你系統(tǒng)中的PLD控制設(shè)計進(jìn)行全面的修改,請仔細(xì)看看這個開發(fā)系統(tǒng)和預(yù)測試的設(shè)計。它可以為你的下一個設(shè)計節(jié)省幾周的時間。

責(zé)任編輯:gt

-

處理器

+關(guān)注

關(guān)注

68文章

19349瀏覽量

230304 -

FPGA

+關(guān)注

關(guān)注

1630文章

21760瀏覽量

604382 -

PLD

+關(guān)注

關(guān)注

6文章

224瀏覽量

59433

發(fā)布評論請先 登錄

相關(guān)推薦

Altium推出智能FPGA開發(fā)板NanoBoard 300

Lattice_MachXO系列FPGA開發(fā)板電路原理圖

fpga開發(fā)板用途,fpga開發(fā)板價格

介紹MachXO迷你開發(fā)套件的特點與應(yīng)用

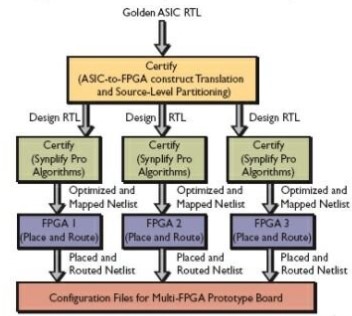

采用FPGA的原型開發(fā)板進(jìn)行ASIC驗證與開發(fā)設(shè)計

ESP32迷你開發(fā)板設(shè)計開源分享

制作一個基于ATtiny13的迷你開發(fā)板

上位機和FPGA開發(fā)板--串口通信實驗

MachXO迷你開發(fā)板加快了FPGA設(shè)計的開發(fā)速度

MachXO迷你開發(fā)板加快了FPGA設(shè)計的開發(fā)速度

評論