引 言

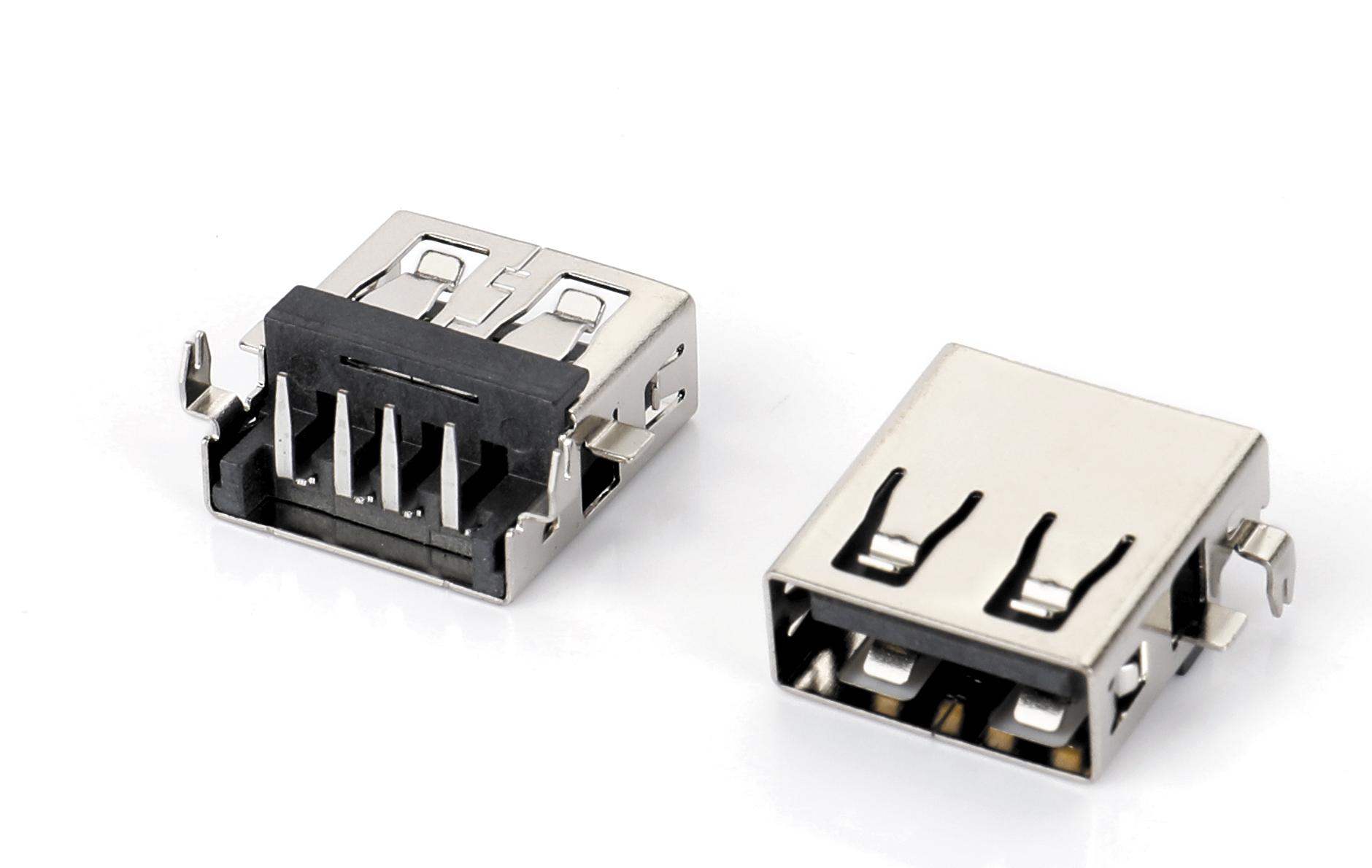

USB(Universal Serial Bus)是一種通用串行總線,主要用于PC與外圍USB設(shè)備的互聯(lián)。近年來,USB接口以其快速、即插即用、使用安裝方便等優(yōu)點(diǎn)逐漸成為現(xiàn)代數(shù)據(jù)傳輸?shù)陌l(fā)展趨勢。目前,國內(nèi)外采用USBl.1和USB2.O兩種規(guī)范。USBl.1主要用于低速傳輸要求的場合,支持1.5Mb/s和12Mb/s兩種傳輸速率;而USB2.O規(guī)范則提供高達(dá)480Mb/s的傳輸速率。盡管如此,在某些對(duì)數(shù)據(jù)傳輸速度要求很高的系統(tǒng)中,外圍設(shè)備與USB接口之間在速度上仍存在著不可忽視的傳輸瓶頸。

Cypress公司生產(chǎn)的USB2.0控制器CY7C68013提供了一種獨(dú)特的接口方式,即通用可編程接口(GPIF)方式。它與傳統(tǒng)接口方式的主要區(qū)別有兩點(diǎn):①在數(shù)據(jù)傳輸過程中不需要CPU干涉,使得傳輸速率明顯提高,從而可以充分利用USB2.0的傳輸帶寬;②由軟件設(shè)置讀/寫控制,其控制方式類似于狀態(tài)機(jī),提高了傳輸穩(wěn)定性。因此,本文介紹的基于USB2.0控制器CY7C68013的GPIF接口設(shè)計(jì),就是充分利用了該芯片這一獨(dú)特的數(shù)據(jù)傳輸接口方式,有效地解決了在傳統(tǒng)接口方式下USB2.0設(shè)備數(shù)據(jù)傳輸速度的局限性,大大提高了數(shù)據(jù)的傳輸速率。

1 、CY7C68013簡介

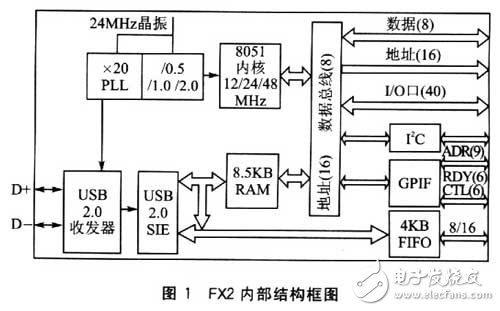

CY7C68013是Cypress公司的EZ-USB FX2系列芯片。EZ-USB FX2是一款集成USB2.0收發(fā)器的微控制器,內(nèi)部結(jié)構(gòu)如圖l所示。該系列芯片集成了USB2.O收發(fā)器、串行接口引擎(SIE)、帶8.5KB片上RAM的增強(qiáng)型高速8051單片機(jī)、4KB FIFO存儲(chǔ)器以及通用可編程接口等模塊.提供了全面集成的USB解決方案,無需外加芯片即可實(shí)現(xiàn)高速USB傳輸。FX2系列芯片最主要的特點(diǎn)是可以通過USB2.0的通用可編程接口為特定的應(yīng)用接口編程。另外,CY7C68013的GPIF引擎具有自動(dòng)傳輸數(shù)據(jù)結(jié)構(gòu)的特性,這種特性使得以主/從端點(diǎn)FIFO(B/16位數(shù)據(jù)總線)為ATA、UTOPIA、EPP、PCMCIA、DSP等的外圍設(shè)備,可以與主機(jī)通過CY7C68013無縫、高速地傳輸數(shù)據(jù)。另外,CY7C68013內(nèi)部集成的USB2.O的SIF能完成大部分USB2.O協(xié)議的處理工作,從而減少了用戶對(duì)繁雜的USB協(xié)議的處理。

2、 硬件設(shè)計(jì)及原理

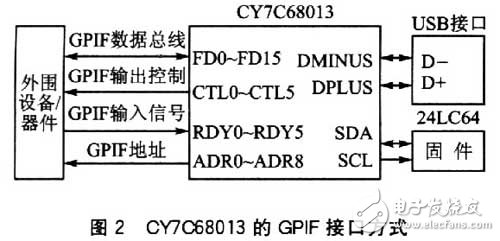

在GPIF接口方式設(shè)計(jì)中,GPIF作為CY7C68013的端點(diǎn)FIFO的內(nèi)部控制器,在這種方式下,CPU不會(huì)干涉數(shù)據(jù)的傳輸。CY7C68013的GPIF接口方式如圖2所示。

CY7C68013專門為GPIF提供了接口信號(hào)(包括16位數(shù)據(jù)線、輸出控制信號(hào)CTL、輸入控制信號(hào)RDY以及地址線ADR),這些信號(hào)負(fù)責(zé)完成USB接口芯片與外圍設(shè)備或器件(如FPGA、DSP等)的數(shù)據(jù)讀/寫控制和傳輸。以下為GPIF方式下的主要端口功能。

FDO~FDl5(輸入/輸出):USB主機(jī)通過CY7C68013與外部設(shè)備進(jìn)行數(shù)據(jù)傳輸?shù)臄?shù)據(jù)線,可以用8位或16位數(shù)據(jù)線。

CTLO~CTL5(輸出):CY7C68013對(duì)外部設(shè)備進(jìn)行控制的信號(hào)線。

RDY0~RDY5(輸入):CY7C68013對(duì)外部設(shè)備的狀態(tài)進(jìn)行檢測的信號(hào)線。

SDA(雙向)、SCL(輸出):E2PROM的數(shù)據(jù)及時(shí)鐘信號(hào)線。

ADR0~ADR8(輸出);GPIF為外部設(shè)備提供的地址線。

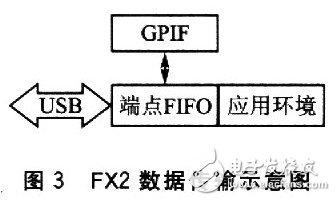

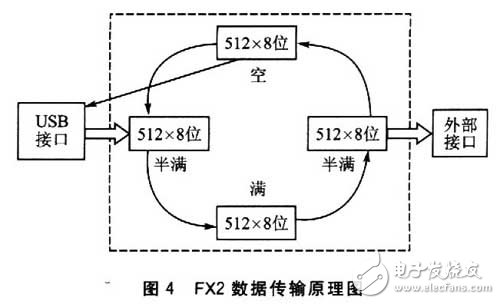

在本設(shè)計(jì)中,除了重點(diǎn)利用通用可編程接口來實(shí)現(xiàn)無縫、高速的傳輸數(shù)據(jù)外,還采用了EZ-USBFX2提供的一種獨(dú)特架構(gòu),即“量子FIFO(Quantum FIFO)”處理架構(gòu)。它能較好地解決帶寬問題,圖3為其數(shù)據(jù)傳輸示意圖。當(dāng)USB執(zhí)行OUT時(shí),EP2端點(diǎn)被設(shè)置為512字節(jié)四重FIFO(在USB端和外部接口端,都不知道有四重FIFO),圖4為其數(shù)據(jù)傳輸原理圖。在USB端看來,只要有1個(gè)FIFO為“半滿”,那么就可以繼續(xù)發(fā)送數(shù)據(jù)。

當(dāng)前操作的FIFO寫“滿”時(shí),F(xiàn)X2自動(dòng)將其轉(zhuǎn)換到外部接口端,排除等候讀取;并將USB接口隊(duì)列中下一個(gè)為“空”的FIFO轉(zhuǎn)移到USB接口上,供其繼續(xù)寫數(shù)據(jù)。同時(shí),在外部接口端看來,只要有1個(gè)FIFO為“半滿”,就可以繼續(xù)讀取數(shù)據(jù)。當(dāng)前操作的FIFO讀“空”時(shí),F(xiàn)X2自動(dòng)將其轉(zhuǎn)換到USB接口端,排除等候?qū)懭耄徊⑼獠拷涌陉?duì)列中下一個(gè)為“滿”的FIFO轉(zhuǎn)移到外部接口上,供其繼續(xù)讀取數(shù)據(jù)。

3、 軟件設(shè)計(jì)及實(shí)現(xiàn)

本設(shè)計(jì)的軟件設(shè)計(jì)包括:固件程序、驅(qū)動(dòng)程序和應(yīng)用程序設(shè)計(jì)。其中,固件程序是整個(gè)程序設(shè)計(jì)的核心,它在設(shè)備CPU中運(yùn)行。GPIF就是在固件中實(shí)現(xiàn)的,因此,只有在該程序運(yùn)行時(shí),外設(shè)才能稱之為具有給定功能的外部設(shè)備。

責(zé)任編輯:gt

-

控制器

+關(guān)注

關(guān)注

112文章

16418瀏覽量

178791 -

usb

+關(guān)注

關(guān)注

60文章

7966瀏覽量

265296 -

協(xié)議

+關(guān)注

關(guān)注

2文章

606瀏覽量

39286

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

USB2.0模塊的設(shè)計(jì)技術(shù)

基于層次模型的USB2.0接口芯片IP核固件的設(shè)計(jì)

基于USB2.0總線的TMS320VC5402 HPI自舉實(shí)現(xiàn)

怎么實(shí)現(xiàn)USB2.0微控制器CY7C68013的GPIF接口設(shè)計(jì)?

基于USB2.0 的CMOS圖像采集系統(tǒng)的實(shí)現(xiàn)

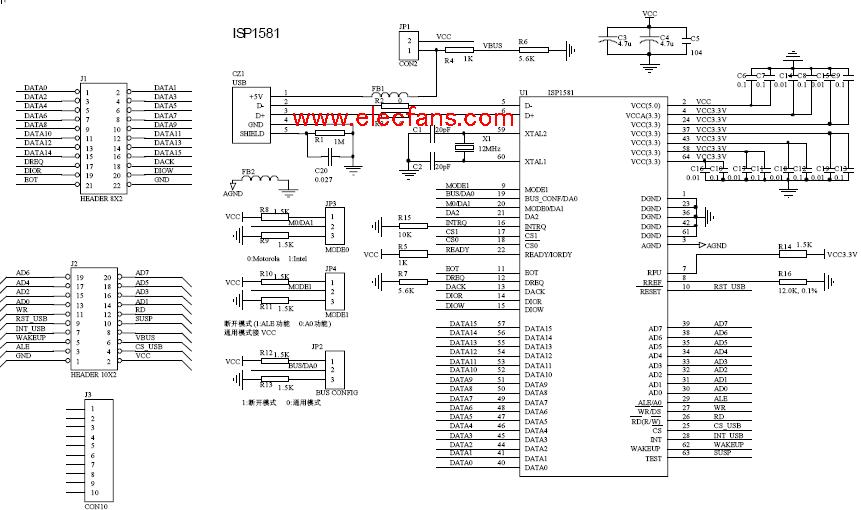

基于USB2.0的接口芯片ISP1581的應(yīng)用與設(shè)計(jì)

USB2.0 接口控制演示實(shí)驗(yàn)

USB2.0接口芯片CY7C68013的固件程序開發(fā)

USB2.0接口芯片IP核固件設(shè)計(jì)

基于USB2.0芯片CY7C68013的高速數(shù)據(jù)通信接口設(shè)計(jì)

基于層次模型的USB2.0接口芯片IP核固件的設(shè)計(jì)

數(shù)字合成掃頻儀USB2.0接口設(shè)計(jì)

基于FPGA NANO2開發(fā)板實(shí)現(xiàn)USB2.0接口通信的設(shè)計(jì)方案

USB2.0微控制器CY7C68013的GPIF接口設(shè)計(jì)資料下載

USB2.0接口選型時(shí)要注意的問題

基于USB2.0實(shí)現(xiàn)GPIF接口的固件、驅(qū)動(dòng)和應(yīng)用程序的設(shè)計(jì)

基于USB2.0實(shí)現(xiàn)GPIF接口的固件、驅(qū)動(dòng)和應(yīng)用程序的設(shè)計(jì)

評(píng)論